### Datasheet

DS000556

### XYZ True Color Sensor with I<sup>2</sup>C Interface

v3-01 • 2018-Feb-07

## **Content Guide**

| 1                                                    | General Description3               |

|------------------------------------------------------|------------------------------------|

| 1.1<br>1.2<br>1.3                                    | Key Benefits & Features            |

| 2                                                    | Ordering Information6              |

| 3                                                    | Pin Assignment7                    |

| 3.1<br>3.2                                           | Pin Diagram7<br>Pin Description    |

| 4                                                    | Absolute Maximum Ratings9          |

| 5                                                    | Electrical Characteristics         |

| 6                                                    | Typical Optical Characteristics 13 |

| 7                                                    | Functional Description14           |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8 | Operational States                 |

| 7.9<br>7.10<br>7.11<br>7.12                          | Energy Saving Options              |

| 7.13<br>7.14<br>7.15                                 | Transfer Function                  |

| 7.16<br>7.17<br>7.18<br>7.19                         | Mode                               |

| 7.20<br>7.21                                         | I <sup>2</sup> C Addressable Register Space<br>I <sup>2</sup> C General Procedure to start with the<br>AS73211                                                                                                                     |                                       |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 8                                                    | Register Description                                                                                                                                                                                                               |                                       |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8 | Register Overview<br>Operational State Register – OSR<br>API Generation Register – AGEN<br>Configuration Register - CREG1, CREG2<br>and CREG3<br>Register – BREAK<br>Register – EDGES<br>Register – OPTREG<br>Output Register Bank | 44<br>44<br>2<br>47<br>51<br>51<br>51 |

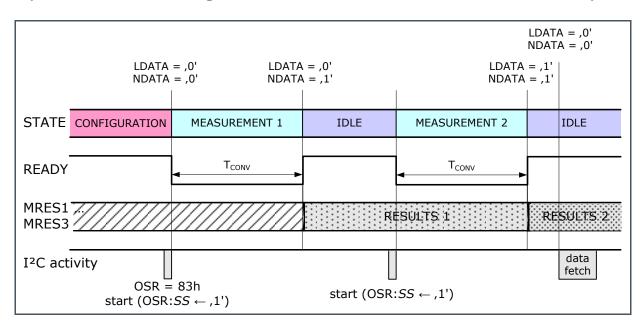

| 9                                                    | Application Information                                                                                                                                                                                                            | 56                                    |

| 9.1<br>9.2<br>9.3                                    | Schematic<br>External Components<br>PCB Layout                                                                                                                                                                                     | 56                                    |

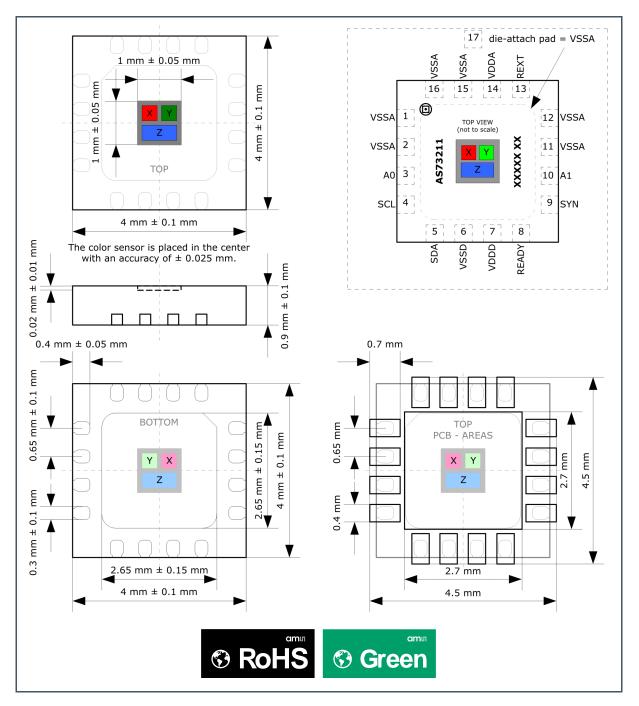

| 10                                                   | Package Drawings                                                                                                                                                                                                                   | 58                                    |

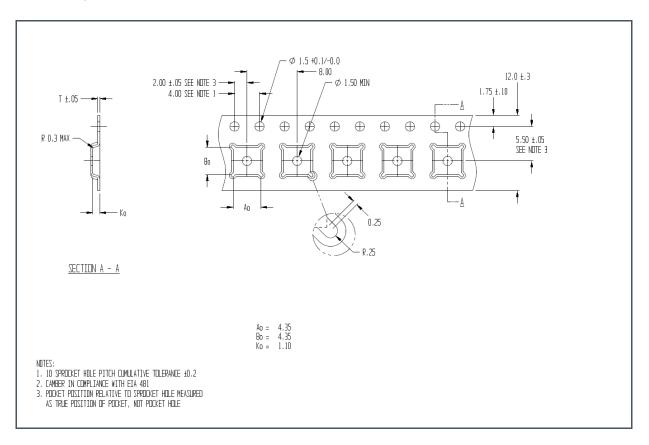

| 11                                                   | Tape & Reel Information                                                                                                                                                                                                            | 59                                    |

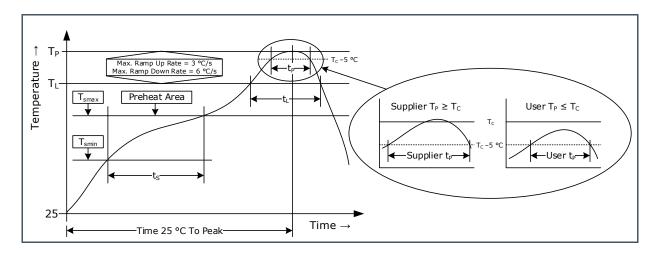

| 12                                                   | Soldering & Storage Information                                                                                                                                                                                                    | n 60                                  |

| 13                                                   | Application Notes                                                                                                                                                                                                                  | 61                                    |

| 13.1<br>13.2<br>13.3<br>13.4<br>13.5                 | Narrowband Luminous Sources<br>Angle of Incidence<br>Effects of Temperature<br>Notes for Manufacturing<br>Sensor Calibration                                                                                                       | 61<br>61<br>61                        |

| 14                                                   | Revision Information                                                                                                                                                                                                               | 64                                    |

| 15                                                   | Legal Information                                                                                                                                                                                                                  | 65                                    |

## **1** General Description

The AS73211 is a low power, low noise integrated color sensor. Three channels convert light signals via photodiodes to a digital result and realize a continuous or triggered measurement. In front of the three photodiodes there are optical filter mounted for X-, Y- and Z-signals respectively. The irradiance responsivity can be set in a range of 12 steps by a factor of two for each step. The conversion time is internally controlled over a wide range of 15 steps by a factor of two for each step. With the input pin (SYN) the conversion time can be externally controlled to adapt the measurement to the given environment and time base.

With its irradiance responsivity factor and conversion time the AS73211 supports an overall huge dynamic range up to 3.43E+10 (resolution multiplied by gain range). It achieves an accuracy of up to 24-bit signal resolution (internal via I<sup>2</sup>C and shifter 16 bit) with an irradiance responsivity per count down to 0.5pW/cm<sup>2</sup>.

$$Dynamic Range = \frac{MAX \text{ measureable value } = Max. Full Scale Range}{MIN \text{ measureable value } = Min. Least Significant Bit}$$

For high robustness at high sensitivity, the AS73211 has an inherent ripple rejection of the 50Hz / 60Hz external disturbances. Automatic Power Down (sleep function) between subsequent measurements offers operation with very low current consumption. Further, a synchronized mode and other control modes adjustable by user programming can be used. The supported operating modes of the AS73211 are:

- CMD Mode single measurement and conversion (controlled via I<sup>2</sup>C interface),

- CONT Mode continuous measurement and conversion (periodically recurring measuring cycles) start and stop controlled via I<sup>2</sup>C interface,

- SYN[x] Modes synchronized measurement and conversion:

- [SYNS Mode] synchronization of start via control signal at pin SYN,

- [SYND Mode] synchronization of start and stop of measuring cycles via control signal at pin SYN.

The conversion data is accessed by the I<sup>2</sup>C interface with programmable slave addresses via 16-bit / 400 kHz fast mode. The measurement of the actual conversion time for an external triggered measurement can be performed. The measurement modes will not affect the settings of the irradiance responsivity and conversion time. Further, the converter supports functions like Power Down and Standby, therefore it is suitable for mobile applications. Based on the high flexibility the AS73211 is suitable as an optical converter for three different wave-lengths. The device achieves a high dynamic range in back light applications and in the measurements of integral intensity of pulsed light. That makes the color sensors excellently suited for photometry applications (brightness, color coordinate and/or color temperature), for determining current values for control of spectrally mixed LED light sources or as sensors for display and (back)light calibration and mobile devices for light measurement. The AS73211 contains an integrated temperature sensor for rough compensation of the thermic behavior of light sources. The device is available in a small SMD package.

### 1.1 Key Benefits & Features

The benefits and features of AS73211, XYZ True Color Sensor with I<sup>2</sup>C Interface, are listed below:

Figure 1:

Added Value of Using AS73211

| Benefits                                                      | Features                                                                                       |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Light control measurement based on CIE 1931/DIN 5033          | JENCOLOR <sup>®</sup> interference filter technology                                           |

| Brightness, color coordinate and/or color temperature control | High dynamic range up to 3.43E+10 (16 .24 Bit ADC)                                             |

| Usable under poor lighting conditions                         | High sensitivity up to 2.1M counts/(µW/cm <sup>2</sup> )<br>Smallest LSB 0.5pW/cm <sup>2</sup> |

| Mobile applications                                           | Low power operation, Power on Reset, Power down and standby, small QFN package                 |

| Harsh environmental applications                              | -40°C up to 125°C operation temperature range                                                  |

| Temperature compensation                                      | On-chip temperature sensor                                                                     |

### 1.2 Applications

- LED lighting control management for solid-state lighting applications (SSL)

- Cabin lighting, daylight management / Human and Color Centric Lighting (HCL and CCL)

- Ambient light color detection / correction

- (O)LED display aging compensation and dynamic display color balancing

- Portable light color measurement

- Digital light projection (DLP)

- Printer, Smartphone, PDA, tablet PCs, LCD-TVs, digital picture, frames, digital cameras color enhancement

- Photometry (brightness, color coordinate and/or color temperature)

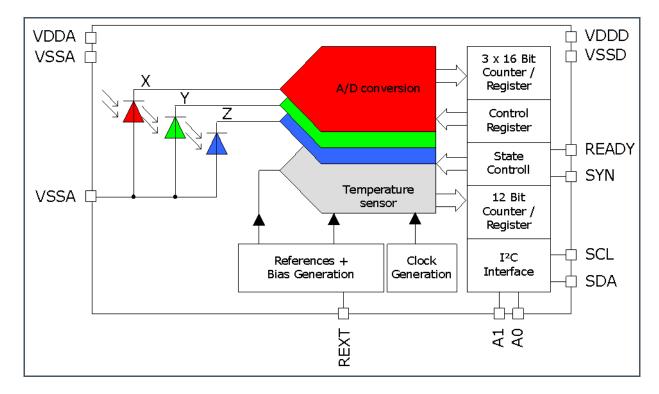

### 1.3 Block Diagram

Figure 2 shows the main components of the AS73211. The photodiodes convert the incoming light to a photo current and with subsequent current-to-digital converter to digital data. An internal reference generator provides all necessary references for the A/D conversion and the photodiodes by using an external resistor  $R_{EXT}$  at pin REXT. The results of the A/D conversion are stored in three 16-bit registers and can be accessed via I<sup>2</sup>C interface. For the externally triggered start or start and stop of the measurement, the input pin SYN can be used. The output READY reflects the status of the conversion. The internal temperature sensor delivers the on-chip temperature, stored as 12-bit value in a 16-bit register, which can be accessed via I<sup>2</sup>C interface, too. The pins A0 and A1 set the I<sup>2</sup>C slave address. Separated analog and digital power supply and ground pins reduces noise coupling.

Figure 2: Functional Blocks of AS73211

## 2 Ordering Information

| Ordering Code | Package | Marking | Delivery Form | Delivery Quantity |

|---------------|---------|---------|---------------|-------------------|

| AS73211-AQFM  | QFN16   | AS73211 | Tape & Reel   | 500pcs/reel       |

| AS73211-AQFT  | QFN16   | AS73211 | Tape & Reel   | 3000pcs/reel      |

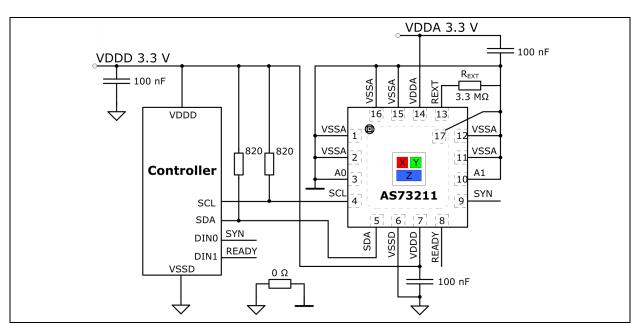

## 3 Pin Assignment

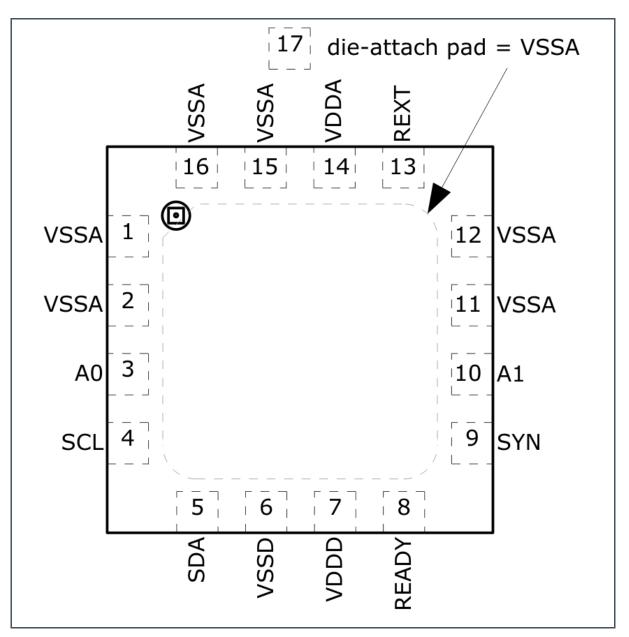

### 3.1 Pin Diagram

Figure 3:

Pin Diagram of AS73211 in QFN16 Package (top view)

### 3.2 Pin Description

#### Figure 4:

Pin Description of AS73211

| Pin<br>Number | Pin Name | Pin Type <sup>(1)</sup> | Description                                                                                 |

|---------------|----------|-------------------------|---------------------------------------------------------------------------------------------|

| 1 - 2         | VSSA     | Ρ                       | Analog ground                                                                               |

| 3             | A0       | DI                      | Variable I <sup>2</sup> C slave address bit 0                                               |

| 4             | SCL      | DI                      | I <sup>2</sup> C clock input                                                                |

| 5             | SDA      | D_I/O_OD                | I <sup>2</sup> C data input / output; open drain output stage                               |

| 6             | VSSD     | Р                       | Digital ground                                                                              |

| 7             | VDDD     | Р                       | Digital power supply                                                                        |

| 8             | READY    | DO                      | Conversion status; configurable as push pull or open drain output stage (default push pull) |

| 9             | SYN      | DI                      | Input for external controlled conversion                                                    |

| 10            | A1       | DI                      | Variable I <sup>2</sup> C slave address bit 1                                               |

| 11 – 12       | VSSA     | Р                       | Analog ground                                                                               |

| 13            | REXT     | A_I/O                   | External reference resistor                                                                 |

| 14            | VDDA     | Р                       | Analog power supply                                                                         |

| 15 – 17       | VSSA     | Р                       | Analog ground                                                                               |

(1) Explanation of abbreviations:

DI Digital input

DO Digital output

D\_I/O\_OD Digital input / output open drain

P Power pin

A\_I/O Analog

## 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 5:

Absolute Maximum Ratings of AS73211

| Symbol             | Parameter                              | Min  | Max                  | Unit | Comments                           |

|--------------------|----------------------------------------|------|----------------------|------|------------------------------------|

| Electrical Pa      | rameters                               |      |                      |      |                                    |

| V <sub>DD</sub>    | Power Supply Voltage                   | -0.5 | 5.0                  | V    | VDDA and VDDD                      |

| $DIFF_{VDD}$       | Supply Voltage Difference              | -0.3 | 0.3                  | V    | VDDD-VDDA                          |

|                    | Input and Output Voltages              | -0.5 | V <sub>DD</sub> +0.5 | V    | A0, A1, SCL, SDA, SYN,<br>READY    |

| Electrostatio      | Discharge                              |      |                      |      |                                    |

| ESD <sub>HBM</sub> | Electrostatic Discharge HBM            | ±    | 500                  | V    | JS-001-2014                        |

| ESD <sub>CDM</sub> | Electrostatic Discharge CDM            | ±    | 500                  | V    | JEDEC JESD22-C101F Oct 2013        |

| Temperature        | e Ranges and Storage Conditions        |      |                      |      |                                    |

| T <sub>A</sub>     | Operating Ambient Temperature          | -40  | 125                  | °C   |                                    |

| T <sub>STRG</sub>  | Storage Temperature Range              | -55  | 125                  | °C   |                                    |

| T <sub>BODY</sub>  | Package Body Temperature               |      | 260                  | °C   | IPC/JEDEC J-STD-020 <sup>(1)</sup> |

| RH <sub>NC</sub>   | Relative Humidity (non-<br>condensing) | 5    | 85                   | %    |                                    |

| MSL                | Moisture Sensitivity Level             |      | 3                    |      | Maximum floor life time of 168h    |

(1) The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices." The lead finish for Pbfree leaded packages is "Matte Tin" (100 % Sn)

## **5 Electrical Characteristics**

All limits are guaranteed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods. All voltages with respect to ground (GND). Device parameter are guaranteed at  $V_{DD}$ =3.3V and T<sub>A</sub>=25°C unless otherwise noted.

#### Figure 6:

**Electrical Characteristics of AS73211**

| Symbol               | Description                             | Condition                                           | Min   | Тур | Max             | Unit               |

|----------------------|-----------------------------------------|-----------------------------------------------------|-------|-----|-----------------|--------------------|

| T <sub>OP</sub>      | Operating Temperature                   |                                                     | -40   |     | 125             | °C                 |

| V <sub>DD</sub>      | Power Supply Voltage                    | VDDA and VDDD                                       | 2.7   | 3.3 | 3.6             | V                  |

|                      | Supply Voltage Difference               | VDDD-VDDA                                           | -0.3  | 0   | 0.3             | V                  |

| R <sub>EXT</sub>     | External Resistor at Pin REXT           | R <sub>EXT</sub><br>(TC <sub>REXT</sub> ≤ 50ppm/K)  | 3.267 | 3.3 | 3.333           | MΩ                 |

| I <sub>VDD</sub>     | Current Consumption                     | Active mode during measurement                      |       | 1.5 | 2               | mA                 |

| I <sub>VDDSB</sub>   | Standby Current Consumption             | Standby state                                       |       |     | 800             | μA                 |

| IVDDPD               | Power Down Current Consumption          | Power down state                                    |       |     | 1               | μA                 |

| VIH                  | Input High Level                        | A0, A1, SCL, SYN                                    | 0.7   |     |                 | VDDD               |

| VIL                  | Input Low Level                         | A0, A1, SCL, SYN                                    |       |     | 0.3             | VDDD               |

| VOH                  | Output High Level                       | READY<br>IOHL ≤ 3mA                                 | 0.8   |     |                 | VDDD               |

| VO                   |                                         | SDA, READY<br>IOHL ≤ 4mA                            |       |     | 0.4             | V                  |

| VOL                  | Output Low Level                        | SDA, READY<br>IOHL ≤ 4mA                            |       |     | 0.4<br>0.6<br>6 | V                  |

| IOHL                 | Output Drive Strength                   | Concerning to<br>VOH and VOL                        |       | 3   | 6               | mA                 |

| I <sub>ILEAK</sub>   | Input Leakage Current                   | $VSSD \leq VIN \leq VDDD$                           | -10   |     | 10              | μA                 |

| f <sub>CLKMIN</sub>  | Min. Internal Clock Frequency           | CREG3:CCLK = 00b                                    | 0.75  | 1   | 1.3             | MHz                |

| f <sub>CLKMAX</sub>  | Max. Internal Clock Frequency           | CREG3:CCLK = 11b                                    | 6     | 8.2 | 10              | MHz                |

| T <sub>STARTSB</sub> | Startup Time after Standby state        | Until start of first measurement                    |       | 4   | 5               | μs                 |

| T <sub>STARTPD</sub> | Startup Time after Power Down state     | Until start of first measurement                    |       | 1.2 | 2               | ms                 |

| T <sub>SYNDEL</sub>  | SYN Trigger Delay                       | From falling SYN-edge<br>to start of<br>measurement |       |     | 3               | 1/f <sub>CLK</sub> |

| T <sub>SYN</sub>     | SYN Negative or Positive Pulse<br>Width | SYN recognized as start or end pulse of measurement | 3     |     |                 | 1/f <sub>CLK</sub> |

| T_abs_err            | Temperature Absolute Error              |                                                     | -10   |     | 10              | K                  |

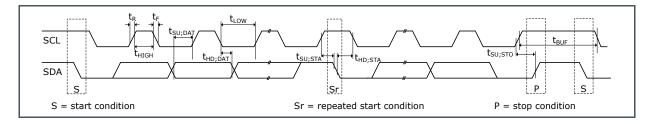

#### Figure 7:

I<sup>2</sup>C Slave Timing Characteristics of AS73211

| Symbol               | Description                                           | Condition                                                      | Min  | Тур | Max | Unit |

|----------------------|-------------------------------------------------------|----------------------------------------------------------------|------|-----|-----|------|

| f <sub>SCL</sub>     | I <sup>2</sup> C Clock Frequency at SCL               | R <sub>PULLUP</sub> ≥ 820Ω<br>CL <sub>(SCL, SDA)</sub> ≤ 400pF |      |     | 400 | kHz  |

| t <sub>HIGH</sub>    | SCL High Pulse Width                                  |                                                                | 0.6  |     |     | μs   |

| t <sub>LOW</sub>     | SCL Low Pulse Width                                   |                                                                | 1.3  |     |     | μs   |

| t <sub>R</sub>       | SCL and SDA Rise Time                                 |                                                                |      |     | 0.3 | μs   |

| t <sub>F</sub>       | SCL and SDA Fall Time                                 |                                                                |      |     | 0.3 | μs   |

| t <sub>HD;STA</sub>  | Hold Time Start Condition                             |                                                                | 0.6  |     |     | μs   |

| t <sub>su;sda</sub>  | Setup Time Start Condition                            |                                                                | 0.6  |     |     | μs   |

| t <sub>HD;DATM</sub> | SDA Data Hold Time (Master)                           | Data transfer from master to slave                             | 0.02 |     |     | μs   |

| t <sub>HD;DATS</sub> | SDA Data Hold Time (Slave)                            | Data transfer from slave to master                             | 0.3  |     | 0.9 | μs   |

| t <sub>su;dat</sub>  | Data Setup Time                                       |                                                                | 0.1  |     |     | μs   |

| t <sub>su;sto</sub>  | Setup Time Stop Condition                             |                                                                | 0.6  |     |     | μs   |

| t <sub>BUF</sub>     | Bus Free Time between a Stop<br>and a Start Condition |                                                                | 1.3  |     |     | μs   |

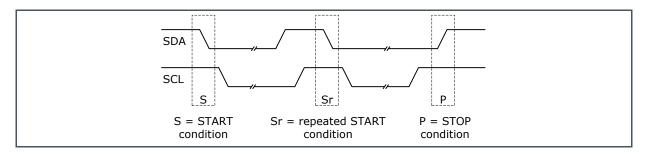

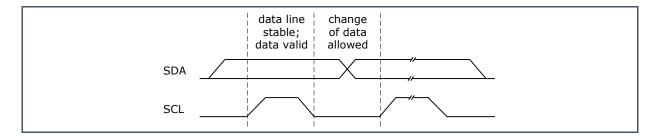

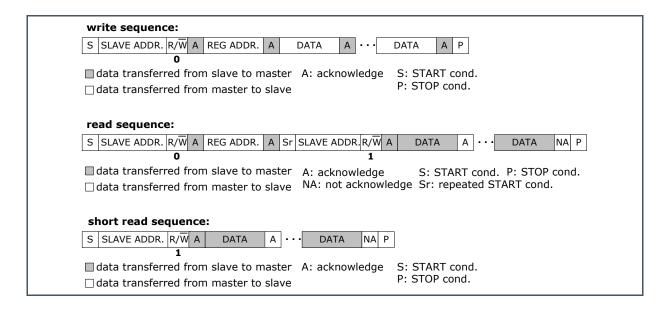

#### Figure 8:

I<sup>2</sup>C Slave Timing Diagram

#### Figure 9:

ADC Specification of AS73211

| Symbol            | Description                                                                                                 | Condition                               | Min   | Тур | Max   | Unit   |    |

|-------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|-----|-------|--------|----|

| RES               | ADC Resolution                                                                                              |                                         | 10    |     | 24    | bit    |    |

| _                 | ES ADC Resolution CONV Conversion Time T <sub>CONV</sub> Conversion Time Tolerance IL Integral Nonlinearity | CREG3:CC<br>f <sub>CLKMIN</sub>         |       | 1   |       | 16384  | ms |

| T <sub>CONV</sub> | Conversion Time                                                                                             | CREG3:CCLK = 11b<br>f <sub>CLKMAX</sub> | 0.125 |     | 24    | ms     |    |

| $\Delta T_{CONV}$ | Conversion Time Tolerance                                                                                   | Related to f <sub>CLK</sub>             | -25   |     | 25    | %      |    |

| INL               | Integral Nonlinearity                                                                                       |                                         | -0.02 |     | 0.02  | %      |    |

| DNL               | Differential Nonlinearity                                                                                   | No missing codes                        | -0.5  |     | 0.5   | LSB    |    |

| D <sub>FSR</sub>  | Full Scale ADC Code                                                                                         | Per channel                             | 1024  |     | 65535 | counts |    |

| Symbol            | Description              | Condition                                                                                                        | Min | Тур  | Max | Unit   |

|-------------------|--------------------------|------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| D <sub>DARK</sub> | Dark ADC Count Value     | $E_e = 0;$<br>GAIN = 2048x<br>T <sub>CONV</sub> = 64ms @<br>f <sub>CLKMIN</sub> ;                                |     |      | 8   | counts |

| ENOB              | Effective Number of Bits | $\begin{array}{l} \text{GAIN} = 64x \\ \text{T}_{\text{CONV}} = 64ms @ \\ \text{f}_{\text{CLKMIN}}; \end{array}$ |     | 15.4 |     | bit    |

Figure 10:

**Optical Characteristics of AS73211**

| Symbol                                                                   | Description                                                            | Condition                    | Min | Тур    | Max   | Unit                |  |  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------|-----|--------|-------|---------------------|--|--|

|                                                                          |                                                                        | X channel<br>λ = 600nm       |     | 4730   |       |                     |  |  |

| Re <sub>GAIN2048</sub><br>Re <sub>GAIN1</sub><br>FSR <sub>GAIN2048</sub> | Irradiance Responsivity for<br>CREG1:GAIN = 2048x                      | Y channel<br>λ = 555nm       |     | 4392   |       | counts/<br>(µW/cm²) |  |  |

|                                                                          |                                                                        | Z channel<br>λ = 445nm       |     | 8179   |       | _                   |  |  |

|                                                                          |                                                                        | X channel<br>λ = 600nm       |     | 2.309  |       |                     |  |  |

| Re <sub>GAIN1</sub>                                                      | Irradiance Responsivity for<br>CREG1:GAIN = 1x                         | Y channel<br>λ = 555nm       |     | 2.145  |       | counts/<br>(µW/cm²) |  |  |

|                                                                          |                                                                        | Z channel<br>λ = 445nm       |     | 3.994  |       |                     |  |  |

|                                                                          | Full Scale Range of detectable<br>Irradiance for<br>CREG1:GAIN = 2048x | X channel<br>λ = 600nm       |     | 13.854 |       |                     |  |  |

| FSR <sub>GAIN2048</sub>                                                  |                                                                        | Y channel<br>λ = 555nm       |     | 14.919 |       | µW/cm²              |  |  |

|                                                                          |                                                                        | Z channel<br>λ = 445nm       |     | 8.012  | 8.012 |                     |  |  |

| FSR <sub>GAIN1</sub>                                                     |                                                                        | X channel<br>λ = 600nm       |     | 28372  |       |                     |  |  |

|                                                                          | Full Scale Range of detectable<br>Irradiance for<br>CREG1:GAIN = 1x    | Y channel<br>λ = 555nm       |     | 30554  |       | μW/cm²              |  |  |

|                                                                          | CREGT.GAIN = 1X                                                        | Z channel $\lambda = 445$ nm |     | 16408  |       |                     |  |  |

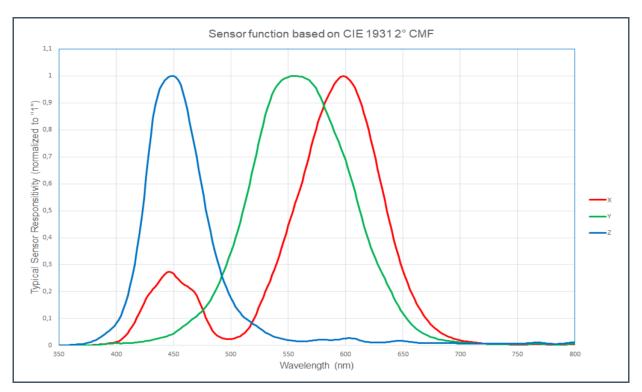

## **6** Typical Optical Characteristics

The filter response curves based on the CIE 1931 standard are shown in the figure below.

#### Figure 11:

Typical Spectral Sensitivity of XYZ True Color Sensor AS73211

Typical characteristic sensitivity. Spectral tolerance filter curve Δλ(λ) typ. <±1%\*λ determined by the deviation between the filter curve's centroid wavelength and the CIE 1931 2° Standard Observer centroid wavelength.</li>

See chapter 13.2 Angle of Incidence

#### Figure 12: Photodiode Array

## **7** Functional Description

Three internal photodiodes with different spectral sensitivity with three A/D converters. The irradiance responsivity Re and the time of conversion TCONV are user defined and determined by registers CREG1:GAIN and CREG1:TIME and should be adapted to the application of interest. At the end of each conversion, the digital equivalents of the filtered input light signal regarding to the sensors area are stored in the output registers (MRES1 ... MRES3). Additionally a temperature sensor works in parallel to the three optical channels, delivering the on-chip temperature at the end of conversion. The pin READY remains at low logic level all the time during the conversion. Internal information related to the conversion is available in a status register, too.

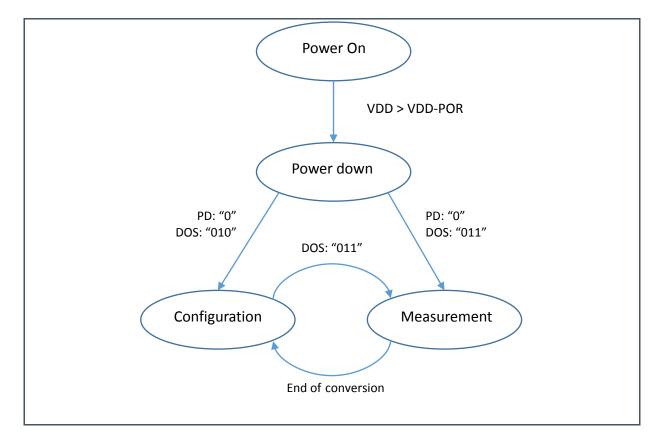

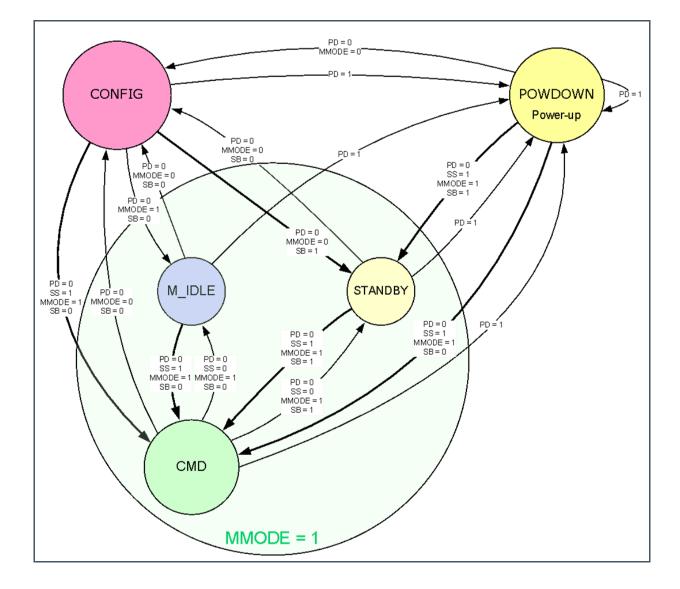

### 7.1 Operational States

The AS73211 operates in two different states "**Configuration**" and "**Measurement**". The three least significant bits of the Operational State Register (OSR) as Device Operational State (DOS) defined the current state. After applying the power supply voltage including power-on reset or after software reset the AS73211 stays in Power Down state. It is ready to be programmed via I<sup>2</sup>C interface. Switching off Power Down (OSR:PD set to ,0') the AS73211 starts up in Configuration state (CONFIG) or in Measurement state (MMODE) according to its DOS programming.

### 7.2 Configuration State

This state enables the access to the configuration registers (CREG1, CREG2, CREG3). Irradiance responsivity  $R_e$  and conversion time  $T_{CONV}$  can be determined by settings of registers CREG1:GAIN and CREG1:TIME as well as the kind of measurement mode can be chosen via register CREG3:MMODE. A measurement is not possible in this state and therefore no access to any measurement result registers.

### 7.3 Measurement State

In this state the light-to-digital conversion can be performed. The access to the output result registers is enabled, but at this time, there is no access possible to the configuration registers. Specific settings for the measuring task should be performed by programming the configuration registers before the measurement is started (see chapter 8.5). The change between Configuration and Measurement state can be performed by programming the DOS value of the operational state register OSR (see Figure 45). A change from Measurement state to Configuration state takes place immediately. Any active measurement is stopped and all output result registers and the status register are reset as well.

#### Figure 13: Simplified State Diagram

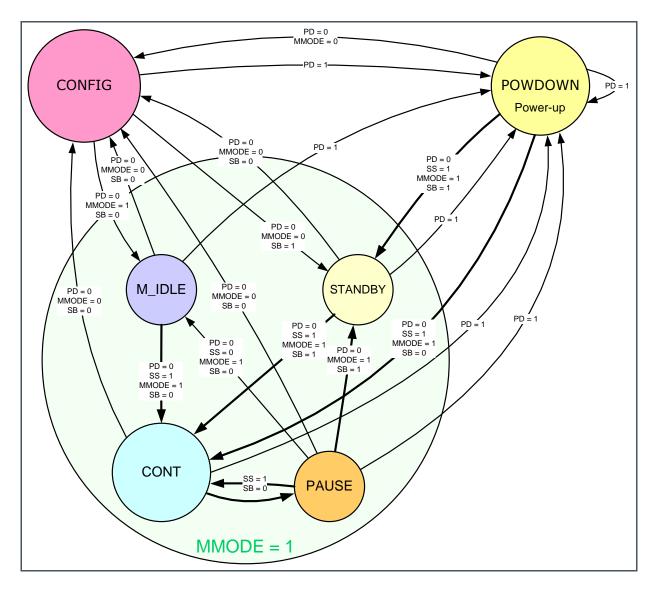

### 7.4 Measurement Modes

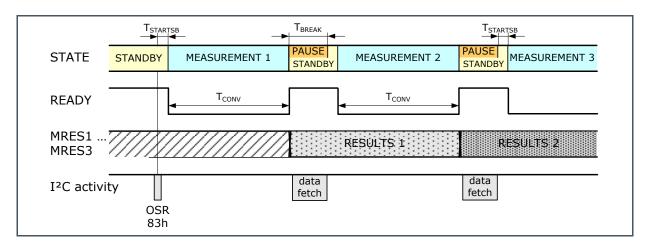

There are four different modes available to perform the measurement. The register CREG3:MMODE (see Figure 50) defines the measurement mode that is performed by the device. It is generally recommended not to communicate via I<sup>2</sup>C during the conversion. Use pause times between two conversion cycles for data transfer via I<sup>2</sup>C interface. To support such a behavior a variable pause time TBREAK is implemented (register BREAK in Figure 52), which delays the start of the next conversion cycle in the measurement modes CONT, SYNS and SYND. I<sup>2</sup>C commands sent to the AS73211 always take effect after the complete I<sup>2</sup>C write cycle with an I<sup>2</sup>C Stop condition at the end.

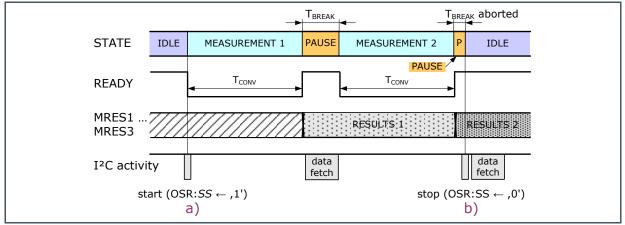

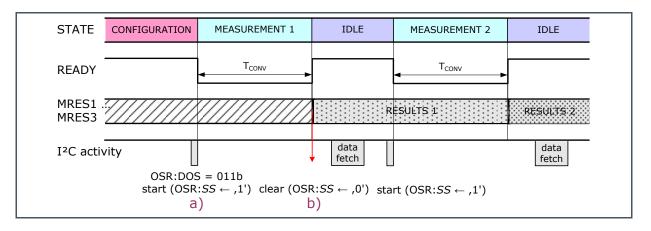

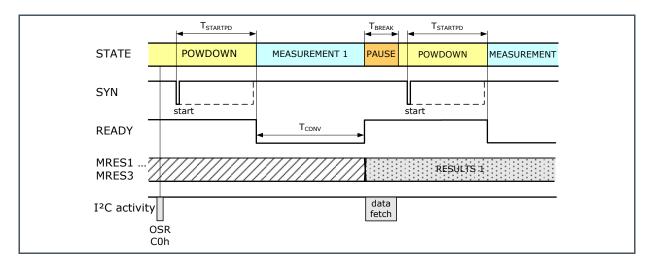

### 7.5 Continuous Measurement Mode – CONT

The A/D conversion is sequentially performed. The first conversion starts by setting the bit OSR:SS to ,1'. If the Power Down or Standby option is switched on, the device deactivates it and initializes the continuous measurement. The measurement can only be stopped by resetting the bit OSR:SS bit.

#### Figure 14: State Machine CONT Mode

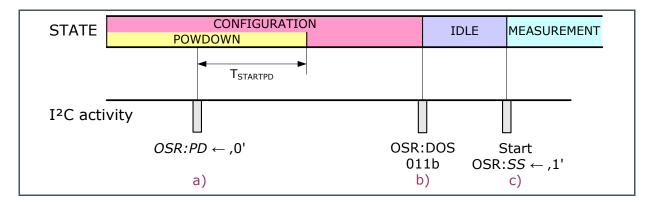

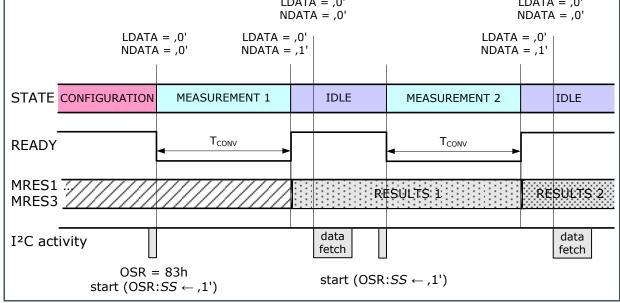

The conversion time (TCONV) is determined by the content of the register CREG1:TIME (see Figure 48). The rising edge of READY signalizes the end of each conversion and its available valid results Figure 48 shows the principle sequence for a measurement start in CONT mode, while waiting in Measurement state shows IDLE:

- 1. OSR programming: 83h, start of continuous measurement via OSR:SS = ,1', while device is already in measurement mode (OSR:DOS = 011b),

- 2. OSR programming: 03h, abortion of continuous measurement via OSR:SS = ,0<sup>°</sup> here while pause time TBREAK is already activated to get the last measurement results.

It is recommended to read the measurement results during the break between two consecutive conversions. This pause time TBREAK can be configured in steps of 8µs up to 2040µs long (see Figure 52). Please note that the break time should be long enough to prevent overlapping of data fetch activities with the measurement for avoiding measurement disturbances, which could cause distortions of the measurement results

#### Figure 15:

### 7.6 Command Measurement Mode – CMD

The CMD mode enables a start of a single conversion. Each conversion starts by setting the bit OSR:SS to ,1'. The conversion time (TCONV) is determined by the content of the register CREG1:TIME (see Figure 48). Figure 16 shows the first measurement starting from the Configuration state by setting the bits of the Device Operational State (OSR:DOS) and Start/Stop (OSR:SS) at the same time with OSR = 83h. For the next measurement start OSR = 80h is set (only bit OSR:SS, OSR:DOS = 000b corresponds to NOP – no operation, see also Figure 45.

The rising edge of READY signalizes the end of conversion and its valid output data can be read via the I<sup>2</sup>C interface (data fetch).

#### Figure 16: State Machine CMD Mode

Figure 17 shows the principle sequence for a measurement start in CMD mode coming from Configuration state and waiting in Measurement state between the measurements is shown as IDLE:

- 1. OSR programming: 83h, change to Measurement state, start of measurement via OSR:SS = ,1',

- 2. "Automatically" OSR programming: 03h, to reset bit OSR:SS to ,0' at the end of conversion.

Figure 17:

Principle Sequence for a Measurement Start in CMD Mode Coming From Configuration State

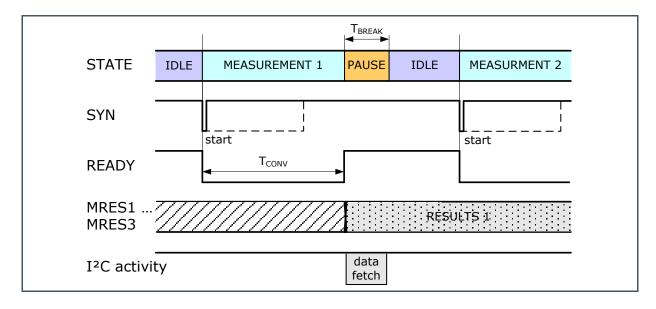

### 7.7 Synchronous Measurement Mode – SYNS

In this measurement mode, the input pin SYN acts as a trigger event for the start of A/D conversion. The falling edge at pin SYN starts the measurement. The conversion time (TCONV) is determined by the content of the register CREG1:TIME (see Figure 48). The pin READY signalizes the progress of conversion (see Figure 18) and its rising edge shows the end of conversion and its available valid results. The data fetch should be performed between the rising edge of signal READY and the next falling edge of signal SYN in order to allow distortion free measurement. SYN pulses during the programmed pause time TBREAK are ignored to avoid a start of the measurement during a running data fetch (see also Figure 52). The bit OSR:SS also takes effect in the SYNS mode, because the start of the measurement is only possible with OSR:SS = ,1<sup>4</sup>.

Figure 18 shows the principle sequence for a measurement start in SYNS mode, OSR:DOS = 011b and OSR:SS = ,1' already set and waiting in Measurement state is shown as IDLE.

#### Figure 18:

Principle Sequence for a Measurement Start in SYNS Mode, OSR:DOS = 011b and OSR:SS = ,1'

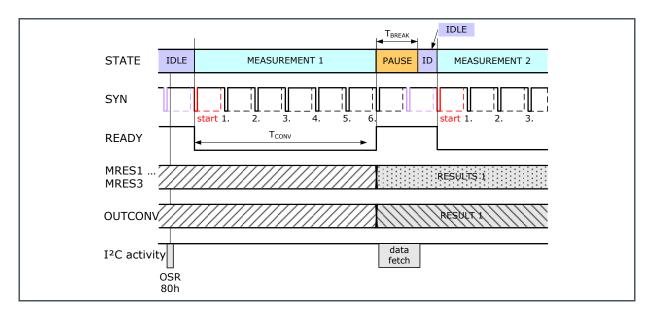

### 7.8 Synchronous Measurement Start and End Mode – SYND

In this mode, the signal at pin SYN controls the start and stop of a measurement completely. When the device is waiting in Measurement state and OSR:SS is set to ,1' the first falling edge at pin SYN starts the measurement. Each following falling edge of signal SYN, which occurs within the conversion time, can continue or stop the measurement. The content of the register EDGES determines, which edge is the stopping one. That means the measurement will not stop until a certain number of falling edges at pin SYN passed within the conversion time. The value of register EDGES determines the number of edges (see Figure 19 and chapter "Register - EDGES"). Figure 19 shows the principle sequence for a measurement start in SYND mode. While waiting in Measurement state is shown as IDLE, after OSR:SS is set to ,1' (see Figure 45) the AS73211 waits for signal SYN to start. The conversion time is set to 06h in register EDGES, during the pause time TBREAK falling edges at pin SYN are ignored.

#### Figure 19:

Principle Sequence for a Measurement Start in SYND Mode

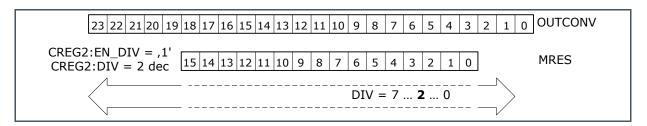

The conversion time (TCONV) is determined by the duration between the edges of start and stop of the signal SYN. If CREG2:EN\_TM is set to ,1', the register OUTCONV contains an equivalent amount of TCONV as counts of the internal clock. With the value of OUTCONV, the measurement results can be calculated more precisely (see chapter "Conversion Time Measurement in SYND Mode").

### 7.9 Energy Saving Options

The usage of the energy saving options is consistent for all measurement modes. The signal path at pin READY always represents independent of wake-up times or synchronizing events at pin SYN concerning the internal clock, the real measurement process. Every measurement mode can be terminated with OSR:SS = ,0' or changing to Configuration state at every time, whereas not completed A/D conversions are not stored. In case of both energy saving options Power Down state (POWDOWN) and Standby state (STANDBY) are switched on (OSR:PD = ,1' and CREG3:SB = ,1'). The startup times (T<sub>STARTPD</sub> and T<sub>STARTSB</sub>) run one after the other after Power Down and Standby is switched off.

### 7.10 Power Down

Power Down is an option to reduce the power consumption. After applying the power supply voltage including power-on reset or after software reset the AS73211 stays in Power Down state. The clock generator and all analog parts of the device are turned off. The power consumption of the device is close to zero. The digital part of the AS73211 stays idle, but a full communication via the I<sup>2</sup>C interface is granted in Configuration state and Measurement state as well.

In case of the Device Operational State (DOS) is set to Measurement mode the start/stop of a measurement is possible by setting the OSR:SS bit and reading of measurement data. The Power Down can be switched on and off by the bit OSR:PD (Figure 1). Switching on Power Down via bit OSR:PD = ,1' the AS73211 changes to the Power Down state after the end of an ongoing measurement. Switching off Power Down (OSR:PD = ,0') results in a change to the Idle state (IDLE for waiting) or Standby state depending on bit CREG3:SB. This change to another operational state is delayed by the startup time TSTARTPD of typically 1.2ms. A conversion can start in all measurement modes while the Power Down state is activated (OSR:PD = ,1'). In the measurement modes CMD and CONT it is done by setting the bit OSR:SS to ,1'. In addition, the falling edge of the signal at pin SYN for the measurement modes SYNS and SYND initiate the start. In all cases, the start of conversion is delayed by the startup time TSTARTPD. After the conversion in the CMD, SYNS and SYND modes the AS73211 changes back into the Power Down state, whereas the measurement of the CONT mode is interactive until it is stopped by setting bit OSR:SS = to ,0' before it changes back into the Power Down state.

There are two methods for startup the AS73211:

After applying the power supply voltage including power-on reset or after software reset the bit OSR:PD must be set to ,0' via I<sup>2</sup>C interface communication. The analog part and the internal clock system starts to work along the defined configuration of the AS73211. Nevertheless, it is still possible to change the configuration in front of time b) of Figure 20. The Device Operational State changes to Measurement state to start the measurement (OSR:SS = ,1') without further delay caused by energy saving options.

Figure 20 shows the principle sequence after power-on reset and separated writing of the bits OSR:PD, OSR:DOS and OSR:SS:

- a) OSR programming: 02h, after TSTARTPD continuing within Configuration state only,

- b) OSR programming: 03h, change to Measurement state waiting is shown as IDLE.

#### Figure 20:

Principle Sequence After Power-On Reset and Separated Writing of the Bits OSR:PD, OSR:DOS and OSR:SS

2. OSR programming: 80h, start of the measurement as stated in the device's configuration. Coming from Power Down state activated by OSR:PD = ,1' the AS73211 is active switched on not until OSR:SS is set to ,1' (together while or with OSR:DOS = 011b). That means the bit OSR:SS is a direct start condition for the CMD and CONT modes whereas for both SYN modes also the falling edge at pin SYN is necessary for the startup. The programmed measurement mode follows after startup marked by the falling edge of the signal path at pin READY. If the configuration even contains CREG3:SB = ,1' (as the example of Figure 21shows), additionally after startup time TSTARTPD the wake-up time TSTARTSB of 4µs follows before the measurement starts.

```

Figure 21:

```

| STATE                  | CONFIGURATION S MEASUREMENT                 |  |

|------------------------|---------------------------------------------|--|

|                        | T <sub>STARTPD</sub> STANDBY                |  |

| I <sup>2</sup> C activ | vity                                        |  |

|                        | $CREG3:SB \leftarrow ,1' OSR \\C3h \\a) b)$ |  |

Principle Start of the Measurement from OSR:PD = ,1' and CREG3:SB = ,1'

Figure 21 shows the principle start of the measurement from OSR:PD = ,1' and CREG3:SB = ,1':

- a) CREG3 programming: bit CREG3:SB = ,1',

- b) OSR programming: C3h, start of the measurement with prior run of TSTARTPD and TSTARTS.

The programmed energy saving option (before or when measurement is started or while the measurement runs) is switched on after the regular end of the measurement and storing of the results within the buffer registers. In case of an abortion of the measurement with OSR:SS = ,0' or switching to Configuration state the energy saving option is switched on without saving any results.

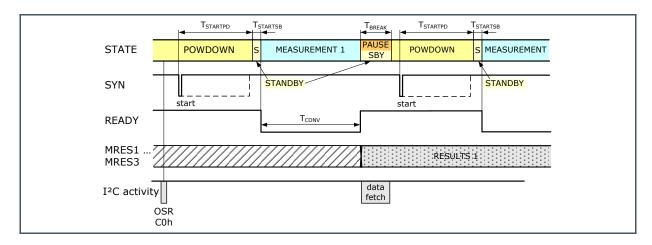

### 7.11 Standby

Standby is another option for reducing the power consumption, but compared to Power Down less internal analog components are switched off to be able to get back active in a very short time. The digital part of the AS73211 stays idle, but a full communication via the I<sup>2</sup>C interface is granted in Configuration state and Measurement state as well. The bit CREG3:SB can only be changed in Configuration mode. The wake-up process is possible in combination with the start condition of the configured Measurement mode. Standby is automatically deactivated by starting the CMD or CONT

measurement mode by setting the bit OSR:SS to ,1<sup>c</sup>. In addition, for the measurement modes SYNS and SYND an initiated start is necessary by the falling edge of the signal at pin SYN. While starting the measurement the A/D conversion follows immediately after the wake-up time TSTARTSB of about 4µs.

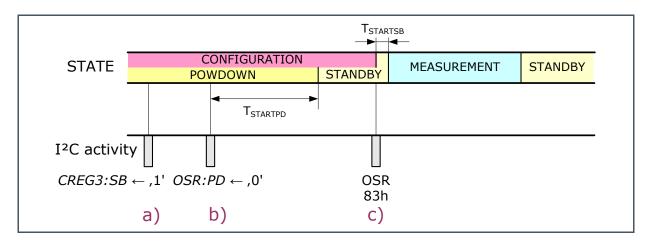

Figure 22 shows the principle start and stop sequence of a measurement after startup with  $OSR:PD = ,0^{\circ}$  and CREG3:SB = ,1:

- a) CREG3 programming: bit CREG3:SB = ,1',

- b) OSR programming: 02h, after startup continuing with Configuration mode,

- c) OSR programming: 83h, measurement start, wake-up and conversion, return to standby after measurement ends.

Figure 22:

Principle Start and Stop Sequence of a Measurement After Startup with OSR:PD = ,0' and CREG3:SB = ,1'

### 7.12 Examples

For both modes CONT and SYN it is recommended to configure a pause time TBREAK (register BREAK of Figure 52) to avoid disturbances during the A/D conversion caused by I<sup>2</sup>C interface communication. The selectable pause time using register BREAK should be long enough, that all output results are read before the next conversion starts (automatically in CONT modus or synchronized via pin SYN in SYN modes). While the pause time TBREAK is running it is possible to save energy if the bit CREG3:SB is configured to ,1'. The wake-up time TSTARTSB of about 4µs is short compared to the necessary time for the I<sup>2</sup>C communication protocol represented by register BREAK.

Figure 23 shows the principle sequence of CONT mode: if CREG3:SB is set to ,1', saving energy is possible while the pause time TBREAK is activated for I<sup>2</sup>C interface communication.

Figure 23:

Principle Sequence of CONT Mode - if CREG3:SB is Set to ,1'

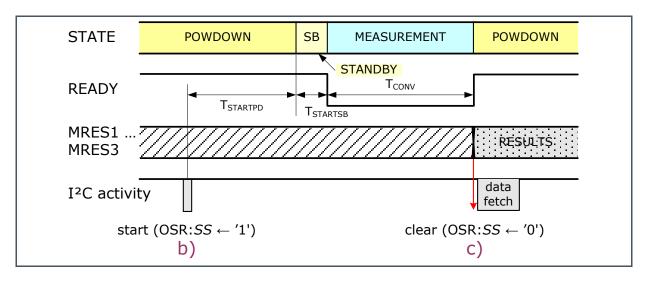

Another example shows, that after the end of a conversion in CMD mode the AS73211 returns to Power Down and/or Standby state depending on the bits OSR:PD and CREG3:SB. In case of both bits are ,0' while in Measurement state the device would return to idle, waiting for the next measurement to start. Figure 24: Principle sequence whereas measurement starts in CMD mode with Power Down and Standby switched on (device is already in Measurement state):

- a) CREG3 programming: bit CREG3:SB = ,1' was set in Configuration state (not shown),

- b) OSR programming: C0h, "startup" and "wake-up" before conversion starts,

- c) "Automatically" OSR programming: 43h, the end of conversion resets bit OSR:SS, return to Power Down.

Figure 24:

Principle Sequence Whereas Measurement is Started in CMD Mode with Power Down, Standby Switched On

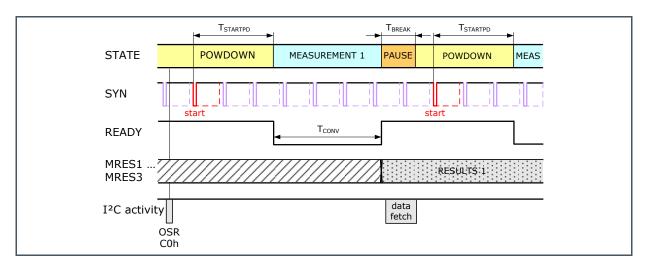

It is also possible to use Power Down state in combination with SYNS mode. The falling edge at pin SYN immediately starts the conversion after Power Down ends shown by the signal at pin READY. That kind of measurement is only useful in case of the distance between falling edges at pin SYN is more than the conversion time, pause time and startup time together. Figure 25 shows the principle sequence of measurement in SYNS mode being ready (bits OSR:PD = ,1' and OSR:SS = ,1') and waiting for falling edge at pin SYN to startup.

#### Figure 25:

Principle Sequence of Measurement in SYNS Mode

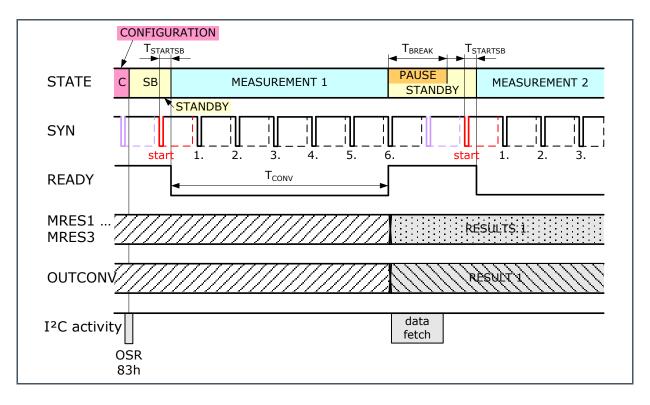

By additionally activated Standby (bit CREG3:SB =  $,1^{\circ}$ ) a maximum of energy can be saved, because the operational readiness is given not until short before A/D conversion starts and with the beginning read process of the results (pause time) the device is already again saving energy in Standby state (see Figure 26). Figure 26 shows the principle sequence of measurement in SYNS mode being ready with OSR:PD =  $,1^{\circ}$  (as in Figure 25), but now with bit CREG3:SB =  $,1^{\circ}$  to save a maximum of energy as explained above.

#### Figure 26:

Principle Sequence of Measurement in SYNS Mode Being Ready with OSR:PD = ,1'

The following example of a SYNS mode shows a correct measurement procedure but with an unfavorable chosen application. After start of measurement with bit OSR:SS = ,1' only the red marked falling edges (see Figure 27) at pin SYN are accepted as start condition, because of the too tight distances of the SYN edges a lot of falling edges are ignored during startup phase (TSTARTPD), conversion time (TCONV) and pause time (TBREAK).

#### Figure 27:

Principle Sequence of Measurement in SYNS Mode (OSR:PD, OSR:SS are set to ,1')

Continuously occurring SYN pulses (e.g. generated by a PWM controlling in measurement mode SYND) are ignored in Configuration state and while pause time TBREAK (see Figure 28) is activated. It is recommended to increase the default value of register BREAK accordingly, if the time reference result OUTCONV must be read via I<sup>2</sup>C interface. The conversion time is given by register EDGES, but as shown in Figure 28 the real conversion time is always represented by TCONV at pin READY. Furthermore, the output result OUTCONV can be used to get the right measurement result (see also chapters "Transfer Function" and "Conversion Time Measurement in SYND Mode"). Figure 28 shows the principle sequence of measurement in SYND mode ready for wake-up after switch off Power Down state with OSR:PD = ,0' and setting of OSR:SS to ,1' in Configuration state, then waiting for start via pin SYN (with exemplary settings of EDGES = 06h and CREG3:SB = ,1' for energy saving while pause time TBREAK).

#### Figure 28:

Principle Sequence of Measurement in SYND Mode Ready for Wake-Up After Switch Off Power Down State

### 7.13 Transfer Function

In generally the implemented A/D converter represents a delta-sigma converter, which performs charge balancing between the input light at the photodiodes and an internal reference. The input currents of the photodiodes result in pulse density modulated digital signals, further filtered by counters up to 24 bits. At the end, each channel's counter status represents a digital equivalent of the average input light irradiance regarding to the channel's sensor area within the conversion time interval. The input light irradiance can be calculated from the measurement result by:

Equation 1:

$$E_e = \frac{MRES}{R_e} = \frac{FSR_{E_e}}{N_{CLK}} \bullet MRES$$

**Equation 2:**

$$E_{e} = \frac{FSR_{E_{e}}}{T_{CONV} \bullet f_{CLK}} \bullet MRES$$

MRES: Digital output value of the conversion (content of output registers MRES1 to MRES3)

E<sub>e</sub>: Input light irradiance regarding to the photodiode's area within the conversion time interval

FSR<sub>Ee</sub>: Full Scale Range of detectable input light irradiance Ee

R<sub>e</sub>: Irradiance responsivity (see Figure 14)

T<sub>CONV</sub>: Conversion time interval

**N**<sub>CLK</sub>: Number of clock cycles within the conversion time interval T<sub>CONV</sub> (see Figure 13)

fclk: Clock frequency

In the CONT, CMD and SYNS modes the conversion time T<sub>CONV</sub> is internally generated<sup>1</sup>. In the SYND mode the conversion time is defined by the timing of the external pulses at SYN pin and the number of pulses stored in the register EDGES (see Figure 19 chapter "Conversion time measurements in SYND mode" and chapter "Register - EDGES").

The number of clock counts within this interval is a constant number, which keeps the output result independent of the internal clock frequency. In this case the input light irradiance  $E_e$  regarding to the photodiodes area of the channel can be represented by the Equation 1. In SYND mode, the Equation 2 represents the externally generated conversion time TCONV and the conversion result. If the conversion time measurement is activated (CREG2:EN\_TM = ,1') the number of clock counts within the externally given conversion time can also be internally captured. So the input light irradiance  $E_e$  regarding to the photodiode's area of the channel can be calculated as:

**Equation 3:**

$$E_{e} = \frac{FSR_{E_{e}}}{OUTCONV} \bullet MRES$$

MRES: Digital output value of the conversion (content of output registers MRES1 to MRES3)

Ee: Input light irradiance regarding to the photodiode's area within the conversion time interval

FSR<sub>Ee</sub>: Full Scale Range of detectable input light irradiance Ee

OUTCONV: Conversion time duration expressed as the number of clock counts within this time.

In this way, the input light irradiance can be measured independently of the internal frequency and furthermore external conversion time variations in SYND mode.

The calculation of the input light irradiance by Equation 3 is more precise than the result of Equation 2 because the tolerances of the clock frequency  $f_{CLK}$  are eliminated. The irradiance responsivity  $R_e$  and

<sup>&</sup>lt;sup>1</sup> The system clock is internally generated and is subject to technological tolerances. So the clock frequency may vary, which must be considered when calculating the time to be programmed (e. g. registers BREAK for pause time TBREAK or CREG1:TIME for conversion time TCONV).

internal conversion time TCONV are determined by the content of register bits CREG1:GAIN and CREG1:TIME (see Figure 48). Their values directly determine the sensitivity, the LSB value and the full-scale range (FSR) of the detectable irradiance  $E_e$  of the A/D conversion.

Figure 29:

X-Channel ( $\lambda$  = 600nm) Programmable FSR and LSB of the Detectable Input Light Irradiance E<sub>e</sub> with CREG1:TIME Programming from 0 to 7 and CREG1:GAIN Programming from 0 to 11 – CONT, CMD and SYNS Mode

| TIME <sup>(1)</sup> | 0          | 1          | 2                       | 3                            | 4                | 5          | 6        | 7        |  |

|---------------------|------------|------------|-------------------------|------------------------------|------------------|------------|----------|----------|--|

| NCLK(1)             | 1024       | 2048       | 4096                    | 8192                         | 16384            | 32768      | 65536    | 131072   |  |

| TCONV[ms](1)        | 1          | 2          | 4                       | 8                            | 16               | 32         | 64       | 128      |  |

| RESOL[bit](1)       | 10         | 11         | 12                      | 13                           | 14               | 15         | 16       | 17       |  |

| GAIN(1)             |            |            | FSR [µW/cm              | <sup>2</sup> ] of detectable | irradiance Ee (o | hannel X)  | •        |          |  |

| 2048x               |            |            |                         | 13.854                       |                  |            |          | 6.927    |  |

| 1024x               |            |            |                         | 27.707                       |                  |            |          | 13.854   |  |

| 512x                |            |            |                         | 55.414                       |                  |            |          | 27.707   |  |

| 256x                |            |            |                         | 110.828                      |                  |            |          | 55.414   |  |

| 128x                |            |            |                         | 221.657                      |                  |            |          | 110.828  |  |

| 64x                 |            |            |                         | 443.314                      |                  |            |          | 221.657  |  |

| 32x                 |            | 886.628    |                         |                              |                  |            |          |          |  |

| 16x                 | 1773.255   |            |                         |                              |                  |            |          |          |  |

| 8x                  | 3546.510   |            |                         |                              |                  |            |          |          |  |

| 4x                  | 7093.020   |            |                         |                              |                  |            |          |          |  |

| 2x                  | 14186.041  |            |                         |                              |                  |            |          |          |  |

| 1x                  | 28372.081  |            |                         |                              |                  |            |          |          |  |

| GAIN (1)            |            |            | LSB [nW/cm <sup>2</sup> | ] – least signific           | ant bit of FSR ( | channel X) | -        |          |  |

| 2048x               | 13.5289    | 6.7644     | 3.3822                  | 1.6911                       | 0.8456           | 0.4228     | 0.2114   | 0.1057   |  |

| 1024x               | 27.0577    | 13.5289    | 6.7644                  | 3.3822                       | 1.6911           | 0.8456     | 0.4228   | 0.2114   |  |

| 512x                | 54.1155    | 27.0577    | 13.5289                 | 6.7644                       | 3.3822           | 1.6911     | 0.8456   | 0.4228   |  |

| 256x                | 108.2309   | 54.1155    | 27.0577                 | 13.5289                      | 6.7644           | 3.3822     | 1.6911   | 0.8456   |  |

| 128x                | 216.4618   | 108.2309   | 54.1155                 | 27.0577                      | 13.5289          | 6.7644     | 3.3822   | 1.6911   |  |

| 64x                 | 432.9236   | 216.4618   | 108.2309                | 54.1155                      | 27.0577          | 13.5289    | 6.7644   | 3.3822   |  |

| 32x                 | 865.8472   | 432.9236   | 216.4618                | 108.2309                     | 54.1155          | 27.0577    | 13.5289  | 6.7644   |  |

| 16x                 | 1731.6944  | 865.8472   | 432.9236                | 216.4618                     | 108.2309         | 54.1155    | 27.0577  | 13.5289  |  |

| 8x                  | 3463.3888  | 1731.6944  | 865.8472                | 432.9236                     | 216.4618         | 108.2309   | 54.1155  | 27.0577  |  |

| 4x                  | 6926.7777  | 3463.3888  | 1731.6944               | 865.8472                     | 432.9236         | 216.4618   | 108.2309 | 54.1155  |  |

| 2x                  | 13853.5554 | 6926.7777  | 3463.3888               | 1731.6944                    | 865.8472         | 432.9236   | 216.4618 | 108.2309 |  |

| 1x                  | 27707.1108 | 13853.5554 | 6926.7777               | 3463.3888                    | 1731.6944        | 865.8472   | 432.9236 | 216.4618 |  |

(1) TIME (TCONV) – given by CREG1:TIME = 0 ... 7 dec, NCLK – number of clock cycle within conversion time TCONV, RESOL – Resolution of internal A/D conversion, GAIN = 1x given by CREG1:GAIN = 11dec up to GAIN = 2048x given by CREG1:GAIN = 0dec (see Figure 48)

#### Figure 30:

X-Channel ( $\lambda$  = 600nm) Programmable FSR and LSB of the Detectable Input Light Irradiance Ee with CREG1:TIME Programming from 8 to and CREG1:GAIN Programming from 0 to 11 – CONT, CMD and SYNS Mode

| TIME <sup>(1)</sup>                    | 8        | 9        | 10                      | 11                         | 12               | 13            | 14       | 15         |

|----------------------------------------|----------|----------|-------------------------|----------------------------|------------------|---------------|----------|------------|

| N <sub>CLK</sub> <sup>(1)</sup>        | 262144   | 524288   | 1.05E+06                | 2.10E+06                   | 4.19E+06         | 8.39E+06      | 1.68E+07 | 1024       |

| T <sub>CONV</sub> [s] <sup>(1)</sup>   | 0.256    | 0.512    | 1.024                   | 2.048                      | 4.096            | 8.192         | 16.384   | 0.001      |

| R <sub>ESOL</sub> [bit] <sup>(1)</sup> | 18       | 19       | 20                      | 21                         | 22               | 23            | 24       | 10         |

| GAIN <sup>(1)</sup>                    |          |          | FSR [µW/cm              | <sup>2</sup> ] of detectab | le irradiance E  | e (channel X  | )        |            |

| 2048x                                  | 3.463    | 1.732    | 0.866                   | 0.433                      | 0.216            | 0.108         | 0.054    | 13.854     |

| 1024x                                  | 6.927    | 3.463    | 1.732                   | 0.866                      | 0.433            | 0.216         | 0.108    | 27.707     |

| 512x                                   | 13.854   | 6.927    | 3.463                   | 1.732                      | 0.866            | 0.433         | 0.216    | 55.414     |

| 256x                                   | 27.707   | 13.854   | 6.927                   | 3.463                      | 1.732            | 0.866         | 0.433    | 110.828    |

| 128x                                   | 55.414   | 27.707   | 13.854                  | 6.927                      | 3.463            | 1.732         | 0.866    | 221.657    |

| 64x                                    | 110.828  | 55.414   | 27.707                  | 13.854                     | 6.927            | 3.463         | 1.732    | 443.314    |

| 32x                                    | 221.657  | 110.828  | 55.414                  | 27.707                     | 13.854           | 6.927         | 3.463    | 886.628    |

| 16x                                    | 443.314  | 221.657  | 110.828                 | 55.414                     | 27.707           | 13.854        | 6.927    | 1773.255   |

| 8x                                     | 886.628  | 443.314  | 221.657                 | 110.828                    | 55.414           | 27.707        | 13.854   | 3546.510   |

| 4x                                     | 1773.255 | 886.628  | 443.314                 | 221.657                    | 110.828          | 55.414        | 27.707   | 7093.020   |

| 2x                                     | 3546.510 | 1773.255 | 886.628                 | 443.314                    | 221.657          | 110.828       | 55.414   | 14186.041  |

| 1x                                     | 7093.020 | 3546.510 | 1773.255                | 886.628                    | 443.314          | 221.657       | 110.828  | 28372.081  |

| GAIN <sup>(1)</sup>                    |          |          | LSB [nW/cm <sup>2</sup> | ²] – least signi           | ficant bit of FS | SR (channel X | ()       |            |

| 2048x                                  | 0.0528   | 0.0264   | 0.0132                  | 0.0066                     | 0.0033           | 0.0017        | 0.0008   | 13.5289    |

| 1024x                                  | 0.1057   | 0.0528   | 0.0264                  | 0.0132                     | 0.0066           | 0.0033        | 0.0017   | 27.0577    |

| 512x                                   | 0.2114   | 0.1057   | 0.0528                  | 0.0264                     | 0.0132           | 0.0066        | 0.0033   | 54.1155    |

| 256x                                   | 0.4228   | 0.2114   | 0.1057                  | 0.0528                     | 0.0264           | 0.0132        | 0.0066   | 108.2309   |

| 128x                                   | 0.8456   | 0.4228   | 0.2114                  | 0.1057                     | 0.0528           | 0.0264        | 0.0132   | 216.4618   |

| 64x                                    | 1.6911   | 0.8456   | 0.4228                  | 0.2114                     | 0.1057           | 0.0528        | 0.0264   | 432.9236   |

| 32x                                    | 3.3822   | 1.6911   | 0.8456                  | 0.4228                     | 0.2114           | 0.1057        | 0.0528   | 865.8472   |

| 16x                                    | 6.7644   | 3.3822   | 1.6911                  | 0.8456                     | 0.4228           | 0.2114        | 0.1057   | 1731.6944  |

| 8x                                     | 13.5289  | 6.7644   | 3.3822                  | 1.6911                     | 0.8456           | 0.4228        | 0.2114   | 3463.3888  |

| 4x                                     | 27.0577  | 13.5289  | 6.7644                  | 3.3822                     | 1.6911           | 0.8456        | 0.4228   | 6926.7777  |

| 2x                                     | 54.1155  | 27.0577  | 13.5289                 | 6.7644                     | 3.3822           | 1.6911        | 0.8456   | 13853.5554 |

| 1x                                     | 108.2309 | 54.1155  | 27.0577                 | 13.5289                    | 6.7644           | 3.3822        | 1.6911   | 27707.1108 |

(1) TIME (TCONV) – given by CREG1:TIME = 8 ... 15 dec, NCLK – number of clock cycle within conversion time TCONV, RESOL – Resolution of internal A/D conversion, GAIN = 1x given by CREG1:GAIN = 11dec up to GAIN = 2048x given by CREG1:GAIN = 0dec (see Figure 48)

#### Figure 31:

Y-Channel ( $\lambda$  = 555nm) Programmable FSR and LSB of the Detectable Input Light Irradiance Ee with CREG1:TIME Programming from 0 to 7 and CREG1:GAIN Programming from 0 to 11 – CONT, CMD and SYNS Mode

| TIME <sup>(1)</sup>                    | 0         | 1                                                    | 2             | 3                                  | 4              | 5           | 6       | 7       |  |  |  |

|----------------------------------------|-----------|------------------------------------------------------|---------------|------------------------------------|----------------|-------------|---------|---------|--|--|--|

| N <sub>CLK</sub> <sup>(1)</sup>        | 1024      | 2048                                                 | 4096          | 8192                               | 16384          | 32768       | 65536   | 131072  |  |  |  |

| T <sub>CONV</sub> [ms] <sup>(1)</sup>  | 1         | 2                                                    | 4             | 8                                  | 16             | 32          | 64      | 128     |  |  |  |

| R <sub>ESOL</sub> [bit] <sup>(1)</sup> | 10        | 11                                                   | 12            | 13                                 | 14             | 15          | 16      | 17      |  |  |  |

| GAIN <sup>(1)</sup>                    |           | FSR [μW/cm²] of detectable irradiance Ee (channel Y) |               |                                    |                |             |         |         |  |  |  |

| 2048x                                  |           |                                                      |               | 14.919                             |                |             |         | 7.460   |  |  |  |

| 1024x                                  |           |                                                      |               | 29.838                             |                |             |         | 14.919  |  |  |  |

| 512x                                   |           |                                                      |               | 59.677                             |                |             |         | 29.838  |  |  |  |

| 256x                                   |           |                                                      |               | 119.354                            |                |             |         | 59.677  |  |  |  |

| 128x                                   |           |                                                      |               | 238.707                            |                |             |         | 119.354 |  |  |  |

| 64x                                    |           |                                                      |               | 477.415                            |                |             |         | 238.707 |  |  |  |

| 32x                                    |           |                                                      |               | 954.830                            |                |             |         | 477.415 |  |  |  |

| 16x                                    | 1909.659  |                                                      |               |                                    |                |             |         |         |  |  |  |

| 8x                                     | 3819.319  |                                                      |               |                                    |                |             |         |         |  |  |  |

| 4x                                     | 7638.637  |                                                      |               |                                    |                |             |         |         |  |  |  |

| 2x                                     | 15277.275 |                                                      |               |                                    |                |             |         |         |  |  |  |

| 1x                                     | 30554.549 |                                                      |               |                                    |                |             |         |         |  |  |  |

| GAIN <sup>(1)</sup>                    |           | L                                                    | SB [nW/cm²] · | <ul> <li>least signific</li> </ul> | ant bit of FSR | (channel Y) |         |         |  |  |  |

| 2048x                                  | 14.570    | 7.285                                                | 3.642         | 1.821                              | 0.911          | 0.455       | 0.228   | 0.114   |  |  |  |

| 1024x                                  | 29.139    | 14.570                                               | 7.285         | 3.642                              | 1.821          | 0.911       | 0.455   | 0.228   |  |  |  |

| 512x                                   | 58.278    | 29.139                                               | 14.570        | 7.285                              | 3.642          | 1.821       | 0.911   | 0.455   |  |  |  |

| 256x                                   | 116.556   | 58.278                                               | 29.139        | 14.570                             | 7.285          | 3.642       | 1.821   | 0.911   |  |  |  |

| 128x                                   | 233.113   | 116.556                                              | 58.278        | 29.139                             | 14.570         | 7.285       | 3.642   | 1.821   |  |  |  |

| 64x                                    | 466.225   | 233.113                                              | 116.556       | 58.278                             | 29.139         | 14.570      | 7.285   | 3.642   |  |  |  |

| 32x                                    | 932.451   | 466.225                                              | 233.113       | 116.556                            | 58.278         | 29.139      | 14.570  | 7.285   |  |  |  |

| 16x                                    | 1864.902  | 932.451                                              | 466.225       | 233.113                            | 116.556        | 58.278      | 29.139  | 14.570  |  |  |  |

| 8x                                     | 3729.803  | 1864.902                                             | 932.451       | 466.225                            | 233.113        | 116.556     | 58.278  | 29.139  |  |  |  |

| 4x                                     | 7459.607  | 3729.803                                             | 1864.902      | 932.451                            | 466.225        | 233.113     | 116.556 | 58.278  |  |  |  |

| 2x                                     | 14919.214 | 7459.607                                             | 3729.803      | 1864.902                           | 932.451        | 466.225     | 233.113 | 116.556 |  |  |  |

| 1x                                     | 29838.427 | 14919.214                                            | 7459.607      | 3729.803                           | 1864.902       | 932.451     | 466.225 | 233.113 |  |  |  |

(1) TIME (TCONV) – given by CREG1:TIME = 0 ... 7 dec, N<sub>CLK</sub> – number of clock cycle within conversion time TCONV, R<sub>ESOL</sub> – Resolution of internal A/D conversion, GAIN = 1x given by CREG1:GAIN = 11dec up to GAIN = 2048x given by CREG1:GAIN = 0dec (see Figure 48).

#### Figure 32:

Y-Channel ( $\lambda$  = 555nm) Programmable FSR and LSB of the Detectable Input Light Irradiance Ee with CREG1:TIME Programming from 8 to 15 and CREG1:GAIN Programming from 0 to 11 – CONT, CMD and SYNS Mode

| TIME <sup>(1)</sup>                    | 8        | 9        | 10                      | 11                          | 12               | 13            | 14       | 15        |

|----------------------------------------|----------|----------|-------------------------|-----------------------------|------------------|---------------|----------|-----------|

| N <sub>CLK</sub> <sup>(1)</sup>        | 262144   | 524288   | 1.05E+06                | 2.10E+06                    | 4.19E+06         | 8.39E+06      | 1.68E+07 | 1024      |

| T <sub>CONV</sub> [s] <sup>(1)</sup>   | 0.256    | 0.512    | 1.024                   | 2.048                       | 4.096            | 8.192         | 16.384   | 0.001     |

| R <sub>ESOL</sub> [bit] <sup>(1)</sup> | 18       | 19       | 20                      | 21                          | 22               | 23            | 24       | 10        |

| GAIN <sup>(1)</sup>                    |          |          | FSR [µW/cm              | <sup>2</sup> ] of detectabl | e irradiance E   | e (channel Y) |          |           |

| 2048x                                  | 3.730    | 1.865    | 0.932                   | 0.466                       | 0.233            | 0.117         | 0.058    | 14.919    |

| 1024x                                  | 7.460    | 3.730    | 1.865                   | 0.932                       | 0.466            | 0.233         | 0.117    | 29.838    |

| 512x                                   | 14.919   | 7.460    | 3.730                   | 1.865                       | 0.932            | 0.466         | 0.233    | 59.677    |

| 256x                                   | 29.838   | 14.919   | 7.460                   | 3.730                       | 1.865            | 0.932         | 0.466    | 119.354   |

| 128x                                   | 59.677   | 29.838   | 14.919                  | 7.460                       | 3.730            | 1.865         | 0.932    | 238.707   |

| 64x                                    | 119.354  | 59.677   | 29.838                  | 14.919                      | 7.460            | 3.730         | 1.865    | 477.415   |

| 32x                                    | 238.707  | 119.354  | 59.677                  | 29.838                      | 14.919           | 7.460         | 3.730    | 954.830   |

| 16x                                    | 477.415  | 238.707  | 119.354                 | 59.677                      | 29.838           | 14.919        | 7.460    | 1909.659  |

| 8x                                     | 954.830  | 477.415  | 238.707                 | 119.354                     | 59.677           | 29.838        | 14.919   | 3819.319  |

| 4x                                     | 1909.659 | 954.830  | 477.415                 | 238.707                     | 119.354          | 59.677        | 29.838   | 7638.637  |

| 2x                                     | 3819.319 | 1909.659 | 954.830                 | 477.415                     | 238.707          | 119.354       | 59.677   | 15277.275 |

| 1x                                     | 7638.637 | 3819.319 | 1909.659                | 954.830                     | 477.415          | 238.707       | 119.354  | 30554.549 |

| GAIN <sup>(1)</sup>                    |          |          | LSB [nW/cm <sup>2</sup> | ²] – least signi            | ficant bit of FS | SR (channel Y | )        |           |