# MxFE Quad, 16-Bit, 12 GSPS RF DAC and Dual, 12-Bit, 6 GSPS RF ADC

**Data Sheet**

# AD9082

#### FEATURES

Flexible reconfigurable common platform design 4 DACs and 2 ADCs (4D2A) Supports single, dual, and quad band Maximum DAC/ADC sample rate up to 12 GSPS/6 GSPS DAC to ADC sample rate ratios of 1, 2, 3, and 4 ADC and DAC datapath bypass option Analog bandwidth to 8 GHz Full-scale output current range, ac coupling: 7 mA to 40 mA **On-chip PLL with multichip synchronization External RFCLK input option** ADC ac performance at 6 GSPS Full-scale input voltage: 1.475 V p-p Full-scale sine wave input power: 4.4 dBm Noise density: -153 dBFS/Hz Noise figure: 25.3 dB HD2: -65.2 dBFS at 2.7 GHz HD3: -70.8 dBFS at 2.7 GHz Worst other (excluding HD2 and HD3): -68.5 dBFS at 2.7 GHz DAC ac performance at 3.7 GHz output 2-tone IMD3 (-7 dBFS per tone): -78.9 dBc NSD, single-tone, f<sub>DAC</sub> = 12 GSPS: -155.1 dBc/Hz SFDR, single-tone, f<sub>DAC</sub> = 12 GSPS: -70 dBc Versatile digital features Supports real or complex digital data (8-, 12-, 16-, or 24-bit) Selectable interpolation and decimation filters **Configurable DDC and DUC** 8 fine complex DUCs and 4 coarse complex DUCs 8 fine complex DDCs and 4 coarse complex DDCs 48-bit NCO per DUC/DDC Option to bypass fine and coarse DUC/DDC Programmable 192-tap PFIR filter for receive equalization Supports 4 different profile settings loaded via GPIO Programable delay per data path **Receive AGC support** Fast detect with low latency for fast AGC control Signal monitor for slow AGC control **Dedicated AGC support pins Transmit DPD support** Fine DUC channel gain control and delay adjust Coarse DDC delay adjust for DPD observation path

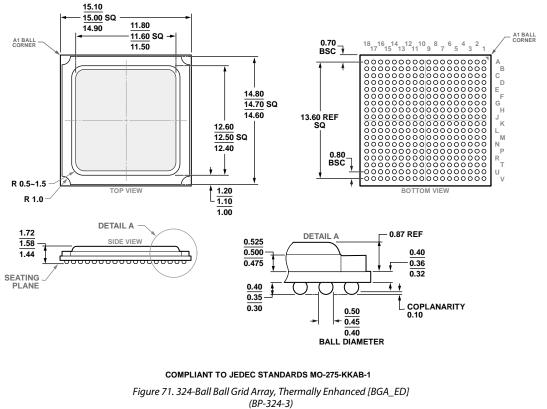

**Auxiliary features Fast frequency hopping Direct digital synthesis (DDS)** Low latency digital loopback mode (ADC to DAC) ADC clock driver with selectable divide ratios Power amplifier downstream protection circuitry **On-chip temperature monitoring unit Flexible GPIOx pins TDD** power savings option SERDES JESD204B/JESD204C interface, 16 lanes up to 16.22 Gbps 8 lanes per DACs and ADCs JESD204B compatible with the maximum 15.5 Gbps lane rate JESD204C compatible with the maximum 16.22 Gbps lane rate Sample and bit repeat mode for lane rate matching Total power consumption: 11.45 W typical 15 mm × 15 mm, 324-ball BGA with 0.8 mm pitch APPLICATIONS

Wireless communications infrastructure Microwave point-to-point, E-band and 5G mmWave Broadband communications systems DOCSIS 3.1 and 4.0 CMTS Phased array radar and electronic warfare Electronic test and measurement systems

#### **GENERAL DESCRIPTION**

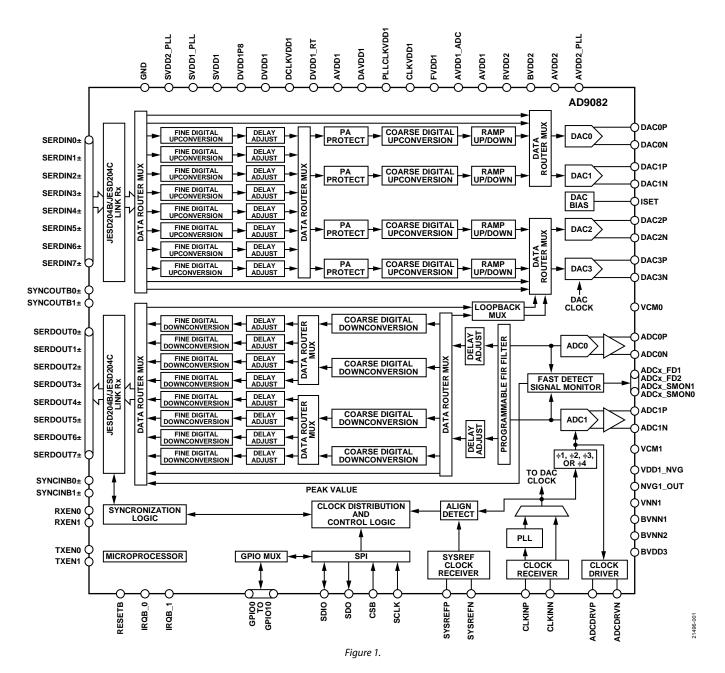

The mixed signal front-end (MxFE\*) is a highly integrated device with a 16-bit, 12 GSPS maximum sample rate, RF digital-to-analog converter (DAC) core, and 12-bit, 6 GSPS rate, RF analog-todigital converter (ADC) core. The AD9082 supports four transmitter channels and two receiver channels. The AD9082 is well suited for applications requiring both wideband ADCs and DACs to process signal(s) having wide instantaneous bandwidth. The device features a 16 lane, 16.22 Gbps JESD204C or 15.5 Gbps JESD204B data transceiver port, an on-chip clock multiplier, and a digital signal processing (DSP) capability targeted at either wideband or multiband, direct to RF applications. The AD9082 also features a bypass mode that allows the full bandwidth capability of the ADC and/or DAC cores to bypass the DSP datapaths. The device also features low latency loopback and frequency hopping modes targeted at phase array radar system and electronic warfare applications.

#### Rev. A

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **TABLE OF CONTENTS**

| Features1                                                              |

|------------------------------------------------------------------------|

| Applications 1                                                         |

| General Description1                                                   |

| Revision History                                                       |

| Functional Block Diagram 3                                             |

| Specifications                                                         |

| Recommended Operating Conditions 4                                     |

| DC Specifications 4                                                    |

| DAC and ADC Sampling Specifications5                                   |

| Power Consumption                                                      |

| Clock Input and Phase-Locked Loop (PLL) Frequency<br>Specifications    |

| Input and Output Data Rates and Signal Bandwidth<br>Specifications7    |

| JESD204B and JESD204C Interface Electrical and Speed<br>Specifications |

| CMOS Pin Specifications9                                               |

#### **REVISION HISTORY**

| 9/2020—Rev. 0 to Rev. A |  |

|-------------------------|--|

| Changes to Figure 1     |  |

| Changes to Figure 5     |  |

| Changes to Table 14     |  |

| Changes to Table 14     |  |

6/2020—Revision 0: Initial Version

| DAC AC Specifications                       | 9  |

|---------------------------------------------|----|

| ADC AC Specifications                       |    |

| Timing Specifications                       | 13 |

| Absolute Maximum Ratings                    | 15 |

| Reflow Profile                              | 15 |

| Thermal Resistance                          | 15 |

| ESD Caution                                 | 15 |

| Pin Configuration and Function Descriptions | 16 |

| Typical Performance Characteristics         |    |

| DAC                                         |    |

| ADC                                         |    |

| Theory of Operation                         |    |

| Outline Dimensions                          | 33 |

| Ordering Guide                              |    |

## FUNCTIONAL BLOCK DIAGRAM

### SPECIFICATIONS RECOMMENDED OPERATING CONDITIONS

Successful DAC calibration is required during the device initialization phase that occurs shortly after power-up to ensure long-term reliability of the DAC core circuitry. Refer to UG-1578, the device user guide, for more information on device initialization.

| Table 1.                                              |      |     |      |      |

|-------------------------------------------------------|------|-----|------|------|

| Parameter                                             | Min  | Тур | Мах  | Unit |

| OPERATING JUNCTION TEMPERATURE (TJ)                   |      |     | 120  | °C   |

| ANALOG SUPPLY VOLTAGE RANGE                           |      |     |      |      |

| AVDD2, BVDD2, RVDD2                                   | 1.9  | 2.0 | 2.1  | V    |

| AVDD1, AVDD1_ADC, CLKVDD1, FVDD1, VDD1_NVG1           | 0.95 | 1.0 | 1.05 | V    |

| DIGITAL SUPPLY VOLTAGE RANGE                          |      |     |      |      |

| DVDD1, DVDD1_RT, DCLKVDD1, DAVDD1                     | 0.95 | 1.0 | 1.05 | V    |

| DVDD1P8                                               | 1.7  | 1.8 | 2.1  | V    |

| SERIALIZER/DESERIALIZER (SERDES) SUPPLY VOLTAGE RANGE |      |     |      |      |

| SVDD2_PLL                                             | 1.9  | 2.0 | 2.1  | V    |

| SVDD1, SVDD1_PLL                                      | 0.95 | 1.0 | 1.05 | V    |

#### DC SPECIFICATIONS

Nominal supplies with DAC output full-scale current ( $I_{OUTFS}$ ) = 26 mA, unless otherwise noted. For the minimum and maximum values,  $T_{I} = -40^{\circ}$ C to +120°C, and for the typical values,  $T_{A} = 25^{\circ}$ C, unless otherwise noted.

| Parameter                                                         | Test Conditions/Comments                                     | Min | Тур        | Max | Unit |

|-------------------------------------------------------------------|--------------------------------------------------------------|-----|------------|-----|------|

| DAC RESOLUTION                                                    |                                                              | 16  |            |     | Bit  |

| ADC RESOLUTION                                                    |                                                              | 12  |            |     | Bit  |

| DAC ACCURACY                                                      |                                                              |     |            |     |      |

| Gain Error                                                        |                                                              |     | 1.5        |     | %FSR |

| Gain Matching                                                     |                                                              |     | 0.1        |     | %FSR |

| Integral Nonlinearity (INL)                                       | Shuffling disabled                                           |     | 8.0        |     | LSB  |

| Differential Nonlinearity (DNL)                                   | Shuffling disabled                                           |     | 3.5        |     | LSB  |

| ADC ACCURACY                                                      |                                                              |     |            |     |      |

| No Missing Codes                                                  |                                                              |     | Guaranteed |     |      |

| Offset Error                                                      |                                                              |     | 0.57       |     | %FSR |

| Offset Matching                                                   |                                                              |     | 0.26       |     | %FSR |

| Gain Error                                                        |                                                              |     | 5.34       |     | %FSR |

| Gain Matching                                                     |                                                              |     | 1.06       |     | %FSR |

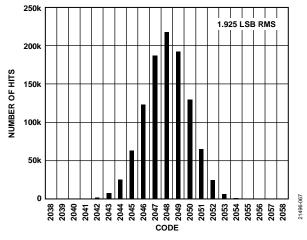

| DNL                                                               | Dithering enabled                                            |     | 0.32       |     | LSB  |

| INL                                                               | Dithering enabled                                            |     | 1.38       |     | LSB  |

| DAC ANALOG OUTPUTS                                                | DACxP and DACxN                                              |     |            |     |      |

| Full-Scale Output Current Range                                   | AC coupling, setting resistance ( $R_{SET}$ ) = 5 k $\Omega$ |     |            |     |      |

| AC Coupling                                                       | Output common-mode voltage ( $V_{CM}$ ) = 0 V                | 7   | 26         | 40  | mA   |

| DC Coupling                                                       | $V_{CM} = 0.3 V$                                             |     | 20         |     | mA   |

| Full-Scale Sinewave Output Power with<br>AC Coupling <sup>1</sup> | ldeal 2:1 balun interface to 50 $\Omega$                     |     |            |     |      |

| $I_{OUTFS} = 26 \text{ mA}$                                       |                                                              |     | 3.3        |     | dBm  |

| $I_{OUTFS} = 40 \text{ mA}$                                       |                                                              |     | 7          |     | dBm  |

| Common-Mode Output Voltage (VCM <sub>OUT</sub> )                  |                                                              |     | 0          |     | v    |

| Differential Impedance                                            |                                                              |     | 100        |     | Ω    |

| Parameter                                          | Test Conditions/Comments                                                         | Min | Тур Мах  | Unit   |

|----------------------------------------------------|----------------------------------------------------------------------------------|-----|----------|--------|

| ADC ANALOG INPUTS                                  | ADCxP and ADCxN                                                                  |     |          |        |

| Differential Input Voltage                         |                                                                                  |     | 1.475    | V р-р  |

| Full-Scale Sine Wave Input Power                   | Input power level resulting 0 dBFS tone level on fast<br>Fourier transform (FFT) |     | 4.4      | dBm    |

| Common-Mode Input Voltage (VCM <sub>IN</sub> )     | AC-coupled, equal to voltage at VCMx for ADCx input                              |     | 1        | V      |

| Differential Input                                 |                                                                                  |     |          |        |

| Resistance                                         |                                                                                  |     | 100      | Ω      |

| Capacitance                                        |                                                                                  |     | 0.4      | pF     |

| Return Loss                                        | <2.7 GHz                                                                         |     | -4.3     | dB     |

|                                                    | 2.7 GHz to 3.8 GHz                                                               |     | -3.6     | dB     |

|                                                    | 3.8 GHz to 5.4 GHz                                                               |     | -2.9     | dB     |

| CLOCK INPUTS                                       | CLKINP and CLKINN                                                                |     |          |        |

| Differential Input Power                           |                                                                                  |     |          |        |

| Direct RF Clock                                    |                                                                                  |     | 0        | dBm    |

| CLK Synchronization Enabled                        |                                                                                  |     | 0        | dBm    |

| Differential Input Impedance <sup>1</sup>          |                                                                                  |     | 100//0.3 | Ω//pF  |

| Common-Mode Voltage                                | AC coupled                                                                       |     | 0.5      | V      |

| ADC CLOCK OUTPUTS                                  | ADCDRVP and ADCDRVN                                                              |     |          |        |

| Differential Output Voltage Magnitude <sup>2</sup> | 1.5 GHz                                                                          |     | 740      | mV p-p |

|                                                    | 2.0 GHz                                                                          |     | 690      | mV p-p |

|                                                    | 3 GHz                                                                            |     | 640      | mV p-p |

|                                                    | 6 GHz                                                                            |     | 490      | mV p-p |

| Differential Output Resistance                     |                                                                                  |     | 100      | Ω      |

| Common-Mode Voltage                                | AC coupled                                                                       |     | 0.5      | V      |

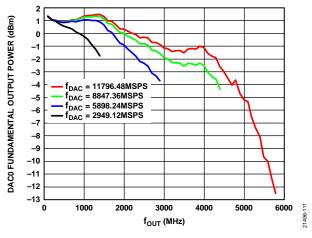

<sup>1</sup> The actual measured full-scale power is frequency dependent due to DAC sinc response, impedance mismatch loss, and balun insertion loss. <sup>2</sup> Measured with differential 100  $\Omega$  load and less than 2 mm of printed circuit board (PCB) trace from package ball.

#### DAC AND ADC SAMPLING SPECIFICATIONS

Nominal supplies. For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply. For the typical values,  $T_A$ = 25°C, unless otherwise noted.

| Table 3.                     |     |     |      |        |

|------------------------------|-----|-----|------|--------|

| Parameter                    | Min | Тур | Max  | Unit   |

| DAC UPDATE RATE <sup>1</sup> |     |     |      |        |

| Minimum                      |     |     | 2.9  | GSPS   |

| Maximum                      | 12  |     |      | GSPS   |

| ADC SAMPLE RATE <sup>1</sup> |     |     |      |        |

| Minimum                      |     |     | 1.45 | GSPS   |

| Maximum                      | 6   |     |      | GSPS   |

| Aperture Jitter <sup>2</sup> |     | 65  |      | fs rms |

<sup>1</sup> Pertains to the update rate of the DAC and ADC cores independent of datapath and JESD mode configuration.

<sup>2</sup> Measured using a signal-to-noise ratio (SNR) degradation method with the DAC disabled, clock divider = 1, ADC frequency (f<sub>ADC</sub>) = 6 GSPS, and input frequency (f<sub>IN</sub>) = 5.55 GHz.

#### **POWER CONSUMPTION**

Typical at nominal supplies and maximum at 5% supplies. DAC datapath with a complex I/Q data rate frequency ( $f_{IQ,DATA}$ ) = 375 MSPS and DAC frequency ( $f_{DAC}$ ) of 12 GSPS with interpolate by 32× with JRx mode of 16B (L = 8, M = 16). ADC datapath with  $f_{IQ,DATA}$  = 375 MSPS and  $f_{ADC}$  of 6 GSPS with decimate by 16× with JTx mode of 17B (L = 8, M = 16). For the minimum and maximum values,  $T_J$  = -40°C to +120°C. For the typical values,  $T_A$  = 25°C, unless otherwise noted.

See the UG-1578 user guide for further information on the JESDB or JESDC mode configurations and detailed settings referred to throughout this data sheet.

#### Table 4.

| Parameter                                                                 | Test Conditions/Comments                      | Min | Тур   | Max | Unit |

|---------------------------------------------------------------------------|-----------------------------------------------|-----|-------|-----|------|

| CURRENTS                                                                  |                                               |     |       |     |      |

| AVDD2 (I <sub>AVDD2</sub> )                                               | 2.0 V supply                                  |     | 190   |     |      |

| BVDD2 (I <sub>BVDD2</sub> ) + RVDD2 (I <sub>RVDD2</sub> )                 | 2.0 V supply                                  |     | 292   |     | mA   |

| AVDD2_PLL (I <sub>AVDD2_PLL</sub> ) + SVDD2_PLL (I <sub>SVDD2_PLL</sub> ) | 2.0 V supply                                  |     | 44    |     | mA   |

| Power Dissipation for 2 V Supplies                                        | 2.0 V supply total power dissipation          |     | 1.05  |     | W    |

| PLLCLKVDD1 (I <sub>PLLCLKVDD1</sub> )                                     | 1.0 V supply                                  |     | 43    |     | mA   |

| AVDD1 (I <sub>AVDD1</sub> ) + DCLKVDD1(I <sub>DCLKVDD1</sub> )            | 1.0 V supply                                  |     | 1541  |     | mA   |

| AVDD1_ADC (I <sub>AVDD1_ADC</sub> )                                       | 1.0 V supply                                  |     | 1700  |     | mA   |

| CLKVDD1 (I <sub>CLKVDD1</sub> )                                           | 1.0 V supply                                  |     | 96    |     | mA   |

| FVDD1 (I <sub>FVDD1</sub> )                                               | 1.0 V supply                                  |     | 72.5  |     | mA   |

| VDD1_NVG (Ivdd1_NVG)                                                      | 1.0 V supply                                  |     | 290   |     | mA   |

| DAVDD1 (I <sub>DAVDD1</sub> )                                             | 1.0 V supply                                  |     | 985   |     | mA   |

| DVDD1 (I <sub>DVDD1</sub> )                                               | 1.0 V supply                                  |     | 3555  |     | mA   |

| DVDD1_RT (I <sub>DVDD1_RT</sub> )                                         | 1.0 V supply                                  |     | 461   |     | mA   |

| SVDD1 (I <sub>SVDD1</sub> ) + SVDD1_PLL (I <sub>SVDD1_PLL</sub> )         | 1.0 V supply                                  |     | 1626  |     | mA   |

| Power Dissipation for 1 V Supplies                                        | 1.0 V supply total power dissipation          |     | 10.4  |     | W    |

| DVDD1P8 (I <sub>DVDD1P8</sub> )                                           | 1.8 V supply                                  |     | 6.8   |     | mA   |

| Total Power Dissipation                                                   | Total power dissipation of 2 and 1 V supplies |     | 11.45 |     | W    |

#### **CLOCK INPUT AND PHASE-LOCKED LOOP (PLL) FREQUENCY SPECIFICATIONS**

For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply, unless otherwise noted.

| Table 5.                                                 |                              |      |     |      |      |

|----------------------------------------------------------|------------------------------|------|-----|------|------|

| Parameter                                                | Test Conditions/Comments     | Min  | Тур | Max  | Unit |

| PLL VOLTAGE CONTROLLED OSCILLATOR (VCO) FREQUENCY RANGES |                              |      |     |      |      |

| VCO Output                                               |                              |      |     |      |      |

| Divide by 1                                              |                              | 6    |     | 12   | GSPS |

| Divide by 2                                              |                              | 3    |     | 6    | GSPS |

| Divide by 4                                              |                              | 1.5  |     | 3    | GSPS |

| PHASE FREQUENCY DETECT INPUT FREQUENCY RANGES            |                              | 25   |     | 750  | MHz  |

| CLOCK INPUTS (CLKINP, CLKINN) FREQUENCY RANGES           |                              |      |     |      |      |

| PLL Off                                                  |                              | 1.45 |     | 12   | GHz  |

| PLL On                                                   | M divider set to divide by 1 | 25   |     | 750  | MHz  |

|                                                          | M divider set to divide by 2 | 50   |     | 1500 | MHz  |

|                                                          | M divider set to divide by 3 | 75   |     | 2250 | MHz  |

|                                                          | M divider set to divide by 4 | 100  |     | 3000 | MHz  |

#### INPUT AND OUTPUT DATA RATES AND SIGNAL BANDWIDTH SPECIFICATIONS

For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply, unless otherwise noted.

| Parameter <sup>1</sup>                                        | Test Conditions/Comments                                                                                                        | Min  | Тур | Max    | Unit |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|-----|--------|------|

| DATA RATE PER INPUT CHANNEL                                   |                                                                                                                                 |      |     |        |      |

|                                                               | Channel datapaths bypassed (1× interpolation),<br>single DAC mode only, 16-bit resolution<br>(JR mode = 19C)                    |      |     | 12,000 | MSPS |

|                                                               | Channel datapaths bypassed (1× interpolation),<br>dual DAC or dual ADC, 16-bit resolution<br>(JRxmode = 18C and JTx mode = 28C) |      |     | 6000   | MSPS |

|                                                               | Channel datapaths bypassed (1× interpolation),<br>quad DAC mode , 12-bit resolution (JRx mode =<br>35C)                         |      |     | 4000   | MSPS |

|                                                               | 1 complex channel enabled, 16-bit resolution<br>(JRx mode = 18C and JTx mode = 19C)                                             |      |     | 6000   | MSPS |

|                                                               | 2 complex channels enabled, 12-bit resolution<br>(JRx mode = 23C and JTx mode = 27C)                                            |      |     | 4000   | MSPS |

|                                                               | 4 complex channels enabled, 12-bit resolution<br>(JRx mode = 24C and JTx mode = 26C)                                            |      |     | 2000   | MSPS |

|                                                               | 8 complex channels enabled, 16-bit resolution<br>(JRx mode = 16C and JTx mode = 16C)                                            |      |     | 750    | MSPS |

| COMPLEX SIGNAL BANDWIDTH PER CHANNEL                          |                                                                                                                                 |      |     |        |      |

|                                                               | 1 complex channel enabled (0.8 $\times$ data frequency (f <sub>DATA</sub> ))                                                    |      |     | 4800   | MHz  |

|                                                               | 2 complex channels enabled ( $0.8 \times f_{DATA}$ )                                                                            |      |     | 3200   | MHz  |

|                                                               | 4 complex channels enabled ( $0.8 \times f_{DATA}$ )                                                                            |      |     | 1600   | MHz  |

|                                                               | 8 complex channels enabled ( $0.8 \times f_{DATA}$ )                                                                            |      |     | 600    | MHz  |

| MAXIMUM NUMERICALLY CONTROLLED OSCILLATOR (NCO)<br>CLOCK RATE |                                                                                                                                 |      |     |        |      |

| Channel NCO                                                   |                                                                                                                                 |      |     | 1500   | MHz  |

| Main DAC NCO                                                  |                                                                                                                                 |      |     | 12     | GHz  |

| Main ADC NCO                                                  |                                                                                                                                 |      |     | 6      | GHz  |

| MAXIMUM NCO SHIFT FREQUENCY RANGE                             |                                                                                                                                 |      |     |        |      |

| Channel NCO                                                   | Channel summing node = $1.5 \text{ GHz}$ ,<br>channel interpolation rate > $1 \times$                                           | -750 |     | +750   | MHz  |

| Main DAC NCO                                                  | $f_{DAC} = 12 \text{ GHz}$ , main interpolation rate > 1×                                                                       | -6   |     | +6     | GHz  |

| Main ADC NCO                                                  | $f_{ADC} = 6 \text{ GHz}$ , main decimation rate > 1×                                                                           | -3   |     | +3     | GHz  |

| MAXIMUM FREQUENCY SPACING ACROSS INPUT CHANNELS               | Maximum NCO output frequency $	imes$ 0.8                                                                                        |      |     | 1200   | MHz  |

<sup>1</sup> The values listed for these parameters are the maximum possible when considering all JESD204B modes of operation. Some modes are more limiting, based on other parameters.

#### JESD204B AND JESD204C INTERFACE ELECTRICAL AND SPEED SPECIFICATIONS

Nominal supplies. For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply, and for the typical values,  $T_A = 25^{\circ}C$ , unless otherwise noted.

| Parameter                                       | Test Conditions/Comments                      | Min    | Тур               | Max            | Unit   |

|-------------------------------------------------|-----------------------------------------------|--------|-------------------|----------------|--------|

| JESD204B SERIAL INTERFACE RATE                  | Serial lane rate (bit repeat option disabled) | 8.11   |                   | 15.5           | Gbps   |

| Unit Interval                                   |                                               | 168.35 |                   | 64.5           | ps     |

| JESD204C SERIAL INTERFACE RATE                  | Serial lane rate (bit repeat option disabled) | 8.11   |                   | 16.22          | Gbps   |

| Unit Interval                                   |                                               | 123.3  |                   | 61.65          | ps     |

| JESD204x DATA INPUTS                            | SERDINx $\pm$ , where x = 0 to 7              |        |                   |                |        |

| Differential Voltage, RVDIFF                    |                                               |        | 800               |                | mV p-p |

| Differential Impedance, ZRDIFF                  | At dc                                         |        | 98                |                | Ω      |

| Termination Voltage, V $_{\mathrm{TT}}$         | AC-coupled                                    |        | 0.97              |                | V      |

| JESD204x DATA OUTPUTS                           | SERDOUTx±, where x = 0 to 7                   |        |                   |                |        |

| Logic Compliance                                |                                               |        | JESD204B/JESD20   | 4C complia     | nt     |

| Differential Output Voltage                     | Maximum strength                              |        | 675               |                | mV p-p |

| Differential Termination Impedance              |                                               | 80     | 108               | 120            | Ω      |

| Rise Time, t <sub>R</sub>                       | 20% to 80% into 100 Ω load                    |        | 18                |                | ps     |

| Fall Time, t⊧                                   | 20% to 80% into 100 Ω load                    | 18     |                   |                | ps     |

| SYSREFP AND SYSREFN INPUTS                      |                                               |        |                   |                |        |

| Logic Compliance                                |                                               |        | LVDS/LVF          | PECL1          | •      |

| Differential Input Voltage                      |                                               |        | 0.7               | 1.9            | V р-р  |

| Input Common-Mode Voltage Range                 | DC-coupled                                    |        | 0.675             | 2              | V      |

| Input Reference, R <sub>IN</sub> (Differential) |                                               |        | 100               |                | Ω      |

| Input Capacitance (Differential)                |                                               |        | 1                 |                | pF     |

| SYNCxOUTB± OUTPUTS <sup>2</sup>                 | Where $x = 0$ or 1                            |        |                   |                |        |

| Output Differential Voltage, V <sub>OD</sub>    | Driving 100 $\Omega$ differential load        |        | 400               |                | mV     |

| Output Offset Voltage, Vos                      |                                               |        | DVDD1P8/2         |                | V      |

| SYNCxOUTB+                                      | CMOS output option                            |        | Refer to CMOS pir | n specificatio | on     |

| SYNCxINB± INPUT <sup>2</sup>                    | Where $x = 0$ or 1                            |        |                   |                |        |

| Logic Compliance                                |                                               |        | LVDS              | 5              | •      |

| Differential Input Voltage                      |                                               |        | 0.7               | 1.9            | mV p-p |

| Input Common-Mode Voltage                       | DC-coupled                                    |        | 0.675             | 2              | V      |

| R <sub>IN</sub> (Differential)                  | 18                                            |        | 18                |                | kΩ     |

| Input Capacitance (Differential)                | 1                                             |        | 1                 |                | pF     |

| SYNCxINB+ INPUT                                 | CMOS input option                             |        | Refer to CMOS pir | n specificatio | on     |

<sup>1</sup> LVDS means low voltage differential signaling and LVPECL means low voltage positive/pseudo emitter-coupled logic. <sup>2</sup> IEEE 1596.3 Standard LVDS compatible.

#### **CMOS PIN SPECIFICATIONS**

Nominal supplies. For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and DVDD1P8 = 2.0 V ± 5%, and for the typical values,  $T_A = 25^{\circ}$ C, unless otherwise noted.

#### Table 8.

| Parameter         | Symbol          | Test Conditions/Comments                                           | Min            | Тур | Max                         | Unit |

|-------------------|-----------------|--------------------------------------------------------------------|----------------|-----|-----------------------------|------|

| INPUTS            |                 | SDIO, SCLK, CSB, RESETB, RXEN0, RXEN1,                             |                |     |                             |      |

|                   |                 | TXEN0, TXEN1, SYNC0INB±, SYNC1INB±,                                |                |     |                             |      |

|                   |                 | and GPIOx                                                          |                |     |                             |      |

| Logic 1 Voltage   | VIH             |                                                                    | 0.70 × DVDD1P8 |     |                             | V    |

| Logic 0 Voltage   | VIL             |                                                                    |                |     | $0.3 \times \text{DVDD1P8}$ | V    |

| Input Resistance  |                 |                                                                    |                | 30  |                             | kΩ   |

| OUTPUTS           |                 | SDIO, SDO, GPIOx, ADCx_FDx, SYNC0INB±,<br>and SYNC1INB±, 4 mA load |                |     |                             |      |

| Logic 1 Voltage   | V <sub>OH</sub> |                                                                    | DVDD1P8 - 0.45 |     |                             | V    |

| Logic 0 Voltage   | V <sub>OL</sub> |                                                                    |                |     | 0.45                        | V    |

| INTERRUPT OUTPUTS |                 | IRQB_0 and IRQB_1, pull-up resistor of 5 k $\Omega$                |                |     |                             |      |

| Logic 1 Voltage   | V <sub>OH</sub> |                                                                    | 1.45           |     |                             | V    |

| Logic 0 Voltage   | Vol             |                                                                    |                |     | 0.35                        | V    |

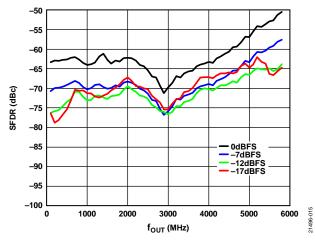

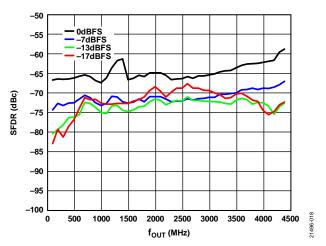

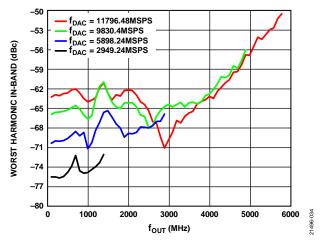

#### DAC AC SPECIFICATIONS

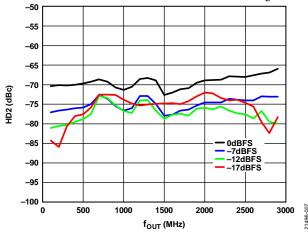

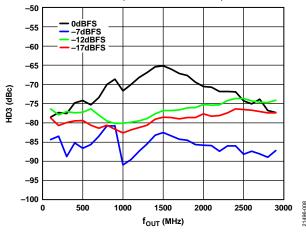

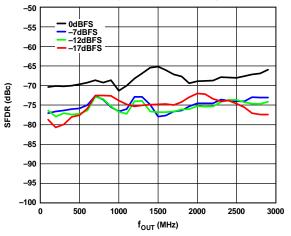

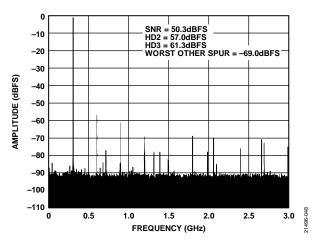

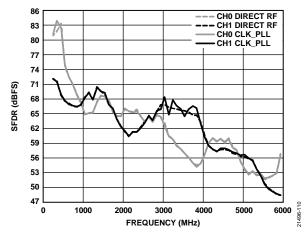

Nominal supplies with  $T_A = 25^{\circ}$ C.  $f_{IQ\_DATA} = 1500$  MSPS. Specifications represent the average of all four DAC channels with the DAC  $I_{OUTFS} = 26$  mA and ADC powered down, unless otherwise noted.

| Table 9. Parameter                       | Test Conditions/Comments                          | Min | Тур    | Мах | Unit |

|------------------------------------------|---------------------------------------------------|-----|--------|-----|------|

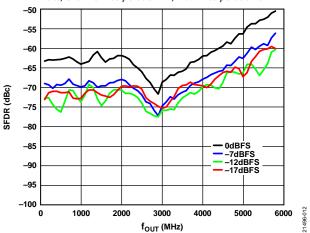

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)       |                                                   |     |        | mux | Unit |

| Single-Tone, $f_{DAC} = 12$ GSPS         | -7 dBFS, shuffle enabled                          |     |        |     |      |

| Output Frequency ( $f_{OUT}$ ) = 100 MHz |                                                   |     | -70.7  |     | dBc  |

| $f_{OUT} = 500 \text{ MHz}$              |                                                   |     | -69.2  |     | dBc  |

| fout = 900 MHz                           |                                                   |     | -69.7  |     | dBc  |

| f <sub>out</sub> = 1900 MHz              |                                                   |     | -68.5  |     | dBc  |

| fout = 2600 MHz                          |                                                   |     | -73.1  |     | dBc  |

| f <sub>OUT</sub> = 3700 MHz              |                                                   |     | -70    |     | dBc  |

| fout = 4500 MHz                          |                                                   |     | -66.5  |     | dBc  |

| Single-Tone, f <sub>DAC</sub> = 9 GSPS   | -7 dBFS, shuffle enabled                          |     |        |     |      |

| f <sub>OUT</sub> = 100 MHz               |                                                   |     | -74.4  |     | dBc  |

| f <sub>OUT</sub> = 500 MHz               |                                                   |     | -72.5  |     | dBc  |

| f <sub>OUT</sub> = 900 MHz               |                                                   |     | -72.50 |     | dBc  |

| f <sub>out</sub> = 1900 MHz              |                                                   |     | -71.0  |     | dBc  |

| fout = 2600 MHz                          |                                                   |     | -71.5  |     | dBc  |

| fout = 3700 MHz                          |                                                   |     | -69.1  |     | dBc  |

| Single-Tone, f <sub>DAC</sub> = 6 GSPS   | -7 dBFS, shuffle enabled                          |     |        |     |      |

| $f_{OUT} = 100 \text{ MHz}$              |                                                   |     | -77    |     | dBc  |

| fout = 500 MHz                           |                                                   |     | -75.8  |     | dBc  |

| fout = 900 MHz                           |                                                   |     | -75.3  |     | dBc  |

| f <sub>OUT</sub> = 1900 MHz              |                                                   |     | -75.3  |     | dBc  |

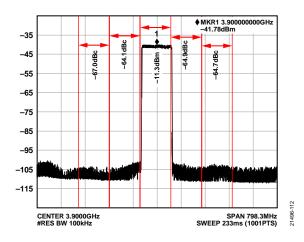

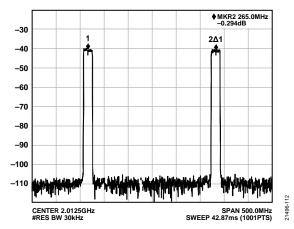

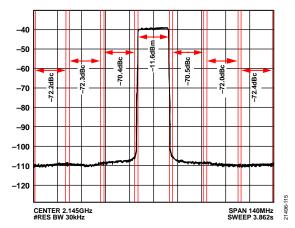

| SINGLE-BAND APPLICATION, BAND 3          | f <sub>DAC</sub> =9 GSPS, 500 MHz reference clock |     |        |     |      |

| Windowed SFDR Nonharmonics               | -7 dBFS, shuffle enabled                          |     |        |     |      |

| In Band                                  | 1842.5 MHz ± 37.5 MHz pass-band region            |     | -95.5  |     | dBc  |

| DPD Band                                 | 1842.5 MHz, ± 200 MHz pass-band region            |     | -80.3  |     | dBc  |

| Parameter                                                                                   | Test Conditions/Comments                       | Min Typ | Мах | Unit     |

|---------------------------------------------------------------------------------------------|------------------------------------------------|---------|-----|----------|

| ADJACENT CHANNEL LEAKAGE RATIO                                                              |                                                |         |     |          |

| Single Carrier 20 MHz LTE Downlink Test Vector                                              | –1 dBFS digital back off, 256QAM               |         |     |          |

| $f_{DAC} = 12 \text{ GSPS}$                                                                 | f <sub>OUT</sub> = 1840 MHz                    | 77.3    |     | dBc      |

|                                                                                             | f <sub>оυт</sub> = 2650 MHz                    | 76.3    |     | dBc      |

|                                                                                             | fouт = 3500 MHz                                | 73.3    |     | dBc      |

| $f_{DAC} = 9 \text{ GSPS}$                                                                  | f <sub>OUT</sub> = 1900 MHz                    | 77.0    |     | dBc      |

|                                                                                             | f <sub>out</sub> = 2650 MHz                    | 77.1    |     | dBc      |

| $f_{DAC} = 6 \text{ GSPS}$                                                                  | $f_{OUT} = 750 \text{ MHz}$                    | 78.8    |     | dBc      |

|                                                                                             | four = 1840 MHz                                | 77.3    |     | dBc      |

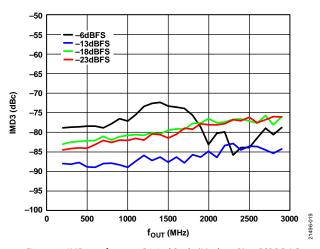

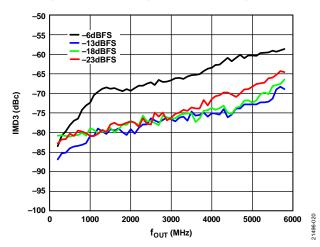

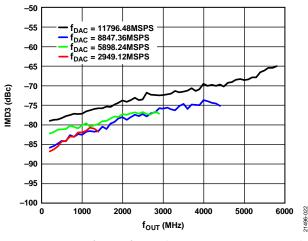

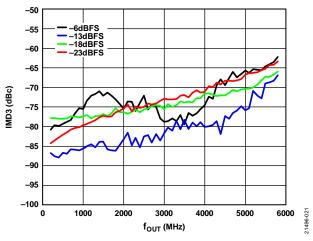

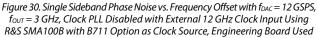

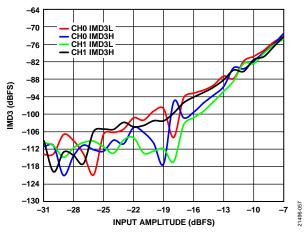

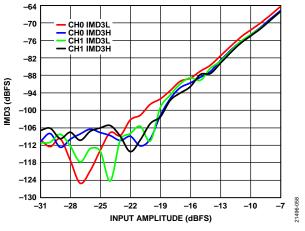

| THIRD-ORDER INTERMODULATION DISTORTION (IMD3)                                               | Two tone test, –6 dBFS per tone, 1 MHz spacing |         |     |          |

| $f_{DAC} = 12 \text{ GSPS}$                                                                 | $f_{OUT} = 1900 \text{ MHz}$                   | -74.5   |     | dBc      |

|                                                                                             | $f_{OUT} = 2600 \text{ MHz}$                   | -75.5   |     | dBc      |

|                                                                                             | $f_{OUT} = 3700 \text{ MHz}$                   | -77     |     | dBc      |

| $f_{DAC} = 9 \text{ GSPS}$                                                                  | $f_{OUT} = 1900 \text{ MHz}$                   | -83     |     | dBc      |

|                                                                                             | $f_{OUT} = 2600 \text{ MHz}$                   | -86     |     | dBc      |

| $f_{DAC} = 6 \text{ GSPS}$                                                                  | $f_{0,T} = 900 \text{ MHz}$                    | -88.4   |     | dBc      |

| IDAC - 0 CDI 5                                                                              | $f_{OUT} = 1900 \text{ MHz}$                   | -86.3   |     | dBc      |

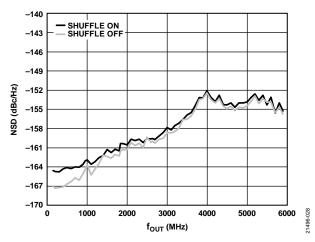

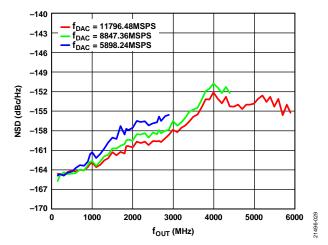

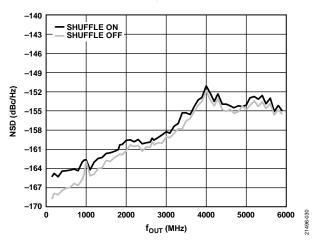

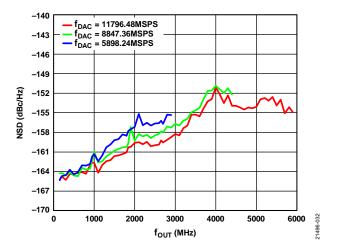

| NOISE SPECTRAL DENSITY (NSD)                                                                | 0 dBFS, NSD measurement taken at               | -00.5   |     | ubc      |

| NOISE SPECTRAL DENSITY (NSD)                                                                | 10% away from $f_{OUT}$ , shuffle off          |         |     |          |

| Single-Tone, f <sub>DAC</sub> = 12 GSPS                                                     |                                                |         |     |          |

| $f_{OUT} = 150 \text{ MHz}$                                                                 |                                                | -168    |     | dBc/Hz   |

| $f_{OUT} = 500 \text{ MHz}$                                                                 |                                                | -166    | 7   | dBc/Hz   |

| $f_{OUT} = 950 \text{ MHz}$                                                                 |                                                | -164    |     | dBc/Hz   |

| $f_{OUT} = 1840 \text{ MHz}$                                                                |                                                | -161    |     | dBc/Hz   |

| $f_{OUT} = 2650 \text{ MHz}$                                                                |                                                | -160    |     | dBc/Hz   |

| $f_{OUT} = 3700 \text{ MHz}$                                                                |                                                | -155    |     | dBc/Hz   |

| $f_{OUT} = 4500 \text{ MHz}$                                                                |                                                | -154    |     | dBc/Hz   |

|                                                                                             |                                                | -154    | 2   | UDC/ HZ  |

| Single-Tone, $f_{DAC} = 9$ GSPS                                                             |                                                | 160     |     | dD a / U |

| $f_{OUT} = 150 \text{ MHz}$                                                                 |                                                | -168    |     | dBc/Hz   |

| $f_{OUT} = 500 \text{ MHz}$                                                                 |                                                | -166    |     | dBc/Hz   |

| $f_{OUT} = 950 \text{ MHz}$                                                                 |                                                | -164    | 2   | dBc/Hz   |

| $f_{OUT} = 1840 \text{ MHz}$                                                                |                                                | -160    |     | dBc/Hz   |

| $f_{OUT} = 2650 \text{ MHz}$                                                                |                                                | -158    |     | dBc/Hz   |

| $f_{OUT} = 3700 \text{ MHz}$                                                                |                                                | -153    | 5   | dBc/Hz   |

| Single-Tone, $f_{DAC} = 6$ GSPS                                                             |                                                | 1.60    |     | 10 (11   |

| $f_{OUT} = 150 \text{ MHz}$                                                                 |                                                | -168    |     | dBc/Hz   |

| $f_{OUT} = 500 \text{ MHz}$                                                                 |                                                | -165    |     | dBc/Hz   |

| $f_{OUT} = 950 \text{ MHz}$                                                                 |                                                | -163    |     | dBc/Hz   |

| f <sub>OUT</sub> = 1840 MHz                                                                 |                                                | -159    |     | dBc/Hz   |

| f <sub>out</sub> = 2650 MHz                                                                 |                                                | -156    | .8  | dBc/Hz   |

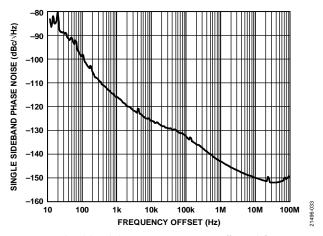

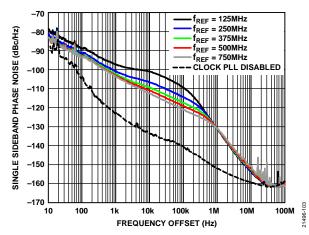

| SINGLE SIDEBAND PHASE NOISE OFFSET (PLL DISABLED)                                           | Direct RF clock input at 7 dBm                 |         |     |          |

| $f_{OUT} = 3 \text{ GHz}, f_{DAC} = 12 \text{ GSPS}, \text{CLKINx Frequency} (f_{CLKIN}) =$ | R&S SMA100B B711 option                        |         |     |          |

| 12 GHz                                                                                      |                                                |         |     | 10 // .  |

| 1 kHz                                                                                       |                                                | -119    |     | dBc/Hz   |

| 10 kHz                                                                                      |                                                | -129    |     | dBc/Hz   |

| 100 kHz                                                                                     |                                                | -136    |     | dBc/Hz   |

| 600 kHz                                                                                     |                                                | -146    |     | dBc/Hz   |

| 1.2 MHz                                                                                     |                                                | -148    |     | dBc/Hz   |

| 1.8 MHz                                                                                     |                                                | -150    |     | dBc/Hz   |

| 6 MHz                                                                                       |                                                | -154    |     | dBc/Hz   |

| Parameter                                                                           | Test Conditions/Comments                                                                                                                                         | Min | Тур  | Max | Unit   |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| SINGLE SIDEBAND PHASE NOISE OFFSET (PLL ENABLED)                                    | Loop filter component values include<br>$C1 = 22 \text{ nF}, R1 = 226 \Omega, C2 = 2.2 \text{ nF},$<br>C3 = 33  nF, and phase detector frequency (PFD) = 500 MHz |     |      |     |        |

| $f_{OUT} = 1.8 \text{ GHz}, f_{DAC} = 12 \text{ GSPS}, f_{CLKIN} = 0.5 \text{ GHz}$ |                                                                                                                                                                  |     |      |     |        |

| 1 kHz                                                                               |                                                                                                                                                                  |     | -103 |     | dBc/Hz |

| 10 kHz                                                                              |                                                                                                                                                                  |     | -111 |     | dBc/Hz |

| 100 kHz                                                                             |                                                                                                                                                                  |     | -119 |     | dBc/Hz |

| 600 kHz                                                                             |                                                                                                                                                                  |     | -127 |     | dBc/Hz |

| 1.2 MHz                                                                             |                                                                                                                                                                  |     | -132 |     | dBc/Hz |

| 1.8 MHz                                                                             |                                                                                                                                                                  |     | -137 |     | dBc/Hz |

| 6 MHz                                                                               |                                                                                                                                                                  |     | -148 |     | dBc/Hz |

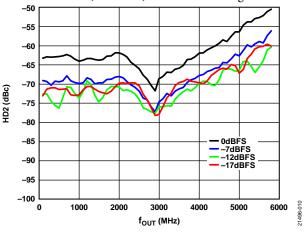

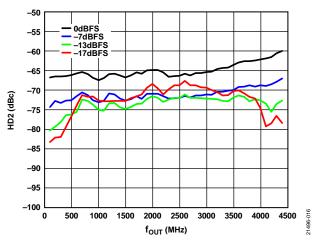

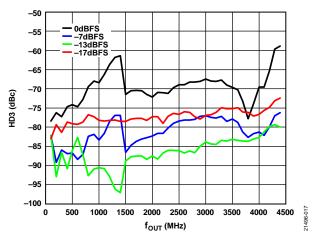

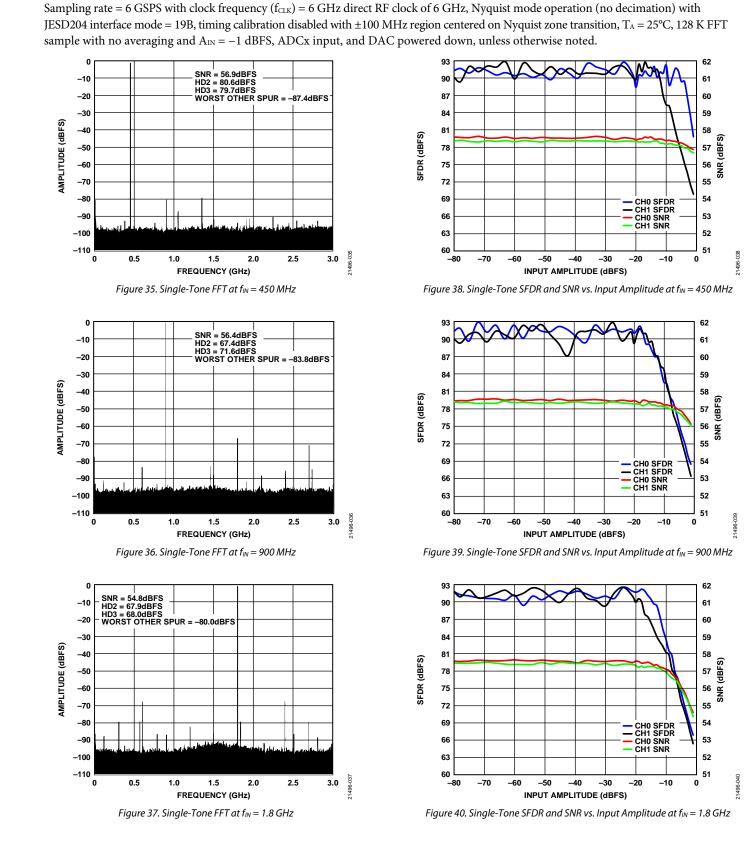

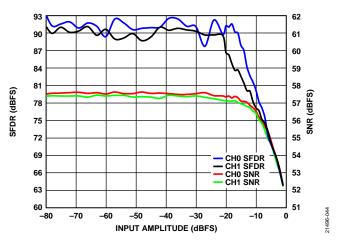

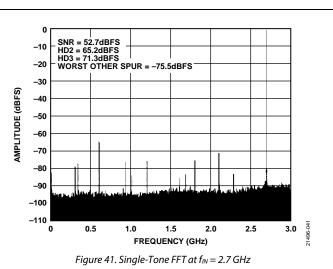

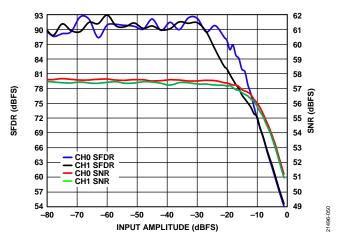

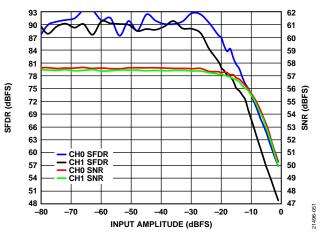

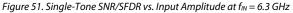

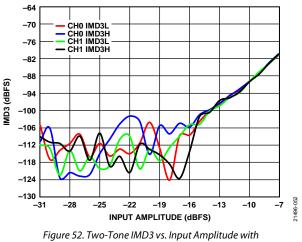

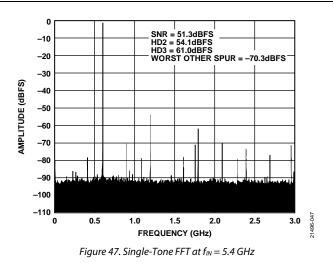

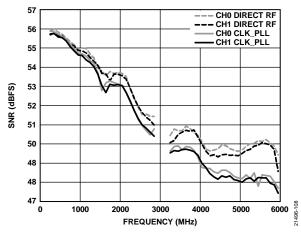

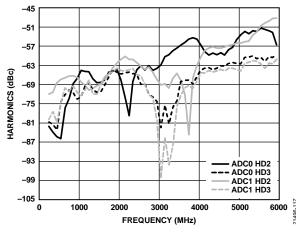

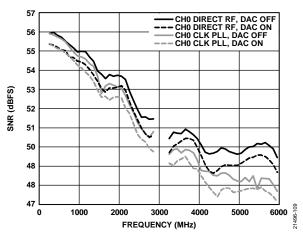

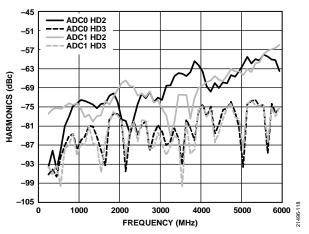

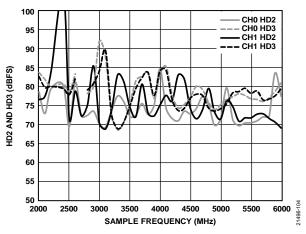

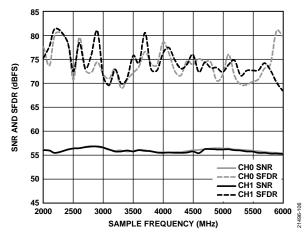

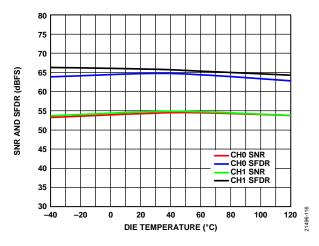

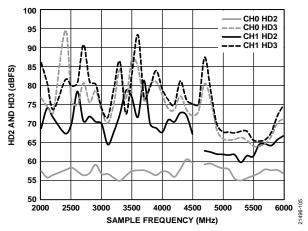

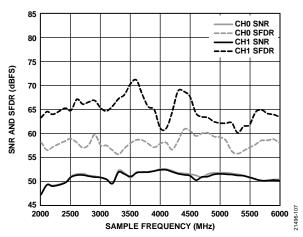

#### ADC AC SPECIFICATIONS

Nominal supplies with  $T_A = 25^{\circ}$ C. Input amplitude  $(A_{IN}) = -1$  dBFS, full bandwidth (no decimation) with dual link JTx mode of 13C. Specifications represent worst measured of any ADC channel with DACs powered down. See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for definitions and for details on how these tests were completed.

| Table 10.                                    |             |         |

|----------------------------------------------|-------------|---------|

| Parameter                                    | Min Typ Max | Unit    |

| NOISE DENSITY <sup>1</sup>                   | -153        | dBFS/Hz |

| NOISE FIGURE <sup>2</sup>                    | 25.3        | dB      |

| SIGNAL-TO-NOISE RATIO (SNR)                  |             |         |

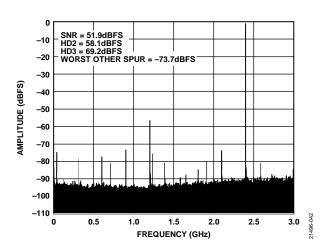

| f <sub>IN</sub> = 253 MHz                    | 56.7        | dBFS    |

| $f_{IN} = 450 \text{ MHz}$                   | 56.9        | dBFS    |

| f <sub>IN</sub> = 900 MHz                    | 56.2        | dBFS    |

| f <sub>IN</sub> = 1800 MHz                   | 54.7        | dBFS    |

| f <sub>IN</sub> = 2700 MHz                   | 52.4        | dBFS    |

| f <sub>IN</sub> = 3600 MHz                   | 51.8        | dBFS    |

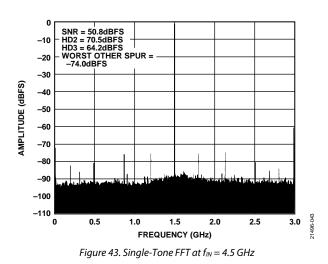

| f <sub>IN</sub> = 4500 MHz                   | 50.4        | dBFS    |

| f <sub>IN</sub> = 5400 MHz                   | 51.0        | dBFS    |

| SIGNAL-TO-NOISE-AND-DISTORTION (SINAD) RATIO |             |         |

| f <sub>IN</sub> = 253 MHz                    | 56.6        | dBFS    |

| $f_{IN} = 450 \text{ MHz}$                   | 56.6        | dBFS    |

| $f_{IN} = 900 \text{ MHz}$                   | 55.7        | dBFS    |

| f <sub>IN</sub> = 1800 MHz                   | 53.9        | dBFS    |

| f <sub>IN</sub> = 2700 MHz                   | 52.0        | dBFS    |

| f <sub>IN</sub> = 3600 MHz                   | 51.3        | dBFS    |

| f <sub>IN</sub> = 4500 MHz                   | 49.6        | dBFS    |

| f <sub>IN</sub> = 5400 MHz                   | 48.9        | dBFS    |

| EFFECTIVE NUMBER OF BITS (ENOB)              |             |         |

| f <sub>IN</sub> = 253 MHz                    | 9.1         | Bits    |

| $f_{IN} = 450 \text{ MHz}$                   | 9.1         | Bits    |

| f <sub>IN</sub> = 900 MHz                    | 9           | Bits    |

| f <sub>IN</sub> = 1800 MHz                   | 8.7         | Bits    |

| f <sub>IN</sub> = 2700 MHz                   | 8.3         | Bits    |

| f <sub>IN</sub> = 3600 MHz                   | 8.2         | Bits    |

| f <sub>IN</sub> = 4500 MHz                   | 7.9         | Bits    |

| f <sub>IN</sub> = 5400 MHz                   | 7.8         | Bits    |

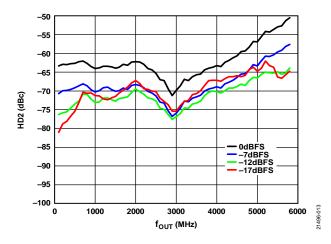

| WORST HD2                                    |             |         |

| f <sub>IN</sub> = 253 MHz                    | -72.1       | dBFS    |

| $f_{IN} = 450 \text{ MHz}$                   | -68.9       | dBFS    |

| $f_{IN} = 900 \text{ MHz}$                   | -67.1       | dBFS    |

| f <sub>IN</sub> = 1800 MHz                   | -64.6       | dBFS    |

| $f_{IN} = 2700 \text{ MHz}$                  | -65.2       | dBFS    |

| f <sub>IN</sub> = 3600 MHz                   | -58.1       | dBFS    |

| $f_{IN} = 4500 \text{ MHz}$                  | -65         | dBFS    |

| $f_{\rm IN} = 5400 \rm MHz$                  | -54.1       | dBFS    |

# AD9082

| Parameter                                                                                  | Min | Тур   | Max | Unit |

|--------------------------------------------------------------------------------------------|-----|-------|-----|------|

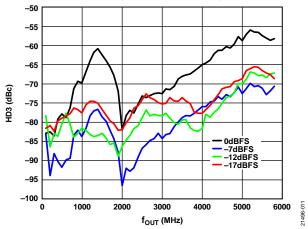

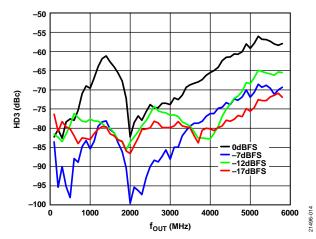

| WORST HD3                                                                                  |     |       |     |      |

| f <sub>IN</sub> = 253 MHz                                                                  |     | -80.0 |     | dBFS |

| $f_{IN} = 450 \text{ MHz}$                                                                 |     | -78.3 |     | dBFS |

| f <sub>IN</sub> = 900 MHz                                                                  |     | -70.8 |     | dBFS |

| f <sub>IN</sub> = 1800 MHz                                                                 |     | -66   |     | dBFS |

| f <sub>IN</sub> = 2700 MHz                                                                 |     | -70.8 |     | dBFS |

| f <sub>IN</sub> = 3600 MHz                                                                 |     | -69.2 |     | dBFS |

| $f_{IN} = 4500 \text{ MHz}$                                                                |     | -64.3 |     | dBFS |

| f <sub>IN</sub> = 5400 MHz                                                                 |     | -62   |     | dBFS |

| WORST OTHER, EXCLUDING HD2 OR HD3 HARMONIC                                                 |     |       |     |      |

| f <sub>IN</sub> = 253 MHz                                                                  |     | -85.3 |     | dBFS |

| f <sub>IN</sub> = 450 MHz                                                                  |     | -81.4 |     | dBFS |

| f <sub>IN</sub> = 900 MHz                                                                  |     | -76.5 |     | dBFS |

| f <sub>IN</sub> = 1800 MHz                                                                 |     | -72.1 |     | dBFS |

| f <sub>IN</sub> = 2700 MHz                                                                 |     | -68.5 |     | dBFS |

| f <sub>IN</sub> = 3600 MHz                                                                 |     | -65.9 |     | dBFS |

| f <sub>IN</sub> = 4500 MHz                                                                 |     | -64.2 |     | dBFS |

| f <sub>IN</sub> = 5400 MHz                                                                 |     | -62.7 |     | dBFS |

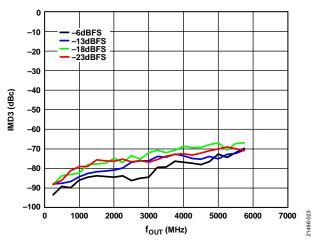

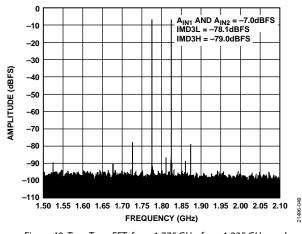

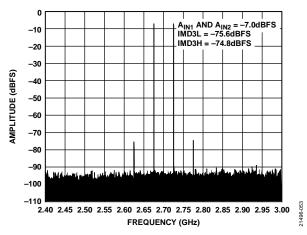

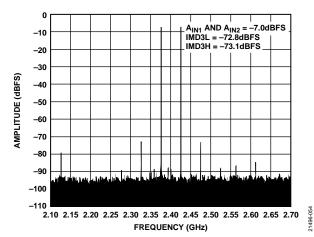

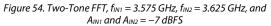

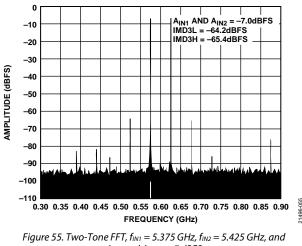

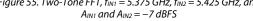

| TWO-TONE IMD3, Input Amplitude 1 ( $A_{IN1}$ ) = Input Amplitude 2 ( $A_{IN2}$ ) = -7 dBFS |     |       |     |      |

| Input Frequency 1 ( $f_{IN1}$ ) = 890 MHz, Input Frequency 2 ( $f_{IN2}$ ) = 910 MHz       |     |       |     |      |

| $f_{IN1} = 1780 \text{ MHz}, f_{IN2} = 1820 \text{ MHz}$                                   |     | -78.9 |     | dBFS |

| $f_{IN1} = 2680 \text{ MHz}, f_{IN2} = 2720 \text{ MHz}$                                   |     | -75   |     | dBFS |

| $f_{IN1} = 3560 \text{ MHz}, f_{IN2} = 3640 \text{ MHz}$                                   |     | -73.2 |     | dBFS |

| $f_{IN1} = 5360 \text{ MHz}, f_{IN2} = 5440 \text{ MHz}$                                   |     | -64.2 |     | dBFS |

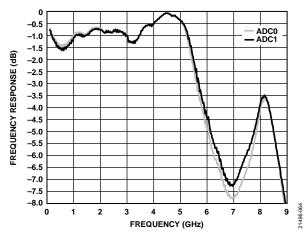

| ANALOG BANDWIDTH <sup>3</sup>                                                              |     | 8     |     | GHz  |

<sup>1</sup> Noise density is measured at a low analog amplitude and/or frequency where timing jitter does not degrade noise floor.

<sup>2</sup> Noise figure is based on a nominal full-scale input power of 4.5 dBm with an input span of 1.5 V p-p and  $R_{IN} = 100 \Omega$ .

<sup>3</sup> Analog input bandwidth is the bandwidth of operation in which the full-scale input frequency response rolls off by –3 dB based on a de-embedded model of the ADC extracted from the measured frequency response on evaluation board. This bandwidth requires optimized matching network to achieve this upper bandwidth.

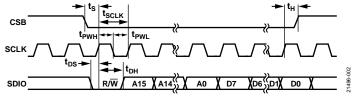

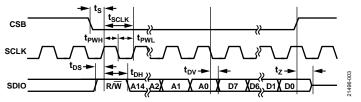

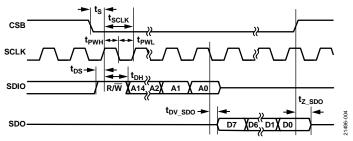

#### TIMING SPECIFICATIONS

For the minimum and maximum values,  $T_J = -40^{\circ}$ C to  $+120^{\circ}$ C and  $\pm 5\%$  of nominal supply, unless otherwise noted.

| Parameter                                   | Symbol                                  | <b>Test Conditions/Comments</b> | Min | Тур | Max | Unit |

|---------------------------------------------|-----------------------------------------|---------------------------------|-----|-----|-----|------|

| SERIAL PORT INTERFACE (SPI) WRITE OPERATION |                                         |                                 |     |     |     |      |

| Maximum SCLK Clock Rate                     | f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> |                                 | 33  |     |     | MHz  |

| SCLK Clock High                             | <b>t</b> <sub>PWH</sub>                 | SCLK = 33 MHz                   | 5   |     |     | ns   |

| SCLK Clock Low                              | t <sub>PWL</sub>                        | SCLK = 33 MHz                   | 5   |     |     | ns   |

| SDIO to SCLK Setup Time                     | t <sub>DS</sub>                         |                                 | 4   |     |     | ns   |

| SCLK to SDIO Hold Time                      | t <sub>DH</sub>                         |                                 | 4   |     |     | ns   |

| CSB to SCLK Setup Time                      | ts                                      |                                 | 4   |     |     | ns   |

| SCLK to CSB Hold Time                       | tн                                      |                                 | 4   |     |     | ps   |

| Parameter                          | Symbol                                  | Test Conditions/Comments | Min | Тур | Max | Unit |

|------------------------------------|-----------------------------------------|--------------------------|-----|-----|-----|------|

| SPI READ OPERATION                 |                                         |                          |     |     |     |      |

| Maximum SCLK Clock Rate            | f <sub>SCLK</sub> , 1/t <sub>SCLK</sub> |                          | 8   |     |     | MHz  |

| SCLK Clock High                    | tpwh                                    |                          | 50  |     |     | ns   |

| SCLK Clock Low                     | t <sub>PWL</sub>                        |                          | 50  |     |     | ns   |

| SDIO to SCLK Setup Time            | t <sub>DS</sub>                         |                          | 4   |     |     | ns   |

| SCLK to SDIO Hold Time             | t <sub>DH</sub>                         |                          | 4   |     |     | ns   |

| CSB to SCLK Setup Time             | ts                                      |                          | 4   |     |     | ns   |

| SCLK to SDIO Data Valid Time       | t <sub>DV</sub>                         |                          | 20  |     |     | ns   |

| SCLK to SDO Data Valid Time        | t <sub>DV_SDO</sub>                     |                          | 20  |     |     | ns   |

| CSB to SDIO Output Valid to High-Z | tz                                      |                          | 20  |     |     | ns   |

| CSB to SDO Output Valid to High-Z  | t <sub>z_sdo</sub>                      |                          | 20  |     |     | ns   |

#### **Timing Diagrams**

Figure 2. Timing Diagram for 3-Wire Write Operation

Figure 3. Timing Diagram for 3-Wire Read Operation

Figure 4. Timing Diagram for 4-Wire Read Operation

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 12.

| .3 V  |

|-------|

|       |

|       |

| ).2 V |

| V     |

|       |

|       |

| V     |

|       |

|       |

|       |

|       |

|       |

|       |

| V     |

<sup>1</sup> Do not exceed this temperature for any duration of time when the device is powered.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **REFLOW PROFILE**

The AD9082 reflow profile is in accordance with the JEDEC JESD 20 criteria for Pb-free devices. The maximum reflow temperature is 260°C.

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. The use of appropriate thermal management techniques is recommended to ensure that the maximum  $T_J$  does not exceed the limits shown in Table 12.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{\text{JC}_{\text{TOP}}}$  is the junction to case, thermal resistance.

$\theta_{JB}$  is the junction to board, thermal resistance.

#### Table 13. Simulated Thermal Resistance<sup>1</sup>

| РСВ Туре            | Airflow Velocity<br>(m/sec) | Αιθ  | <b>θ</b> jc_top | Өјв | Unit |

|---------------------|-----------------------------|------|-----------------|-----|------|

| JEDEC 2s2p<br>Board | 0.0                         | 14.9 | 0.70            | 1.8 | °C/W |

<sup>1</sup> Thermal resistance values specified are simulated based on JEDEC specifications in compliance with JESD51-12 with the device power equal to 9 W.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

|   |        |       |               |                |            |              |               |                  | AD9<br>TOP<br>(Not to | VIEW              |                |                |            |           |               |               |           |           |

|---|--------|-------|---------------|----------------|------------|--------------|---------------|------------------|-----------------------|-------------------|----------------|----------------|------------|-----------|---------------|---------------|-----------|-----------|

|   | 1      | 2     | 3             | 4              | 5          | 6            | 7             | 8                | 9                     | 10                | 11             | 12             | 13         | 14        | 15            | 16            | 17        | 18        |

| A | GND    | AVDD2 | GND           | GND            | NC         | NC           | GND           | GND              | ADCON                 | ADC0P             | GND            | SYNC1INB-      | SYNCOINB-  | SERDOUT0- | SERDOUT0+     | SVDD1         | GND       | GND       |

| в | DACOP  | GND   | GND           | GND            | GND        | GND          | DNC           | VCM0             | GND                   | GND               | RVDD2          | SYNC1INB+      | SYNCOINB+  | GND       | GND           | SVDD1         | SERDOUT7- | SERDOUT7+ |

| с | DACON  | GND   | ADCDRVN       | ADCDRVP        | GND        | GND          | GND           | GND              | BVNN2                 | BVDD3             | GND            | RESETB         | DVDD1P8    | SERDOUT1- | SERDOUT1+     | SVDD1         | GND       | GND       |

| D | GND    | AVDD1 | AVDD1         | AVDD1          | GND        | FVDD1        | BVDD2         | VNN1             | GND                   | VDD1_<br>NVG      | ADC0_<br>SMON1 | ADC0_<br>SMON0 | RXEN1      | GND       | GND           | SVDD1         | SERDOUT6- | SERDOUT6+ |

| E | GND    | AVDD2 | AVDD1         | GND            | DAVDD1     | GND          | BVDD2         | VNN1             | NVG1_<br>OUT          | VNN1              | ADC1_<br>SMON1 | ADC1_<br>SMON0 | RXEN0      | SERDOUT2- | SERDOUT2+     | SVDD1         | GND       | GND       |

| F | DAC1N  | GND   | AVDD1         | GND            | DAVDD1     | GND          | GND           | GND              | DVDD1P8               | DVDD1             | ADC0_FD1       | ADC0_FD0       | SDIO       | GND       | GND           | SVDD1         | SERDOUT5- | SERDOUT5+ |

| G | DAC1P  | GND   | GND           | GND            | GND        | CLKVDD1      | AVDD1_<br>ADC | AVDD1_<br>ADC    | TMU_<br>REFN          | TMU_<br>REFP      | ADC1_FD1       | ADC1_FD0       | CSB        | SERDOUT3- | SERDOUT3+     | SVDD1         | GND       | GND       |

| н | GND    | AVDD2 | ISET          | DNC            | GND        | GND          | GND           | GND              | DVDD1                 | GND               | DVDD1          | GND            | SCLK       | GND       | GND           | SVDD1         | SERDOUT4- | SERDOUT4+ |

| J | CLKINP | GND   | VCO_<br>FINE  | VCO_<br>COARSE | PLLCLKVDD1 | DVDD1_<br>RT | DVDD1_<br>RT  | GND              | DVDD1                 | GND               | DVDD1          | GND            | SDO        | GND       | GND           | SVDD1_<br>PLL | GND       | GND       |

| к | CLKINN | GND   | VCO_<br>VREG  | VCO_<br>VCM    | DCLKVDD1   | DVDD1_<br>RT | DVDD1_<br>RT  | GND              | DVDD1                 | GND               | DVDD1          | GND            | GPIO9      | GND       | SVDD2_<br>PLL | SVDD1_<br>PLL | GND       | GND       |

| L | GND    | AVDD2 | AVDD2_<br>PLL | DNC            | GND        | GND          | GND           | GND              | DVDD1                 | GND               | DVDD1          | GND            | GPIO8      | GND       | DNC           | DNC           | SERDIN0-  | SERDIN0+  |

| м | DAC2P  | GND   | GND           | GND            | GND        | CLKVDD1      | AVDD1_<br>ADC | AVDD1_<br>ADC    | DVDD1                 | GND               | GPIO3          | GPIO1          | GPIO7      | SERDIN4-  | SERDIN4+      | SVDD1         | GND       | GND       |

| N | DAC2N  | GND   | AVDD1         | GND            | DAVDD1     | GND          | GND           | GND              | TDP                   | TDN               | GPIO2          | GPI00          | GPIO6      | GND       | GND           | SVDD1         | SERDIN1-  | SERDIN1+  |

| Ρ | GND    | AVDD2 | AVDD1         | GND            | DAVDD1     | GND          | BVDD2         | VNN1             | NVG1_<br>OUT          | VNN1              | GPIO4          | IRQB_0         | TXEN0      | SERDIN7-  | SERDIN7+      | SVDD1         | GND       | GND       |

| R | GND    | AVDD1 | AVDD1         | AVDD1          | GND        | FVDD1        | BVDD2         | VNN1             | GND                   | VDD1_<br>NVG      | GPIO5          | IRQB_1         | TXEN1      | GND       | GND           | SVDD1         | SERDIN2-  | SERDIN2+  |

| т | DAC3N  | GND   | SYSREFN       | SYSREFP        | GND        | GND          | GND           | GND              | BVNN2                 | BVDD3             | GND            | GPIO10         | DVDD1P8    | SERDIN6-  | SERDIN6+      | SVDD1         | GND       | GND       |

| U | DAC3P  | GND   | GND           | GND            | GND        | GND          | DNC           | VCM1             | GND                   | GND               | RVDD2          | SYNC1OUTB+     | SYNC0OUTB+ | . GND     | GND           | SVDD1         | SERDIN3-  | SERDIN3+  |

| v | GND    | AVDD2 | GND           | GND            | NC         | NC           | GND           | GND              | ADC1N                 | ADC1P             | GND            | SYNC1OUTB-     | SYNC0OUTB- | SERDIN5-  | SERDIN5+      | SVDD1         | GND       | GND       |

| I |        |       |               |                |            |              | GND           | ANALOG<br>GROUND | GND                   | DIGITAL<br>GROUND | GI             | ND SERDE       | S<br>ND    |           |               |               |           |           |

Rev. A | Page 16 of 33

Figure 5. 324-Ball Pin Configuration

Table 14. Pin Function Descriptions

| Mnemonic   | Туре                                                                                                                                                                                                                   | Description                                                                                                                                                                                       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                                                                                                                                                                                        |                                                                                                                                                                                                   |

| AVDD2      | Input                                                                                                                                                                                                                  | Analog 2.0 V Supply Inputs for DAC.                                                                                                                                                               |

| AVDD2_PLL  | Input                                                                                                                                                                                                                  | Analog 2.0 V Supply Input for Clock PLL Linear<br>Dropout Regulator (LDO).                                                                                                                        |

| BVDD2      | Input                                                                                                                                                                                                                  | Analog 2.0 V Supply Inputs for ADC Buffer.                                                                                                                                                        |

| RVDD2      | Input                                                                                                                                                                                                                  | Analog 2.0 V Supply Inputs for ADC Reference.                                                                                                                                                     |

| PLLCLKVDD1 | Input                                                                                                                                                                                                                  | Analog 1.0 V Supply Input for Clock PLL.                                                                                                                                                          |

| AVDD1      | Input                                                                                                                                                                                                                  | Analog 1.0 V Supply Inputs for DAC Clock.                                                                                                                                                         |