# 1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT

#### SSTE32882HLB

### **Description**

This 28-bit 1:2, or 26-bit 1:2 and 4-bit 1:1, registering clock driver with parity is designed for 1.35V and 1.5V VDD operation.

All inputs are 1.35V and 1.5V CMOS compatible, except the reset ( $\overline{RESET}$ ) and MIRROR inputs which are LVCMOS. All outputs are 1.35V and 1.5V CMOS edge-controlled drivers optimized to drive single terminated 25 $\Omega$  to 50 $\Omega$  traces in DDR3 RDIMM applications, except the open-drain error ( $\overline{ERROUT}$ ) output. The clock outputs (Yn and  $\overline{Yn}$ ) and control net outputs QnCKEn,  $\overline{QnCSn}$  and QnODTn are designed with a different strength and skew to compensate for different loading and equalize signal travel speed.

The SSTE32882HLB has two basic modes of operation associated with the Quad Chip Select Enable ( $\overline{QCSEN}$ ) input. When the  $\overline{QCSEN}$  input pin is open (or pulled high), the component has two chip select inputs,  $\overline{DCS0}$  and  $\overline{DCS1}$ , and two copies of each chip select output,  $\overline{QACS0}$ ,  $\overline{QACS1}$ ,  $\overline{QBCS0}$  and  $\overline{QBCS1}$ . This is the "QuadCS disabled" mode. When the  $\overline{QCSEN}$  input pin is pulled low, the component has four chip select inputs  $\overline{DCS[3:0]}$ , and four chip select outputs,  $\overline{QCS[3:0]}$ . This is the "QuadCS enabled" mode. Through the remainder of this specification,  $\overline{DCS[n:0]}$  will indicate all of the chip select inputs, where n=1 for QuadCS disabled, and n=3 for QuadCS enabled.  $\overline{QxCS[n:0]}$  will indicate all of the chip select outputs.

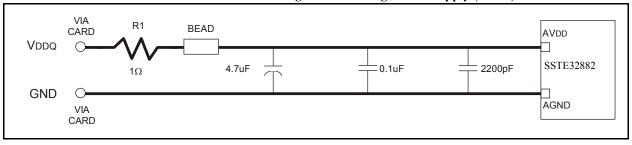

The SSTE32882HLB includes a high-performance, low-jitter, low-skew buffer that distributes a differential clock input (CK and  $\overline{CK}$ ) to four differential pairs of clock outputs (Yn and  $\overline{Yn}$ ), and to one differential pair of feedback clock outputs (FBOUT and  $\overline{FBOUT}$ ). The clock outputs are controlled by the input clocks (CK and  $\overline{CK}$ ), the feedback clocks (FBIN and  $\overline{FBIN}$ ), and the analog power inputs (AVDD and AVSS). When AVDD is grounded, the PLL is turned off and bypassed for test purposes.

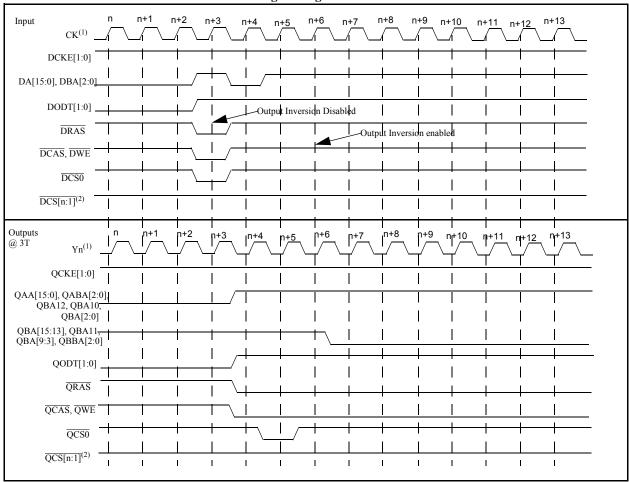

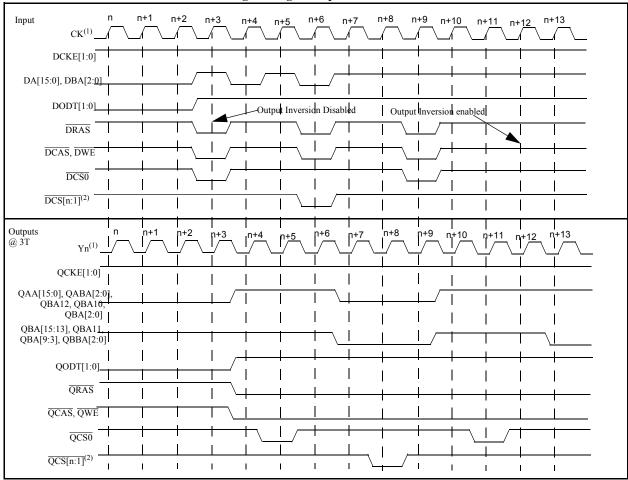

The SSTE32882HLB operates from a differential clock (CK and  $\overline{CK}$ ). Data are registered at the crossing of CK going high, and  $\overline{CK}$  going low. The data is either driven to the corresponding device outputs if exactly one of the  $\overline{DCS[n:0]}$  input signals is driven low.

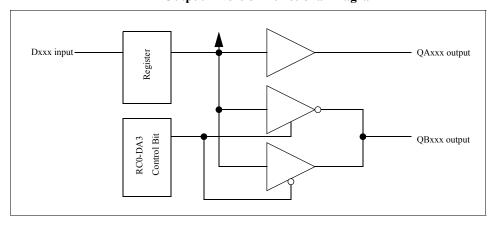

Based on the control register settings, the device can change its output characterisitics to match different DIMM net topologies. The timing can be changed to compensate for different flight time of signals within the target application. By disabling unused outputs the power consumption is reduced.

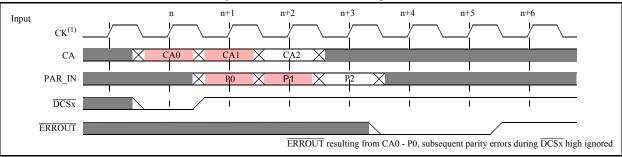

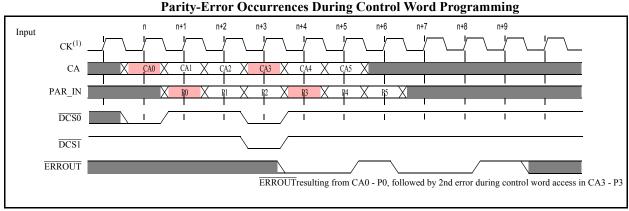

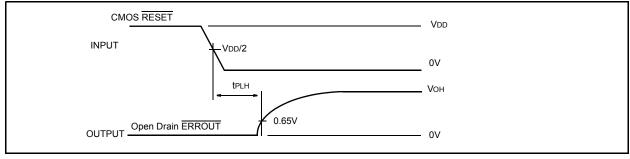

The SSTE32882HLB accepts a parity bit from the memory controller on the parity (PAR\_IN) input, compares it with the data received on the DIMM-independent data inputs (DAn, DBAn, DRAS, DCAS, and DWE), and indicates whether a parity error

has occurred on the open-drain  $\overline{ERROUT}$  pin (active low). The convention is even parity; i.e., valid parity is defined as an even number of ones across the DIMM-independent data inputs combined with the parity input bit. To calculate parity, all DIMM-independent D-inputs must be tied to a known logic state.

The DIMM-dependent signals (DCKEn, DODTn, and  $\overline{DCSn}$ ) are not included in the parity check computation.

To ensure defined outputs from the register before a stable clock has been supplied,  $\overline{RESET}$  must be held in the low state during power-up.

The SSTE32882HLB is available in a 176-ball BGA with 0.65mm ball pitch in a 11 x 20 grid. It is also available in a 176-ball Thin-Profile Fine-Pitch BGA with 0.65mm ball pitch in an 8x22 grid. The device pinout supports outputs on the outer two left and right columns to support easy DIMM signal routing. Corresponding inputs are placed in a-way that two devices can be placed back-to-back for four Rank modules while the data inputs share the same vias. Each input and output is located close to an associated no ball position or on the outer two rows to allow low cost via technology combined with the small 0.65mm ball pitch.

#### SSTE32882HLB

#### 1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT COMMERCIAL TEMPERATURE

#### **Features**

- Pinout optimizes DDR3 RDIMM PCB layout

- 1-to-2 Register Outputs and 1-to-4 Clock Pair Outputs support stacked DDR3 RDIMMs

- Phase Lock Loop clock driver for buffering one differential clock pair (CK and  $\overline{CK}$ ) and distributing to four differential outputs

- Supports LVCMOS switching levels on the RESET and MIRROR inputs

- Checks priority on DIMM-independent data inputs

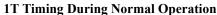

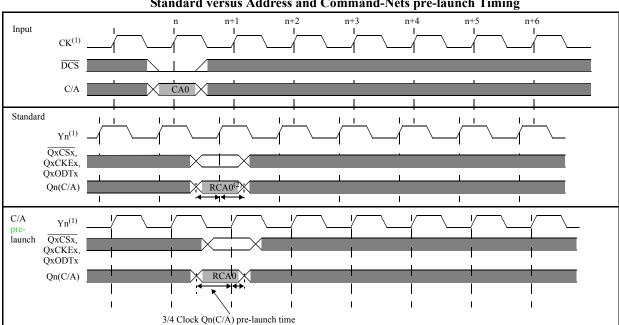

- Supports dynamic 1T/3T timing transaction and output inversion feature for improved timing performance during normal operations and MRS command pass-through

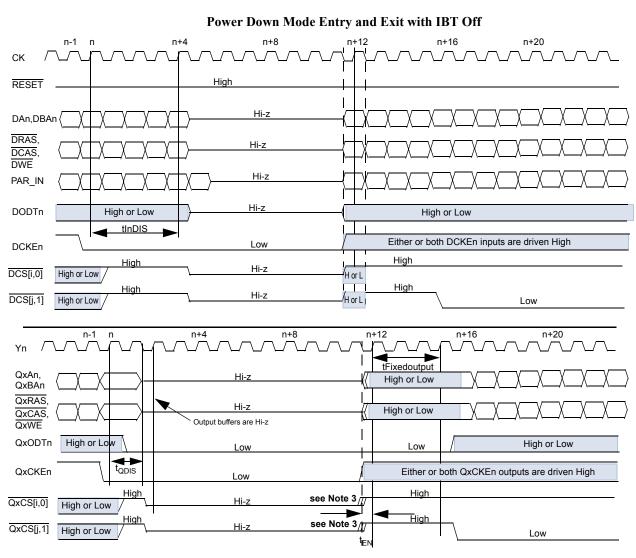

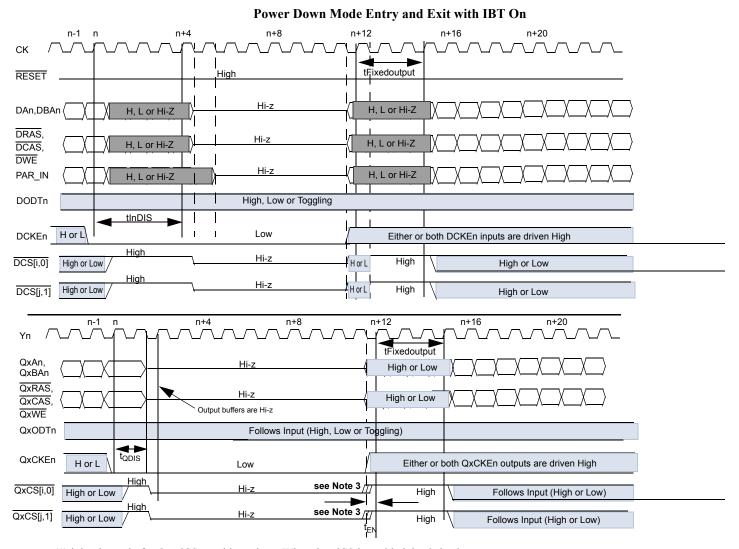

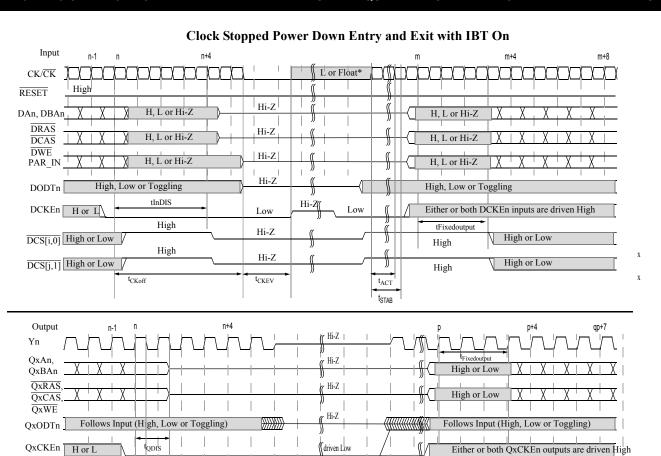

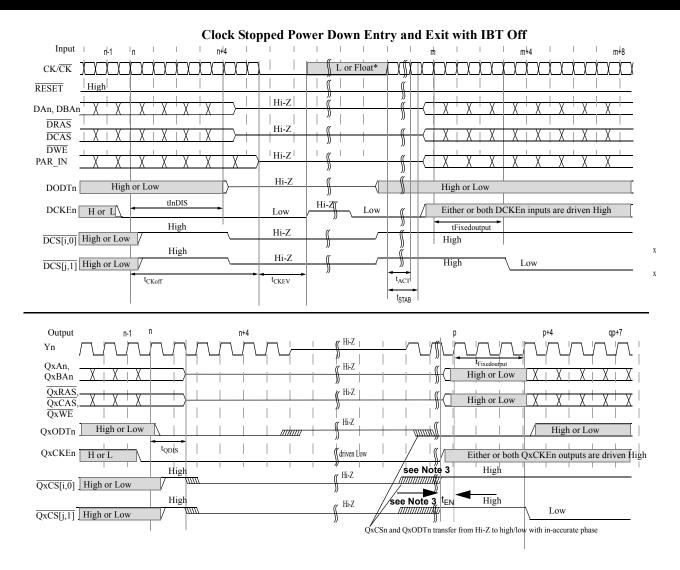

- Supports CKE Power Down operation modes

- Supports Quad Chip Select operation features

- RESET input disables differential input recievers, resets all registers, and disables all output drivers except ERROUT and QnCKEn

- Provides access to internal control words for configuring the device features and adapting in different RDIMM and system applications

- Latch-up performance exceeds 100mA

- ESD > 2000V per MIL-STD883, Method 3015; ESD > 200V using machine model (c = 200pF, R = 0)

- Available in 176 Ball Grid Array package

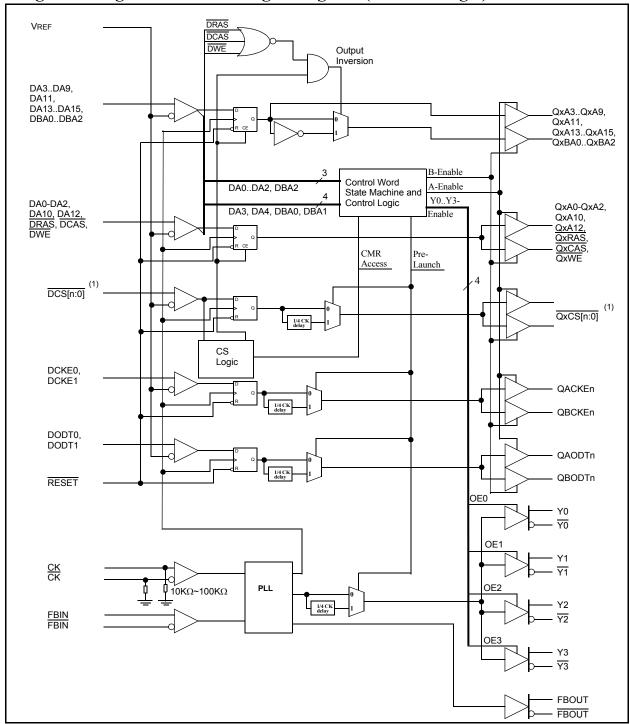

### Block Diagram - Register and PLL Logic Diagram (Positive Logic)

<sup>1</sup>  $\overline{DCS[n:0]}$  indicates all of the chip select inputs, where n=1 for QuadCS disabled, and n=3 for QuadCS enabled.  $\overline{QxCS[n:0]}$  indicates all of the chip select outputs.

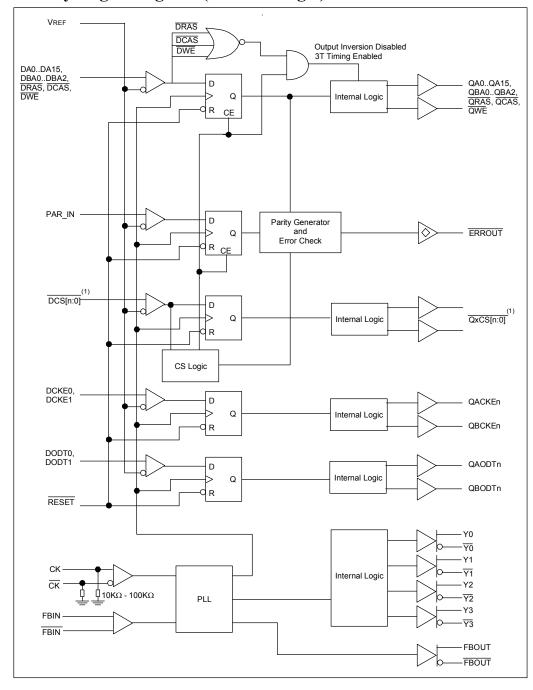

## **Block Diagram - Parity Logic Diagram (Positive Logic)**

1  $\overline{DCS[n:0]}$  indicates all of the chip select inputs, where n=1 for QuadCS disabled, and n=3 for QuadCS enabled.  $\overline{QxCS[n:0]}$ indicates all of the chip select outputs.

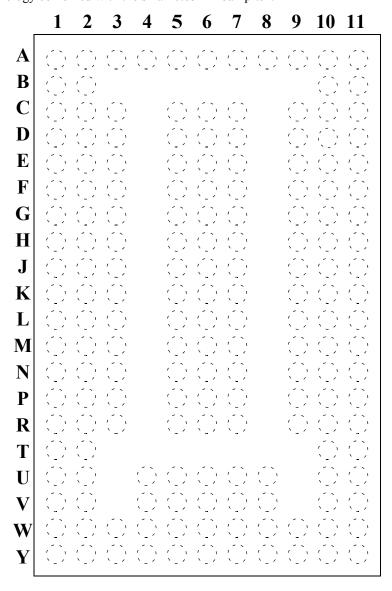

### **Pinout Configuration**

Package options include a 176-ball Thin-Profile Fine-Pitch BGA (TFBGA) with 0.65mm ball pitch, 11 x 20 grid, 8.0mm x 13.5mm. It uses the mechanical outline MO-246 variation F. The device pinout supports outputs on the outer two left and right columns to support easy DIMM signal routing. Corresponding inputs are placed in a way that two devices can be placed back to back for 4 Rank modules while the data inputs share the same vias. Each input and output is located close to an associated no-ball position or on the outer two rows to allow low cost via technology combined with the small 0.65mm ball pitch.

176-ball Thin Profile Fine Pitch BGA (TFBGA) 11x20 Grid

Top View

### **Pin Descriptions**

The device has symmetric pinout with the inputs on the south side and the outputs on the east and west sides. This allows back-to-back mounting on both sides of the PCB if more than one device is needed.

# Ball Assignment: MIRROR = LOW, $\overline{QCSEN}$ = HIGH or float

This table specifies the pinout for SSTE32882HLB in the front configuration (QuadCS mode disabled).

Balls A9 and W7 are reserved for future functions and must not be connected on the system. However, a ball on the device and connecting pad on the module are required in these locations. Also, balls Y2 and R6 are "do not use" balls reserved for  $\overline{DCS2}$  and  $\overline{DCS3}$  in the QuadCS mode, and must not be connected on the system. The device is designed to tolerate floating on these pins. Blank spaces indicate no ball is populated at that gridpoint, and vias on the module may be located in these areas.

|   | 1     | 2      | 3     | 4         | 5     | 6      | 7      | 8         | 9     | 10     | 11           |

|---|-------|--------|-------|-----------|-------|--------|--------|-----------|-------|--------|--------------|

| A | QAA13 | QAA8   | QCSEN | Vss       | RESET | MIRROR | ERROUT | Vss       | RSVD  | QBA8   | QBA13        |

| В | QAA14 | QAA7   |       |           |       |        |        |           |       | QBA7   | QBA14        |

| С | QAA9  | QAA6   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA6   | QBA9         |

| D | QAA11 | QAA5   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA5   | QBA11        |

| Е | QAA2  | QAA4   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA4   | QBA2         |

| F | QAA1  | QAA3   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA3   | QBA1         |

| G | QAA0  | QABA1  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBBA1  | QBA0         |

| Н | QAA12 | QABA0  | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBBA0  | QBA12        |

| J | QABA2 | QACS1  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBCS1  | QBBA2        |

| K | QAA15 | QACKE0 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE0 | QBA15        |

| L | QAWE  | QACS0  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBCS0  | QBWE         |

| M | QAA10 | QACKE1 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE1 | QBA10        |

| N | QACAS | QAODT0 | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBODT0 | <b>QBCAS</b> |

| P | QARAS | QAODT1 | DA3   |           | Vss   | Vss    | Vss    |           | DA4   | QBODT1 | QBRAS        |

| R | DCKE1 | DA14   | DA15  |           | DA5   | RSVD   | DA2    |           | DA1   | DA10   | DODT1        |

| T | DCKE0 | DCS0   |       |           |       |        |        |           |       | DCS1   | DODT0        |

| U | DA12  | DBA2   |       | <u>Y1</u> | PVss  | Vdd    | PVdd   | <u>Y0</u> |       | DA13   | DCAS         |

| V | DA9   | DA11   |       | Y1        | PVss  | Vss    | PVDD   | Y0        |       | DRAS   | DWE          |

| W | DA8   | DA6    | FBIN  | <u>Y3</u> | AVss  | CK     | RSVD   | <u>Y2</u> | FBOUT | DA0    | DBA0         |

| Y | DA7   | RSVD   | FBIN  | Y3        | AVdd  | CK     | VREFCA | Y2        | FBOUT | PAR_IN | DBA1         |

# **Ball Assignment: MIRROR = HIGH, \overline{QCSEN} = HIGH or float**

This table specifies the pinout for SSTE32882HLB in the back configuration (QuadCS mode disabled).

Balls A9 and W7 are reserved for future functions and must not be connected on the system. However, a ball on the device and connecting pad on the module are required in these locations. Also, balls Y10 and R6 are "do not use" balls reserved for  $\overline{DCS2}$  and  $\overline{DCS3}$  in the QuadCS mode, and must not be connected on the system. The device is designed to tolerate floating on these pins. Blank spaces indicate no ball is populated at that gridpoint, and vias on the module may be located in these areas.

|   | 1     | 2      | 3     | 4         | 5     | 6      | 7      | 8         | 9     | 10     | 11    |

|---|-------|--------|-------|-----------|-------|--------|--------|-----------|-------|--------|-------|

| A | QAA13 | QAA8   | QCSEN | Vss       | RESET | MIRROR | ERROUT | Vss       | RSVD  | QBA8   | QBA13 |

| В | QAA14 | QAA7   |       |           |       |        |        |           |       | QBA7   | QBA14 |

| С | QAA9  | QAA6   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA6   | QBA9  |

| D | QAA11 | QAA5   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA5   | QBA11 |

| Е | QAA2  | QAA4   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA4   | QBA2  |

| F | QAA1  | QAA3   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA3   | QBA1  |

| G | QAA0  | QABA1  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBBA1  | QBA0  |

| Н | QAA12 | QABA0  | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBBA0  | QBA12 |

| J | QABA2 | QACS1  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBCS1  | QBBA2 |

| K | QAA15 | QACKE0 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE0 | QBA15 |

| L | QAWE  | QACS0  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBCS0  | QBWE  |

| M | QAA10 | QACKE1 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE1 | QBA10 |

| N | QACAS | QAODT0 | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBODT0 | QBCAS |

| P | QARAS | QAODT1 | DA4   |           | Vss   | Vss    | Vss    |           | DA3   | QBODT1 | QBRAS |

| R | DODT1 | DA10   | DA1   |           | DA2   | RSVD   | DA5    |           | DA15  | DA14   | DCKE1 |

| T | DODT0 | DCS1   |       |           |       |        |        |           |       | DCS0   | DCKE0 |

| U | DCAS  | DA13   |       | <u>Y1</u> | PVss  | Vdd    | PVdd   | <u>¥0</u> |       | DBA2   | DA12  |

| V | DWE   | DRAS   |       | Y1        | PVss  | Vss    | PVdd   | Y0        |       | DA11   | DA9   |

| W | DBA0  | DA0    | FBIN  | <u>¥3</u> | AVss  | CK     | RSVD   | <u>¥2</u> | FBOUT | DA6    | DA8   |

| Y | DBA1  | PAR_IN | FBIN  | Y3        | AVdd  | CK     | VREFCA | Y2        | FBOUT | RSVD   | DA7   |

# Ball Assignment: MIRROR = LOW, $\overline{QCSEN}$ = LOW

This table specifies the pinout for SSTE32882HLB in the front configuration (QuadCS mode enabled).

Balls A9 and W7 are reserved for future functions and must not be connected on the system. However, a ball on the device and connecting pad on the module are required in these locations. Blank spaces indicate no ball is populated at that gridpoint, and vias on the module may be located in these areas.

|   | 1     | 2      | 3     | 4         | 5     | 6      | 7      | 8         | 9     | 10     | 11           |

|---|-------|--------|-------|-----------|-------|--------|--------|-----------|-------|--------|--------------|

| A | QAA13 | QAA8   | QCSEN | Vss       | RESET | MIRROR | ERROUT | Vss       | RSVD  | QBA8   | QBA13        |

| В | QAA14 | QAA7   |       |           |       |        |        |           |       | QBA7   | QBA14        |

| С | QAA9  | QAA6   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA6   | QBA9         |

| D | QAA11 | QAA5   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA5   | QBA11        |

| Е | QAA2  | QAA4   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA4   | QBA2         |

| F | QAA1  | QAA3   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA3   | QBA1         |

| G | QAA0  | QABA1  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBBA1  | QBA0         |

| Н | QAA12 | QABA0  | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBBA0  | QBA12        |

| J | QABA2 | QCS1   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QCS3   | QBBA2        |

| K | QAA15 | QACKE0 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE0 | QBA15        |

| L | QAWE  | QCS0   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QCS2   | QBWE         |

| M | QAA10 | QACKE1 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE1 | QBA10        |

| N | QACAS | QAODT0 | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBODT0 | <b>QBCAS</b> |

| P | QARAS | QAODT1 | DA3   |           | Vss   | Vss    | Vss    |           | DA4   | QBODT1 | QBRAS        |

| R | DCKE1 | DA14   | DA15  |           | DA5   | DCS3   | DA2    |           | DA1   | DA10   | DODT1        |

| T | DCKE0 | DCS0   |       |           |       |        |        |           |       | DCS1   | DODT0        |

| U | DA12  | DBA2   |       | <u>¥1</u> | PVss  | Vdd    | PVdd   | <u>Y0</u> |       | DA13   | DCAS         |

| V | DA9   | DA11   |       | Y1        | PVss  | Vss    | PVdd   | Y0        |       | DRAS   | DWE          |

| W | DA8   | DA6    | FBIN  | <u>¥3</u> | AVss  | CK     | RSVD   | <u>¥2</u> | FBOUT | DA0    | DBA0         |

| Y | DA7   | DCS2   | FBIN  | Y3        | AVDD  | CK     | VREFCA | Y2        | FBOUT | PAR_IN | DBA1         |

# Ball Assignment: MIRROR = HIGH, $\overline{QCSEN}$ = LOW

This table specifies the pinout for SSTE32882HLB in the back configuration (QuadCS mode enabled).

Balls A9 and W7 are reserved for future functions and must not be connected on the system. However, a ball on the device and connecting pad on the module are required in these locations. Blank spaces indicate no ball is populated at that gridpoint, and vias on the module may be located in these areas.

|   | 1     | 2      | 3     | 4         | 5     | 6      | 7      | 8         | 9     | 10     | 11    |

|---|-------|--------|-------|-----------|-------|--------|--------|-----------|-------|--------|-------|

| A | QAA13 | QAA8   | QCSEN | Vss       | RESET | MIRROR | ERROUT | Vss       | RSVD  | QBA8   | QBA13 |

| В | QAA14 | QAA7   |       |           |       |        |        |           |       | QBA7   | QBA14 |

| С | QAA9  | QAA6   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA6   | QBA9  |

| D | QAA11 | QAA5   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA5   | QBA11 |

| Е | QAA2  | QAA4   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBA4   | QBA2  |

| F | QAA1  | QAA3   | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBA3   | QBA1  |

| G | QAA0  | QABA1  | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBBA1  | QBA0  |

| Н | QAA12 | QABA0  | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBBA0  | QBA12 |

| J | QABA2 | QCS1   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QCS3   | QBBA2 |

| K | QAA15 | QACKE0 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE0 | QBA15 |

| L | QAWE  | QCS0   | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QCS2   | QBWE  |

| M | QAA10 | QACKE1 | Vss   |           | Vss   | Vss    | Vss    |           | Vss   | QBCKE1 | QBA10 |

| N | QACAS | QAODT0 | Vdd   |           | Vdd   | Vdd    | Vdd    |           | Vdd   | QBODT0 | QBCAS |

| P | QARAS | QAODT1 | DA4   |           | Vss   | Vss    | Vss    |           | DA3   | QBODT1 | QBRAS |

| R | DODT1 | DA10   | DA1   |           | DA2   | DCS3   | DA5    |           | DA15  | DA14   | DCKE1 |

| T | DODT0 | DCS1   |       |           |       |        |        |           |       | DCS0   | DCKE0 |

| U | DCAS  | DA13   |       | <u>Y1</u> | PVss  | Vdd    | PVdd   | <u>¥0</u> |       | DBA2   | DA12  |

| V | DWE   | DRAS   |       | Y1        | PVss  | Vss    | PVdd   | Y0        |       | DA11   | DA9   |

| W | DBA0  | DA0    | FBIN  | <u>¥3</u> | AVss  | CK     | RSVD   | <u>¥2</u> | FBOUT | DA6    | DA8   |

| Y | DBA1  | PAR_IN | FBIN  | Y3        | AVDD  | CK     | VREFCA | Y2        | FBOUT | DCS2   | DA7   |

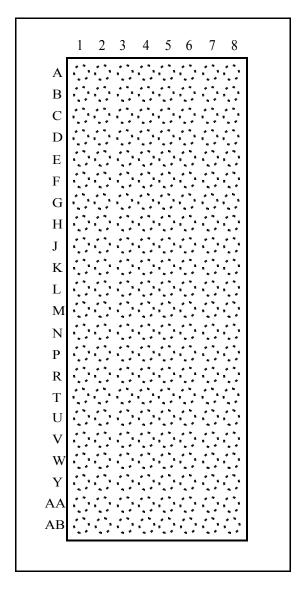

# Pinout configuration narrow package<sup>1</sup>

As an option, the device is available as a 176-ball Thin-Profile Fine-Pitch BGA (TFBGA) with 0.65mm ball pitch, 8 x 22 grid, 6.0mm x 15mm. It is using the mechanical outline MO-246 variation B. Equivalent to the 11 x 20 grid configuration the device pinout supports outputs on the outer two left and right columns. Corresponding inputs are placed in a way that two devices can be placed back to back for 4 Rank modules while the data inputs share the same vias.

176-ball Thin Profile Fine Pitch BGA (TFBGA) 8x22 Grid

Top View

<sup>1.</sup> This package may only be used in new DIMM designs. It is not intended for use in the existing DIMM's.

# Ball Assignment; MIRROR=LOW, QCSEN=HIGH (or Float)

The table below specifies the pinout for SSTE32882 in front configuration with QuadCS mode disabled. The device has symmetric pinout with inputs at the south side and outputs to east and west sides. This allows back to back mounting on both sides of the PCB if more than one device is needed.

|    | 1     | 2      | 3              | 4     | 5      | 6               | 7      | 8     |

|----|-------|--------|----------------|-------|--------|-----------------|--------|-------|

| A  | QAA13 | QAA8   | QCSEN          | RESET | ERROUT | RSVD            | QBA8   | QBA13 |

| В  | QAA14 | QAA7   | VSS            | VSS   | MIRROR | VSS             | QBA7   | QBA14 |

| С  | QAA9  | QAA6   | VDD            | VDD   | VDD    | VDD             | QBA6   | QBA9  |

| D  | QAA11 | QAA5   | VSS            | VSS   | VSS    | VSS             | QBA5   | QBA11 |

| E  | QAA2  | QAA4   | VDD            | VDD   | VDD    | VDD             | QBA4   | QBA2  |

| F  | QAA1  | QAA3   | VSS            | VSS   | VSS    | VSS             | QBA3   | QBA1  |

| G  | QAA0  | QABA1  | VDD            | VDD   | VDD    | VDD             | QBBA1  | QBA0  |

| Н  | QAA12 | QABA0  | VSS            | VSS   | VSS    | VSS             | QBBA0  | QBA12 |

| J  | QABA2 | QACS1  | VDD            | VDD   | VDD    | VDD             | QBCS1  | QBBA2 |

| K  | QAA15 | QACKE0 | VSS            | VSS   | VSS    | VSS             | QBCKE0 | QBA15 |

| L  | QAWE  | QACS0  | VDD            | VDD   | VDD    | VDD             | QBCS0  | QBWE  |

| M  | QAA10 | QACKE1 | VSS            | VSS   | VSS    | VSS             | QBCKE1 | QBA10 |

| N  | QACAS | QAODT0 | VDD            | VDD   | VDD    | VDD             | QBODT0 | QBCAS |

| P  | QARAS | QAODT1 | VSS            | VSS   | VSS    | VSS             | QBODT1 | QBRAS |

| R  | DA14  | DCKE1  | VDD            | VDD   | VDD    | VDD             | DODT1  | DA10  |

| T  | DCS0  | DCKE0  | VSS            | VSS   | VSS    | VSS             | DODT0  | DCS1  |

| U  | DA12  | DA3    | <u>¥1</u>      | PVSS  | PVDD   | $\overline{Y0}$ | DA4    | DCAS  |

| V  | DA5   | DA9    | Y1             | PVSS  | PVDD   | Y0              | DWE    | DA2   |

| W  | DA8   | DA15   | <del>¥</del> 3 | PVSS  | PVDD   | <u>¥2</u>       | DA1    | DBA0  |

| Y  | DA7   | DBA2   | Y3             | AVSS  | AVDD   | Y2              | DA13   | DBA1  |

| AA | DA11  | RSVD   | FBIN           | CK    | RSVD   | FBOUT           | PAR_IN | DRAS  |

| AB | DA6   | RSVD   | FBIN           | CK    | VREFCA | FBOUT           | RSVD   | DA0   |

Pins A6, AA2, AA5, AB2 and AB7 are reserved for future functions must not be connected on system. The system must provide a solder pad for these pins. The device design needs to tolerate floating on these pins. A3 may be left floating since it has an internal pull-up resistor.

# Ball Assignment; MIRROR=HIGH, QCSEN=HIGH (or Float)

The table below specifies the pinout for SSTE32882 in back configuration with QuadCS mode disabled.

|    | 1     | 2      | 3             | 4     | 5      | 6               | 7      | 8     |

|----|-------|--------|---------------|-------|--------|-----------------|--------|-------|

| A  | QAA13 | QAA8   | QCSEN         | RESET | ERROUT | RSVD            | QBA8   | QBA13 |

| В  | QAA14 | QAA7   | VSS           | VSS   | MIRROR | VSS             | QBA7   | QBA14 |

| С  | QAA9  | QAA6   | VDD           | VDD   | VDD    | VDD             | QBA6   | QBA9  |

| D  | QAA11 | QAA5   | VSS           | VSS   | VSS    | VSS             | QBA5   | QBA11 |

| E  | QAA2  | QAA4   | VDD           | VDD   | VDD    | VDD             | QBA4   | QBA2  |

| F  | QAA1  | QAA3   | VSS           | VSS   | VSS    | VSS             | QBA3   | QBA1  |

| G  | QAA0  | QABA1  | VDD           | VDD   | VDD    | VDD             | QBBA1  | QBA0  |

| Н  | QAA12 | QABA0  | VSS           | VSS   | VSS    | VSS             | QBBA0  | QBA12 |

| J  | QABA2 | QACS1  | VDD           | VDD   | VDD    | VDD             | QBCS1  | QBBA2 |

| K  | QAA15 | QACKE0 | VSS           | VSS   | VSS    | VSS             | QBCKE0 | QBA15 |

| L  | QAWE  | QACS0  | VDD           | VDD   | VDD    | VDD             | QBCS0  | QBWE  |

| M  | QAA10 | QACKE1 | VSS           | VSS   | VSS    | VSS             | QBCKE1 | QBA10 |

| N  | QACAS | QAODT0 | VDD           | VDD   | VDD    | VDD             | QBODT0 | QBCAS |

| P  | QARAS | QAODT1 | VSS           | VSS   | VSS    | VSS             | QBODT1 | QBRAS |

| R  | DA10  | DODT1  | VDD           | VDD   | VDD    | VDD             | DCKE1  | DA14  |

| Т  | DCS1  | DODT0  | VSS           | VSS   | VSS    | VSS             | DCKE0  | DCS0  |

| U  | DCAS  | DA4    | <u>¥1</u>     | PVSS  | PVDD   | $\overline{Y0}$ | DA3    | DA12  |

| V  | DA2   | DWE    | Y1            | PVSS  | PVDD   | Y0              | DA9    | DA5   |

| W  | DBA0  | DA1    | <del>¥3</del> | PVSS  | PVDD   | <u>¥2</u>       | DA15   | DA8   |

| Y  | DBA1  | DA13   | Y3            | AVSS  | AVDD   | Y2              | DBA2   | DA7   |

| AA | DRAS  | PAR_IN | FBIN          | CK    | RSVD   | FBOUT           | RSVD   | DA11  |

| AB | DA0   | RSVD   | FBIN          | CK    | VREFCA | FBOUT           | RSVD   | DA6   |

Pins A6, AA5, AA7, AB2 and AB7 are reserved for future functions must not be connected on system. The system must provide a solder pad for these pins. The device design needs to tolerate floating on these pins. A3 may be left floating since it has an internal pull-up resistor.

# Ball Assignment; MIRROR=LOW, QCSEN=LOW

The table below specifies the pinout for SSTE32882 in front configuration with QuadCS mode enabled.

|    | 1     | 2      | 3              | 4     | 5      | 6             | 7      | 8     |

|----|-------|--------|----------------|-------|--------|---------------|--------|-------|

| A  | QAA13 | QAA8   | QCSEN          | RESET | ERROUT | RSVD          | QBA8   | QBA13 |

| В  | QAA14 | QAA7   | VSS            | VSS   | MIRROR | VSS           | QBA7   | QBA14 |

| C  | QAA9  | QAA6   | VDD            | VDD   | VDD    | VDD           | QBA6   | QBA9  |

| D  | QAA11 | QAA5   | VSS            | VSS   | VSS    | VSS           | QBA5   | QBA11 |

| E  | QAA2  | QAA4   | VDD            | VDD   | VDD    | VDD           | QBA4   | QBA2  |

| F  | QAA1  | QAA3   | VSS            | VSS   | VSS    | VSS           | QBA3   | QBA1  |

| G  | QAA0  | QABA1  | VDD            | VDD   | VDD    | VDD           | QBBA1  | QBA0  |

| Н  | QAA12 | QABA0  | VSS            | VSS   | VSS    | VSS           | QBBA0  | QBA12 |

| J  | QABA2 | QCS1   | VDD            | VDD   | VDD    | VDD           | QCS3   | QBBA2 |

| K  | QAA15 | QACKE0 | VSS            | VSS   | VSS    | VSS           | QBCKE0 | QBA15 |

| L  | QAWE  | QCS0   | VDD            | VDD   | VDD    | VDD           | QCS2   | QBWE  |

| M  | QAA10 | QACKE1 | VSS            | VSS   | VSS    | VSS           | QBCKE1 | QBA10 |

| N  | QACAS | QAODT0 | VDD            | VDD   | VDD    | VDD           | QBODT0 | QBCAS |

| P  | QARAS | QAODT1 | VSS            | VSS   | VSS    | VSS           | QBODT1 | QBRAS |

| R  | DA14  | DCKE1  | VDD            | VDD   | VDD    | VDD           | DODT1  | DA10  |

| T  | DCS0  | DCKE0  | VSS            | VSS   | VSS    | VSS           | DODT0  | DCS1  |

| U  | DA12  | DA3    | <u>¥1</u>      | PVSS  | PVDD   | <del>Y0</del> | DA4    | DCAS  |

| V  | DA5   | DA9    | Y1             | PVSS  | PVDD   | Y0            | DWE    | DA2   |

| W  | DA8   | DA15   | <del>¥</del> 3 | PVSS  | PVDD   | <del>Y2</del> | DA1    | DBA0  |

| Y  | DA7   | DBA2   | Y3             | AVSS  | AVDD   | Y2            | DA13   | DBA1  |

| AA | DA11  | DCS2   | FBIN           | CK    | RSVD   | FBOUT         | PAR_IN | DRAS  |

| AB | DA6   | RSVD   | FBIN           | CK    | VREFCA | FBOUT         | DCS3   | DA0   |

Pins A6, AA5 and AB2 are reserved for future functions must not be connected on system. The system must provide a solder pad for these pins. The device design needs to tolerate floating on these pins. A3 must be tied LOW for this configuration.

# Ball Assignment; MIRROR=HIGH, QCSEN=LOW)

The table below specifies the pinout for SSTE32882 in back configuration with QuadCS mode enabled.

|    | 1     | 2      | 3              | 4     | 5      | 6         | 7      | 8     |

|----|-------|--------|----------------|-------|--------|-----------|--------|-------|

| A  | QAA13 | QAA8   | QCSEN          | RESET | ERROUT | RSVD      | QBA8   | QBA13 |

| В  | QAA14 | QAA7   | VSS            | VSS   | MIRROR | VSS       | QBA7   | QBA14 |

| C  | QAA9  | QAA6   | VDD            | VDD   | VDD    | VDD       | QBA6   | QBA9  |

| D  | QAA11 | QAA5   | VSS            | VSS   | VSS    | VSS       | QBA5   | QBA11 |

| E  | QAA2  | QAA4   | VDD            | VDD   | VDD    | VDD       | QBA4   | QBA2  |

| F  | QAA1  | QAA3   | VSS            | VSS   | VSS    | VSS       | QBA3   | QBA1  |

| G  | QAA0  | QABA1  | VDD            | VDD   | VDD    | VDD       | QBBA1  | QBA0  |

| Н  | QAA12 | QABA0  | VSS            | VSS   | VSS    | VSS       | QBBA0  | QBA12 |

| J  | QABA2 | QCS1   | VDD            | VDD   | VDD    | VDD       | QCS3   | QBBA2 |

| K  | QAA15 | QACKE0 | VSS            | VSS   | VSS    | VSS       | QBCKE0 | QBA15 |

| L  | QAWE  | QCS0   | VDD            | VDD   | VDD    | VDD       | QCS2   | QBWE  |

| M  | QAA10 | QACKE1 | VSS            | VSS   | VSS    | VSS       | QBCKE1 | QBA10 |

| N  | QACAS | QAODT0 | VDD            | VDD   | VDD    | VDD       | QBODT0 | QBCAS |

| P  | QARAS | QAODT1 | VSS            | VSS   | VSS    | VSS       | QBODT1 | QBRAS |

| R  | DA10  | DODT1  | VDD            | VDD   | VDD    | VDD       | DCKE1  | DA14  |

| T  | DCS1  | DODT0  | VSS            | VSS   | VSS    | VSS       | DCKE0  | DCS0  |

| U  | DCAS  | DA4    | <u>¥1</u>      | PVSS  | PVDD   | <u>¥0</u> | DA3    | DA12  |

| V  | DA2   | DWE    | Y1             | PVSS  | PVDD   | Y0        | DA9    | DA5   |

| W  | DBA0  | DA1    | <del>¥</del> 3 | PVSS  | PVDD   | <u>¥2</u> | DA15   | DA8   |

| Y  | DBA1  | DA13   | Y3             | AVSS  | AVDD   | Y2        | DBA2   | DA7   |

| AA | DRAS  | PAR_IN | FBIN           | CK    | RSVD   | FBOUT     | DCS2   | DA11  |

| AB | DA0   | RSVD   | FBIN           | CK    | VREFCA | FBOUT     | DCS3   | DA6   |

Pins A6, AA5 and AB2 are reserved for future functions must not be connected on system. The system must provide a solder pad for these pins. The device design needs to tolerate floating on these pins. A3 must be tied LOW for this configuration.

### **Terminal Functions**

| Signal Group             | Signal Name                                                     | Type                                    | Description                                                                                                                                                                                                                                                                                                                           |

|--------------------------|-----------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ungated inputs           | DCKEn, DODTn                                                    | 1.35V/1.5V<br>CMOS Inputs <sup>1</sup>  | DRAM corresponding register function pins not associated with Chip Select.                                                                                                                                                                                                                                                            |

| Chip Select gated inputs | DAn, DBAn, DRAS, DCAS, DWE                                      | 1.35V/1.5V<br>CMOS Inputs <sup>1</sup>  | DRAM corresponding register inputs, re-driven only when either chip select is LOW. If both chip selects are low the register maintains the state of the previous input clock cycle at its outputs                                                                                                                                     |

| Chip Select inputs       | DCS0, DCS1                                                      | 1.35V/1.5V<br>CMOS Inputs <sup>1</sup>  | DRAM corresponding register Chip Select signals. These pins initiate DRAM address/command decodes, and as such exactly one will be low when a valid address/command is present which should be re-driven.                                                                                                                             |

|                          | DCS2, DCS3                                                      | 1.35V/1.5V<br>CMOS Inputs <sup>1</sup>  | DRAM corresponding register Chip Select signals when QuadCS mode is enabled. $\overline{DCS2}$ and $\overline{DCS3}$ inputs are disabled when QuadCS mode is disabled.                                                                                                                                                                |

| Re-driven outputs        | QxAn, QxBAn, QxCSn,<br>QxCKEn, QxODTn,<br>QxRAS, QxCAS,<br>QxWE | 1.35V/1.5V<br>CMOS Outputs <sup>2</sup> | Outputs of the register, valid after the specified clock count and immediately following a rising edge of the clock. x is A or B; outputs are grouped as A or B and may be enabled or disabled via RC0.                                                                                                                               |

| Parity input             | PAR_IN                                                          | 1.35V/1.5V<br>CMOS Inputs <sup>1</sup>  | Input parity is received on pin PAR_IN and should maintain parity across the Chip Select Gated inputs (see above), at the rising edge of the input clock, one input clock cycle after corresponding data and one or both chip selects are LOW.                                                                                        |

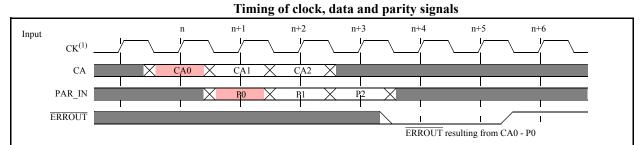

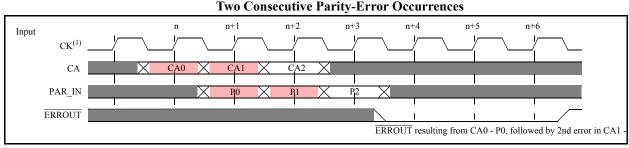

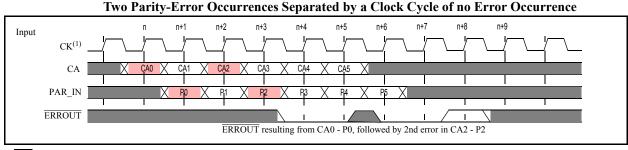

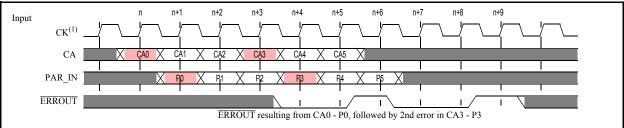

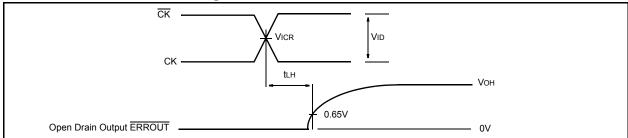

| Parity error output      | ERROUT                                                          | Open drain                              | When LOW, this output indicates that a parity error was identified associated with the address and/or command inputs. ERROUT will be active for two clock cycles, and delayed by 3 clock cycles to the corresponding input data                                                                                                       |

| Clock inputs             | CK, CK                                                          | 1.35V/1.5V<br>CMOS Inputs <sup>1</sup>  | Differential master clock input pair to the PLL; has weak internal pull-down resistors ( $10K\Omega \sim 100K\Omega$ ).                                                                                                                                                                                                               |

| Feedback                 | FBIN, FBIN                                                      | 1.35V/1.5V<br>CMOS Inputs <sup>1</sup>  | Feedback clock input                                                                                                                                                                                                                                                                                                                  |

| Clock                    | FBOUT, FBOUT                                                    | 1.35V/1.5V<br>CMOS Outputs <sup>2</sup> | Feedback clock output                                                                                                                                                                                                                                                                                                                 |

| Clock Outputs            | Yn, <del>Y</del> n                                              | 1.35V/1.5V<br>CMOS Outputs <sup>2</sup> | Re-driven Clock                                                                                                                                                                                                                                                                                                                       |

| Miscellaneous inputs     | RESET                                                           | CMOS <sup>3</sup>                       | Active low asynchronous reset input. When LOW, it causes a reset of the internal latches and disables the outputs, thereby forcing the outputs to float. Once RESET becomes high the Q outputs get enabled and are driven LOW (ERROUT is driven high) until the first access has been performed. RESET also resets the ERROUT signal. |

|                          | MIRROR                                                          | CMOS <sup>3</sup>                       | Selects between two different ballouts for front or back operation. When the MIRROR input is high, the device Input Bus Termination (IBT) is turned off on all inputs, except the $\overline{DCSn}$ and DODTn inputs.                                                                                                                 |

|                          | QSCEN                                                           | CMOS <sup>3</sup>                       | Enables the QuadCS mode. The $\overline{QSCEN}$ input has a weak internal pullup resistor ( $10K\Omega$ - $100K\Omega$ ).                                                                                                                                                                                                             |

| Signal Group | Signal Name         | Type              | Description                                                     |

|--------------|---------------------|-------------------|-----------------------------------------------------------------|

| Power        | Vrefca <sup>1</sup> | Reference Voltage | Input reference voltage for the differential data inputs, VDD/2 |

|              |                     |                   | (0.75V) nominal.                                                |

|              | Vdd                 | Register Power    | Power supply voltage (Register)                                 |

|              | Vss                 | Register Ground   | Ground (Register)                                               |

|              | AVdd                | Analog Power      | Analog supply voltage (PLL)                                     |

|              | AVss                | Analog Ground     | Analog ground (PLL)                                             |

|              | PVdd                | PLL Power         | Clock logic and clock output driver power supply (PLL)          |

|              | PVss                | PLL Ground        | Clock logic and clock output driver ground (PLL)                |

|              | RSVD                | I/O               | Reserved pins, must be left floating (PLL)                      |

- 1 1.35V/1.5V CMOS inputs use VREFCA as the switching point reference for these recievers.

- 2 These outputs are optimized for memory applications to drive DRAM inputs to 1.35V/1.5V signaling levels.

- 3 Voltage levels according standard JESD8-11A, wide range, non terminated logic.

### Function Table (Each Flip Flop) with QuadCS Mode Disabled

|       |               |               | Inputs          |                          |                   |                  |                   | Outputs <sup>1</sup>        |       |       |                  |                  |  |

|-------|---------------|---------------|-----------------|--------------------------|-------------------|------------------|-------------------|-----------------------------|-------|-------|------------------|------------------|--|

| RESET | DCS0          | DCS1          | CK <sup>2</sup> | $\mathbf{C}\mathbf{K}^2$ | ADDR <sup>3</sup> | CMD <sup>4</sup> | CTRL <sup>5</sup> | Qn <sup>6</sup>             | QxCS0 | QxCS1 | QxODTn           | QxCKEn           |  |

| Н     | L             | L             | <b>↑</b>        | <b>\</b>                 | Control<br>Word   | Control<br>Word  | Control<br>Word   | $Q_0$                       | Н     | Н     | $Q_0$            | $Q_0$            |  |

| Н     | X             | X             | L or H          | H or L                   | X                 | X                | X                 | $Q_0$                       | $Q_0$ | $Q_0$ | $Q_0$            | $Q_0$            |  |

| Н     | L             | Н             | <b>↑</b>        | <b>\</b>                 | X                 | X                | X                 | Follows<br>Input            | L     | Н     | Follows<br>Input | Follows<br>Input |  |

| Н     | X             | X             | L               | L                        | X                 | X                | X                 | float                       | float | float | float            | L                |  |

| Н     | Н             | L             | <b>↑</b>        | <b>\</b>                 | X                 | X                | X                 | Follows<br>Input            | Н     | L     | Follows<br>Input | Follows<br>Input |  |

| Н     | Н             | Н             | <b>↑</b>        | $\rightarrow$            | X or<br>float     | X or float       | X                 | $Q_0$ or float <sup>7</sup> | Н     | Н     | Follows<br>Input | Follows<br>Input |  |

| L     | X or<br>float | X or<br>float | X or float      | X or float               | X or<br>float     | X or float       | X or<br>float     | float                       | float | float | float            | L                |  |

- 1  $Q_0$  means the output does not change state.

- 2 It is illegal to hold both the CK and  $\overline{\text{CK}}$  inputs at static logic HIGH levels or static complementary logic levels (LOW and HIGH) when  $\overline{\text{RESET}}$  is driven HIGH.

- 3 ADDR = DA[15:0], DBA[2:0]

- 4 CMD =  $\overline{DRAS}$ ,  $\overline{DCAS}$ ,  $\overline{DWE}$ .

- 5 CTRL = DODTn, DCKEn.

- 6 Qn = QxAn,  $\overline{QxRAS}$ ,  $\overline{QxCAS}$ ,  $\overline{QxWE}$ , and QxBAn.

- Depending on Control Word RC0 Bit DA4. If RC0 DA4 is cleared, previous state  $(Q_0)$  is maintained. Address floating is disabled independent of control word RC0 once 3T timing is activated.

### Function Table (Each Flip Flop) with QuadCS Mode Enabled

|       | Inp        | uts             |                 |                    | Outputs                         |           |           |           |  |  |

|-------|------------|-----------------|-----------------|--------------------|---------------------------------|-----------|-----------|-----------|--|--|

| RESET | DCS[3:0]   | CK <sup>1</sup> | CK <sup>1</sup> | A/C/E <sup>2</sup> | Qn                              | QCS[3:0]  | QxODTn    | QxCKEn    |  |  |

| Н     | LLHH       |                 |                 | Control            | No                              |           |           |           |  |  |

| Н     | HHLL       | <b>↑</b>        | $\downarrow$    | Word               | change                          | НННН      | No change | No change |  |  |

| Н     | LLLL       |                 |                 |                    | - C                             |           |           |           |  |  |

| Н     | XXXX       | L or H          | H or L          | X                  | No<br>change                    | No change | No change | No change |  |  |

| Н     | LHHH       | <b>↑</b>        | $\downarrow$    | Dn                 | Dn                              | LHHH      | DODTn     | DCKEn     |  |  |

| Н     | HLHH       | 1               | $\downarrow$    | Dn                 | Dn                              | HLHH      | DODTn     | DCKEn     |  |  |

| Н     | HHLH       | 1               | $\downarrow$    | Dn                 | Dn                              | HHLH      | DODTn     | DCKEn     |  |  |

| Н     | HHHL       | <b>↑</b>        | $\downarrow$    | Dn                 | Dn                              | HHHL      | DODTn     | DCKEn     |  |  |

| Н     | LHLH       | <b>↑</b>        | $\downarrow$    | Dn                 | Dn                              | LHLH      | DODTn     | DCKEn     |  |  |

| Н     | HLLH       | <b>↑</b>        | $\downarrow$    | Dn                 | Dn                              | HLLH      | DODTn     | DCKEn     |  |  |

| Н     | LHHL       | <b>↑</b>        | $\downarrow$    | Dn                 | Dn                              | LHHL      | DODTn     | DCKEn     |  |  |

| Н     | HLHL       | <b>↑</b>        | $\downarrow$    | Dn                 | Dn                              | HLHL      | DODTn     | DCKEn     |  |  |

| Н     | XXXX       | L               | L               | X                  | float                           | float     | float     | L         |  |  |

| Н     | нннн       | <b>↑</b>        | $\rightarrow$   | X                  | No change or float <sup>3</sup> | нннн      | DODTn     | DCKEn     |  |  |

| Н     | LLLH       |                 |                 |                    |                                 |           |           |           |  |  |

| Н     | LLHL       | <b>^</b>        | $\downarrow$    | X                  | Ilegal Input States             |           |           |           |  |  |

| Н     | LHLL       |                 | •               | Λ                  | negai input states              |           |           |           |  |  |

| Н     | HLLL       |                 |                 |                    |                                 |           |           |           |  |  |

| L     | X or float | X or<br>float   | X or<br>float   | X or float         | float                           | float     | float     | L         |  |  |

<sup>1</sup> It is illegal to hold both the CK and  $\overline{\text{CK}}$  inputs at static logic high levels or static complementary logic levels (low and high) when  $\overline{\text{RESET}}$  is driven high.

<sup>2</sup> A/C/E = DA0..DA15, DBA0..DBA2,  $\overline{DRAS}$ ,  $\overline{DCAS}$ ,  $\overline{DWE}$ , DODTn, DCKEn

<sup>3</sup> Depending on Control Word RC0 Bit DA4. If RC0 DA4 is cleared, previous state is maintained. Address floating is disabled independent of control word RC0 once 3T timing is activated

### Parity, Low Power and Standby with QuadCS Mode Disabled

|       |               |               | Inputs          |                 |                              |                     | Output              |

|-------|---------------|---------------|-----------------|-----------------|------------------------------|---------------------|---------------------|

| RESET | DCS0          | DCS1          | CK <sup>1</sup> | CK <sup>1</sup> | $\Sigma$ of C/A <sup>2</sup> | PAR_IN <sup>3</sup> | ERROUT <sup>4</sup> |

| Н     | L             | X             | 1               | $\downarrow$    | Even                         | L                   | Н                   |

| Н     | L             | X             | 1               | $\downarrow$    | Odd L                        |                     | L                   |

| Н     | L             | X             | 1               | <b>\</b>        | Even                         | Н                   | L                   |

| Н     | L             | X             | 1               | <b>\</b>        | Odd                          | Н                   | Н                   |

| Н     | X             | L             | 1               | $\downarrow$    | Even                         | Even L              |                     |

| Н     | X             | L             | 1               | $\downarrow$    | Odd                          | L                   | L                   |

| Н     | X             | L             | 1               | <b>\</b>        | Even                         | Н                   | L                   |

| Н     | X             | L             | 1               | $\downarrow$    | Odd                          | Н                   | Н                   |

| Н     | Н             | Н             | 1               | $\downarrow$    | X                            | X                   | H <sup>5</sup>      |

| Н     | X             | X             | L or H          | H or L          | X                            | X                   | ERROUT <sub>0</sub> |

| Н     | X             | X             | L               | L               | X                            | X                   | $H^6$               |

| L     | X or floating | X or floating | X or floating   | X or floating   | X or floating                | X or floating       | Н                   |

- 1 It is illegal to hold both the CK and  $\overline{\text{CK}}$  inputs at static logic HIGH levels or static complementary logic levels (LOW and HIGH) when  $\overline{\text{RESET}}$  is driven HIGH.

- 2 C/A= DAn, DBAn,  $\overline{DRAS}$ ,  $\overline{DCAS}$ ,  $\overline{DWE}$ . Inputs DCKEn, DODTn, and  $\overline{DCSn}$  are not included in this range. This column represents the sum of the number of C/A signals that are electrically HIGH.

- 3 PAR\_IN arrives one clock cycle after the data to which it applies, ERROUT is issued three clock cycles after the failing data.

- 4 This transition assumes  $\overline{ERROUT}$  is high at the crossing of CK going high and  $\overline{CK}$  going low. If  $\overline{ERROUT}$  is low, it stays latched low for exactly two clock cycles or until  $\overline{RESET}$  is driven low.

- 5 Same three cycle delay for ERROUT is valid for the de-select phase (see diagram)

- 6 The system is not allowed to pull CK and  $\overline{CK}$  low while  $\overline{ERROUT}$  is asserted.

### Parity, Low Power and Standby with QuadCS Mode Enabled

|       |               | Inputs          |                 |                              |                     | Output               |

|-------|---------------|-----------------|-----------------|------------------------------|---------------------|----------------------|

| RESET | DCS[3:0]      | CK <sup>1</sup> | CK <sup>1</sup> | $\Sigma$ of A/C <sup>2</sup> | PAR_IN <sup>3</sup> | ERROUT <sup>4</sup>  |

| Н     | LXXX          | $\uparrow$      | <b>\</b>        | Even                         | L                   | Н                    |

|       | XLXX          |                 |                 |                              |                     |                      |

|       | XXLX          |                 |                 |                              |                     |                      |

|       | XXXL          |                 |                 |                              |                     |                      |

| Н     | LXXX          | $\uparrow$      | $\downarrow$    | Odd                          | L                   | L                    |

|       | XLXX          |                 |                 |                              |                     |                      |

|       | XXLX          |                 |                 |                              |                     |                      |

|       | XXXL          |                 |                 |                              |                     |                      |

| Н     | LXXX          | <b>1</b>        | $\downarrow$    | Even                         | Н                   | L                    |

|       | XLXX          |                 |                 |                              |                     |                      |

|       | XXLX          |                 |                 |                              |                     |                      |

|       | XXXL          |                 |                 |                              |                     |                      |

| Н     | LXXX          | <b>↑</b>        | $\downarrow$    | Odd                          | Н                   | Н                    |

|       | XLXX          |                 |                 |                              |                     |                      |

|       | XXLX          |                 |                 |                              |                     |                      |

|       | XXXL          |                 |                 |                              |                     |                      |

| Н     | НННН          | $\uparrow$      | <b>\</b>        | X                            | X                   | H <sup>5</sup>       |

| Н     | XXXX          | L or H          | H or L          | X                            | X                   | ERROUTn <sub>0</sub> |

| Н     | XXXX          | L               | L               | X                            | X                   | $H^6$                |

| L     | X or floating | X or floating   | X or floating   | X or floating                | X or floating       | Н                    |

- 1 It is illegal to hold both the CK and  $\overline{\text{CK}}$  inputs at static logic high levels or static complementary logic levels (low and high) when  $\overline{\text{RESET}}$  is driven high.

- 2 A/C = DA0..DA15, DBA0..DBA2,  $\overline{DRAS}$ ,  $\overline{DCAS}$ ,  $\overline{DWE}$ . Inputs DCKE0, DCKE1, DODT0, DODT1,  $\overline{DCSO}$  and  $\overline{DCS1}$  are not included in this range. This column represents the sum of the number of A/C signals that are electrically high.

- 3 PAR\_IN arrivesone clock cycle afterdata to which it applies, ERROUT is issued three clock cycles after the failing data.

- This transition assumes  $\overline{ERROUT}$  is high at the crossing of CK going high and  $\overline{CK}$  going low. If  $\overline{ERROUT}$  is low, it stays latched low for exactly two clock cycles or until  $\overline{RESET}$  is driven low.

- Same three-cycle delay for  $\overline{\text{ERROUT}}$  is valid for the de-select phase (see diagram)

- 6 The system is not allowed to pull CK and  $\overline{CK}$  low while  $\overline{ERROUT}$  is asserted.

### **PLL Function Table**

|       | Inpu             | ts               |                 |                                     |       | Outp  | outs     |       | PLL          |

|-------|------------------|------------------|-----------------|-------------------------------------|-------|-------|----------|-------|--------------|

| RESET | AVDD             | OEn <sup>1</sup> | CK <sup>2</sup> | $\overline{\mathbf{C}\mathbf{K}}^2$ | Yn    | Yn    | FBOUT    | FBOUT |              |

| L     | X                | X                | X               | X                                   | Float | Float | Float    | Float | Off          |

| Н     | VDD nominal      | L                | L               | Н                                   | L     | Н     | L        | Н     | On           |

| Н     | VDD nominal      | L                | Н               | L                                   | Н     | L     | Н        | L     | On           |

| Н     | VDD nominal      | Н                | L               | Н                                   | Float | Float | L        | Н     | On           |

| Н     | VDD nominal      | Н                | Н               | L                                   | Float | Float | Н        | L     | On           |

| Н     | VDD nominal      | X                | L               | L                                   | Float | Float | Float    | Float | Off          |

| Н     | GND <sup>3</sup> | L                | L               | Н                                   | L     | Н     | L        | Н     | Bypassed/Off |

| Н     | GND <sup>3</sup> | L                | Н               | L                                   | Н     | L     | Н        | L     | Bypassed/Off |

| Н     | GND <sup>3</sup> | Н                | L               | Н                                   | Float | Float | L        | Н     | Bypassed/Off |

| Н     | GND <sup>3</sup> | Н                | Н               | L                                   | Float | Float | Н        | L     | Bypassed/Off |

| Н     | GND <sup>3</sup> | X                | L               | L                                   | Float | Float | Float    | Float | Bypassed/Off |

| Н     | X                | X                | Н               | Н                                   |       |       | Reserved |       |              |

<sup>1</sup> The Output Enable (OEn) to disable the output buffer is not an input signal to the SSTE32882HLB, but an internal signal from the PLL powerdown control and test logic. It is controlled by setting or clearing the corresponding bit in the Clock Driver mode register.

<sup>2</sup> It is illegal to hold both the CK and  $\overline{\text{CK}}$  inputs at static logic HIGH levels or static complementary logic levels (LOW and HIGH) when  $\overline{\text{RESET}}$  is driven HIGH.

<sup>3</sup> This is a device test mode and all register timing parameters are not guaranteed.

### **Absolute Maximum Ratings**

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

| Symbol             | Parameter                                                   | Conditions                  | Min  | Max                   | Unit |

|--------------------|-------------------------------------------------------------|-----------------------------|------|-----------------------|------|

| AVDD, PVDD,<br>VDD | Supply voltage                                              |                             | -0.4 | +1.975                | V    |

| VI                 | Receiver input voltage <sup>1</sup>                         |                             | -0.4 | V <sub>DD</sub> + 0.5 | V    |

| Vref               | Reference voltage                                           |                             | -0.4 | V <sub>DD</sub> + 0.5 | V    |

| Vo                 | Driver output voltage <sup>1</sup>                          |                             | -0.4 | V <sub>DD</sub> + 0.5 | V    |

| IIK                | Input clamp current                                         | $V_I < 0$ or $V_I > V_{DD}$ |      | -50                   | mA   |

| Іок                | Output clamp current                                        | Vo < 0 or Vo > VDD          |      | ±50                   | mA   |

| Io                 | Continuous output current                                   | $0 < V_{O} < V_{DD}$        |      | ±50                   | mA   |

| ICCC               | Continuous current through each VDD or GND pin              |                             |      | ±100                  | mA   |

| Tstg               | Storage temperature                                         |                             | -65  | +150                  | °C   |

| Rθja               | Deal or Thomas Long Long to Austin 42                       | 0m/s Airflow                |      | 43.8                  | °C/W |

| KOJA               | Package Thermal Impedance, Junction-to-Ambient <sup>2</sup> | 1m/s Airflow                |      | 35.5                  | C/ W |

| RθJВ               | Package Thermal Impedance, Junction-to-Board <sup>2</sup>   |                             |      | 22                    | °C/W |

| RθJC               | Package Thermal Impedance, Junction-to-Case <sup>2</sup>    |                             |      | 16.2                  | °C/W |

The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed. This value is limited to 1.975 V maximum.

### DC and AC Specifications

The SSTE32882HLB parametric values are specified for the device default control word settings, unless otherwise stated. Note that RC10 setting does not affect any of the parametric values.

<sup>2</sup> The package thermal impedance is calculated in accordance with JESD51-2.

## **DC** Specifications - Voltage

The SSTE32882 parametric values are specified for the device default control word settings, unless otherwise stated. Note that the RC10 setting does not affect any of the parametric values.

| Symbol                   | Parameter                                                                              | Signals                                                                   | Min                                          | Nom                   | Max                             | Unit |

|--------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------|-----------------------|---------------------------------|------|

| $V_{DD}$                 | DC Supply voltage (1.5V Operation)                                                     |                                                                           | 1.425                                        | 1.5                   | 1.575                           | V    |

|                          | DC Supply voltage (1.35V Operation)                                                    |                                                                           | 1.282                                        | 1.35                  | 1.451                           | V    |

| $V_{REF}$                | DC Reference voltage                                                                   |                                                                           | 0.49 x V <sub>DD</sub>                       | $0.50 \times V_{DD}$  | $0.51 \times V_{DD}$            | V    |

| $V_{TT}$                 | DC Termination voltage                                                                 |                                                                           | $V_{REF} - 40 \text{ mV}$                    | $V_{REF}$             | $V_{REF}$ + 40 mV               | V    |

| V <sub>IH(AC)</sub>      | AC HIGH-level input voltage (1.5V Operation, DDR3-800/1066/1333)                       | Data inputs <sup>1</sup>                                                  | V <sub>REF</sub> + 175 mV                    | _                     | $V_{\rm DD} + 0.4$              | V    |

|                          | AC HIGH-level input voltage (1.5V Operation, DDR3-1600)                                | Data inputs <sup>1</sup>                                                  | $V_{REF} + 150 \text{ mV}$                   | _                     | $V_{DD} + 0.4$                  | V    |

|                          | AC HIGH-level input voltage (1.35V Operation, DDR3L-800/1066/1333)                     | Data inputs <sup>1</sup>                                                  | V <sub>REF</sub> + 150 mV                    | -                     | $V_{\rm DD} + 0.2$              | V    |

|                          | AC HIGH-level input voltage (1.35V Operation, DDR3L-1600)                              | Data inputs <sup>1</sup>                                                  | V <sub>REF</sub> + 135 mV                    | _                     | $V_{DD} + 0.2$                  | V    |

| V <sub>IL(AC)</sub>      | AC LOW-level input voltage (1.5V Operation, DDR3-800/1066/1333)                        | Data inputs <sup>1</sup>                                                  | -0.4                                         | -                     | V <sub>REF</sub> – 175 mV       | V    |

|                          | AC LOW-level input voltage (1.5V Operation, DDR3-1600)                                 | Data inputs <sup>1</sup>                                                  | -0.4                                         | -                     | V <sub>REF</sub> – 150 mV       | V    |

|                          | AC LOW-level input voltage(1.35V Operation, DDR3L-800/1066/1333)                       | Data inputs <sup>1</sup>                                                  | -0.2                                         | -                     | V <sub>REF</sub> – 150 mV       | V    |

|                          | AC LOW-level input voltage (1.35V Operation, DDR3L-1600)                               | Data inputs <sup>1</sup>                                                  | -0.2                                         | -                     | $V_{REF} - 135 \text{ mV}$      | V    |

| V <sub>IH(DC)</sub>      | DC HIGH-level input voltage(1.5V Operation)                                            | Data inputs <sup>1</sup>                                                  | $V_{REF} + 100 \text{ mV}$                   | _                     | $V_{DD} + 0.4$                  | V    |

|                          | DC HIGH-level input voltage(1.35V Operation)                                           | Data inputs <sup>1</sup>                                                  | $V_{REF} + 90 \text{ mV}$                    | _                     | $V_{DD} + 0.2$                  | V    |

| V <sub>IL(DC)</sub>      | DC LOW-level input voltage(1.5V Operation)                                             | Data inputs <sup>1</sup>                                                  | -0.4                                         | _                     | V <sub>REF</sub> – 100 mV       | V    |

| , ,                      | DC LOW-level input voltage(1.35V Operation)                                            | Data inputs <sup>1</sup>                                                  | -0.2                                         | -                     | V <sub>REF</sub> - 90 mV        | V    |

| V <sub>IH(CMO</sub>      | HIGH-level input voltage                                                               | CMOS inputs <sup>2</sup>                                                  | 0.65 x VDD                                   | -                     | V <sub>DD</sub>                 | V    |

| V <sub>IL(CMO</sub>      | LOW-level input voltage                                                                | CMOS inputs <sup>2</sup>                                                  | 0                                            | -                     | 0.35 x VDD                      | V    |

| V <sub>IL</sub> (Static) | Static LOW-level input voltage <sup>3</sup>                                            | $CK, \overline{CK},$                                                      | -                                            | -                     | 0.35 x VDD                      | V    |

| V <sub>IX(AC)</sub>      | Differential input crosspoint voltage range(1.5V Operation, DDR3-800/1066/1333/1600)   | $CK$ , $\overline{CK}$ , $\overline{FBIN}$                                | 0.5xV <sub>DD</sub> - 175<br>mV              | 0.5 x V <sub>DD</sub> | 0.5xV <sub>DD</sub> + 175<br>mV | V    |

|                          |                                                                                        |                                                                           | 0.5xV <sub>DD</sub> - 200<br>mV <sup>4</sup> | 0.5 x V <sub>DD</sub> | $0.5xV_{DD} + 200$ $mV^4$       | V    |

|                          | Differential input crosspoint voltage range(1.35V Operation, DDR3L-800/1066/1333/1600) | $\overline{CK}$ , $\overline{CK}$ , $\overline{FBIN}$ , $\overline{FBIN}$ | 0.5xV <sub>DD</sub> - 150<br>mV              | 0.5 x V <sub>DD</sub> | 0.5xV <sub>DD</sub> + 150<br>mV | V    |

|                          |                                                                                        |                                                                           | 0.5xV <sub>DD</sub> - 180<br>mV <sup>5</sup> | 0.5 x V <sub>DD</sub> | $0.5xV_{DD} + 180$ $mV^5$       | V    |

| V <sub>ID(AC)</sub>      | Differential input voltage <sup>6</sup> (1.5V Operation, DDR3-800/1066/1333)           | CK, CK                                                                    | 350                                          | _                     | $V_{\mathrm{DD}}$               | mV   |

|                          | Differential input voltage <sup>6</sup> (1.5V Operation, DDR3-1600)                    | CK, CK                                                                    | 300                                          | -                     | $V_{\mathrm{DD}}$               | mV   |

|                          | Differential input voltage <sup>6</sup> (1.35V Operation, DDR3-800/1066/1333)          | CK, CK                                                                    | 300                                          | _                     | $V_{\mathrm{DD}}$               | mV   |

|                          | Differential input voltage <sup>6</sup> (1.35V Operation, DDR3-1600)                   | CK, CK                                                                    | 270                                          | _                     | $V_{\mathrm{DD}}$               | mV   |

| $I_{OH}$                 | HIGH-level output current <sup>7</sup>                                                 | All outputs except ERROUT                                                 | -11                                          | -                     | _                               | mA   |

| $I_{OL}$                 | LOW-level output current <sup>7</sup>                                                  | All outputs except<br>ERROUT                                              | 11                                           | _                     |                                 | mA   |

#### SSTE32882HLB

#### 1.35V/1.5V REGISTERING CLOCK DRIVER WITH PARITY TEST AND QUAD CHIP SELECT COMMERCIAL TEMPERATURE

| Symbol                  | Parameter                                                | Signals             | Min                                         | Nom              | Max                                         | Unit |

|-------------------------|----------------------------------------------------------|---------------------|---------------------------------------------|------------------|---------------------------------------------|------|

| $I_{OL}$                | LOW-level output current                                 | ERROUT              | 25                                          | _                | _                                           | mA   |

| $V_{OD}$                | Differential re-driven clock swing (1.5V Operation)      | Yn, <del>Yn</del>   | 500                                         | _                | $V_{\mathrm{DD}}$                           | mV   |

|                         | Differential re-driven clock swing (1.35V Operation)     | Yn, <del>Yn</del>   | 450                                         | _                | $V_{\mathrm{DD}}$                           | mV   |

| V <sub>OX</sub>         | Differential Output Crosspoint Voltage (1.5V Operation)  | $Yn, \overline{Yn}$ | 0.5xV <sub>DD</sub> - 100<br>mV             | _                | $0.5xV_{DD} + 100$ $mV$                     | V    |

|                         | Differential Output Crosspoint Voltage (1.35V Operation) | Yn, <del>Yn</del>   | $0.5 \text{xV}_{\text{DD}} - 90 \text{ mV}$ | _                | $0.5 \text{xV}_{\text{DD}} + 90 \text{ mV}$ | V    |

|                         |                                                          | DDR3-800            | DDR3-1066                                   | DDR3-133         | DDR3-1600                                   |      |

| T <sub>case</sub> (max) | Case temperature <sup>8</sup>                            | 109 <sup>9</sup>    | 108 <sup>9</sup>                            | 106 <sup>9</sup> | 103 <sup>9</sup>                            | °С   |

- 1 DCKE0/1, DODT0/1, DA0..DA15, DBA0..DBA2,  $\overline{DRAS}$ ,  $\overline{DCAS}$ ,  $\overline{DWE}$ , PAR IN,  $\overline{DCS[1:0]}$  when  $\overline{QCSEN}$  = HIGH,  $\overline{DCS[3:0]}$  when  $\overline{QCSEN}$  = LOW.

- 2 RESET, MIRROR

- 3 This spec applies only when both CK and  $\overline{\text{CK}}$  are actively driven LOW. It does not apply when  $\overline{\text{CK/CK}}$  are floating.

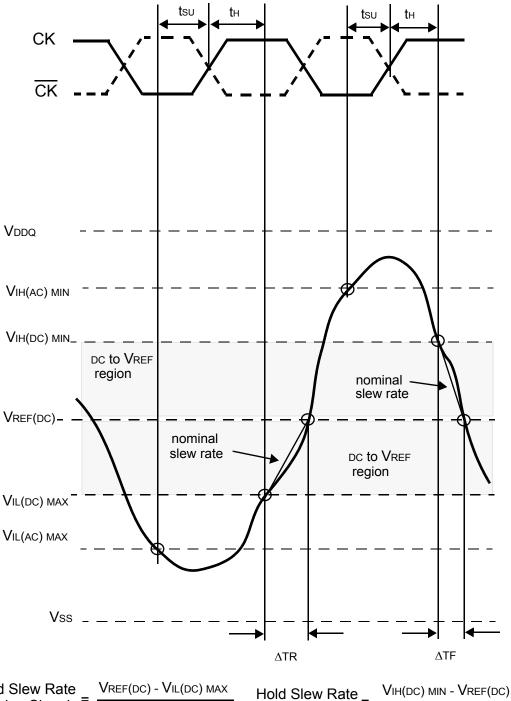

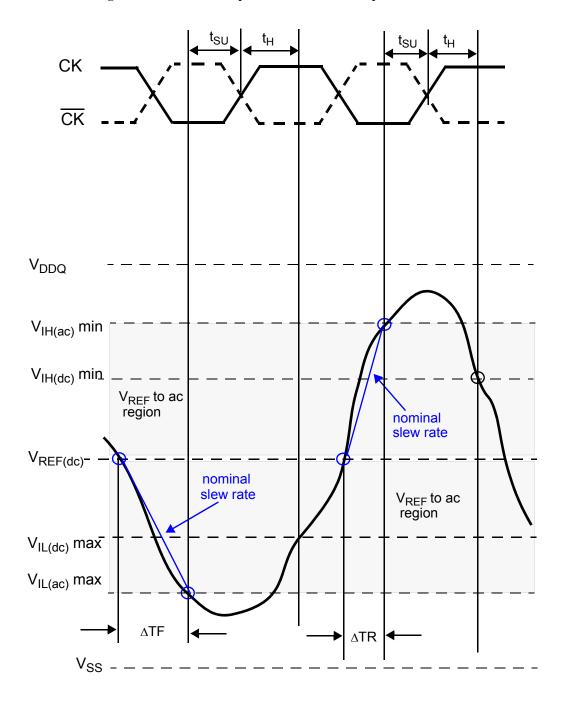

- 4 Extended range for Vix is only allowed for clock (CK and  $\overline{CK}$ ) and if single-ended clock input signals CK and  $\overline{CK}$  are monotonic with a single-ended swing VSEL / VSEH of at least VDD/2 +/-275 mV, and when the differential slew rate of CK  $\overline{CK}$  is larger than 4 V/ns.

- 5 Extended range for Vix is only allowed for clock (CK and  $\overline{CK}$ ) and if single-ended clock input signals CK and  $\overline{CK}$  are monotonic with a single-ended swing VSEL / VSEH of at least VDD/2 +/-243 mV, and when the differential slew rate of CK  $\overline{CK}$  is larger than 3.6 V/ns

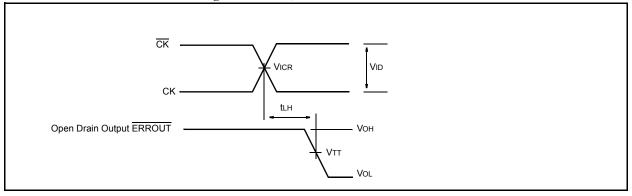

- 6 VID is the magnitude of the difference between the input level on CK and the input level on CK See Diagram (Voltage waveforms; input clock)

- 7 Default settings

- 8 Measurement procedure JESD51-2

- 9 This spec is meant to guarantee a Tj of 125C by the SSTE32882 device. Since Tj cannot be measured or observed by users, Tcase is specified instead. Under all thermal condition, the Tj of a SSTE32882 device shall not be higher than 125 °C.

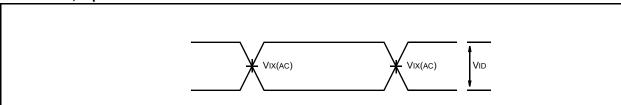

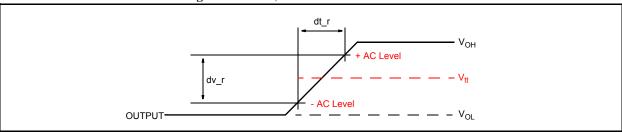

#### Voltage waveforms; input clock

$VIX(AC) = 0.5XV_{DD} \pm 175 \text{ mV} (1.5V \text{ operation}) \text{ or } 0.5XV_{DD} \pm 150 \text{ mV} (1.35 \text{ V operation})$

### **DC Current Specifications**

### **Operating Electrical Characteristics**

| Symbol           | Parameter <sup>1</sup>                             | Conditions                                                                                                                                                                                                                                 | Min  | Typ <sup>2</sup> | Max | Unit                        |

|------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|-----|-----------------------------|

| II               | Input current                                      | $\overline{\text{RESET}}$ , MIRROR, VI = VDD or GND                                                                                                                                                                                        |      |                  | ±5  |                             |

| 11               | QCSEN input current                                | $\overline{\text{QCSEN}}$ , VI = VDD or GND                                                                                                                                                                                                | -150 |                  | 5   | μΑ                          |

| IID              | Input current                                      | Data inputs <sup>3</sup> , VI = VDD or GND                                                                                                                                                                                                 |      |                  | ±5  | μА                          |

| ПБ               | input current                                      | $CK$ , $\overline{CK}^4$ ; $VI = VDD$ or $GND$                                                                                                                                                                                             | -5   |                  | 150 | μΑ                          |

| Іон              | HIGH-level output current                          | Qn <sup>5</sup>                                                                                                                                                                                                                            | -11  |                  |     | mA                          |

| ЮН               | mon-level output current                           | $Yn, \overline{Yn}, FBOUT, \overline{FBOUT}$                                                                                                                                                                                               | -11  |                  |     | mA                          |

|                  |                                                    | Qn <sup>5</sup>                                                                                                                                                                                                                            | 11   |                  |     | mA                          |