# Local Temperature Sensor

# Description

The TS3000GB2A1 digital temperature sensor with accuracy up to  $\pm 0.5^{\circ}$ C was designed to target applications demanding highest level of temperature readout. The sensor is fully compliant with JEDEC JC42.4 Component Specification.

The digital temperature sensor comes with several user-programmable registers to provide maximum flexibility for temperature-sensing applications. The registers allow specifying critical, upper, and lower temperature limits as well as hysteresis settings. Both the limits and hysteresis values are used for communicating temperature events from the chip to the system. This communication is done using Event pin, which has an open-drain configuration. The user has the option of setting the Event pin polarity as either an active-low or active-high comparator output for thermostat operation, or as a temperature event interrupt output for microprocessor-based systems.

The sensor uses an industry standard 2-wire, I<sup>2</sup>C/SMBus serial interface, and allows up to eight devices to be controlled on the bus.

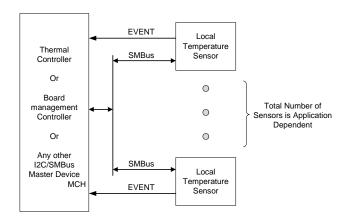

# **Typical Server or Laptop Applications**

## Features

- Temperature Sensor

- Single Supply: 2.3V to 3.6V

- Accurate timeout support - Meets strict SMBus spec of 25ms (min) 35ms (max)

- Timeout supported in all Modes

- Active mode

- Shutdown mode

- Schmitt trigger and noise filtering on bus inputs

- 2-wire Serial Interface: 10-400 kHz I<sup>2</sup>C<sup>™</sup> /SMBus<sup>™</sup>

- Available Packages: DFN-8, TDFN-8

## **Temperature Sensor Features**

- Temperature Converted to Digital Data

- Sampling Rate of 100ms (max)

- Selectable 0, 1.5°C, 3°C, 6°C Hysteresis

- Programmable Resolution from 0.0625°C to 0.5°C

- Accuracy:

- ±0.5°C/ ±1.0°C (typ/max)from +75°C to +95°C

## **Typical Applications**

- DIMM Modules (DDR2, DDR3), SSD Boards

- Servers, Laptops, Ultra-portables, PC Boards

- High end audio / video equipment

- Portable devices

- Hard Disk Drives and Other PC Peripherals

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

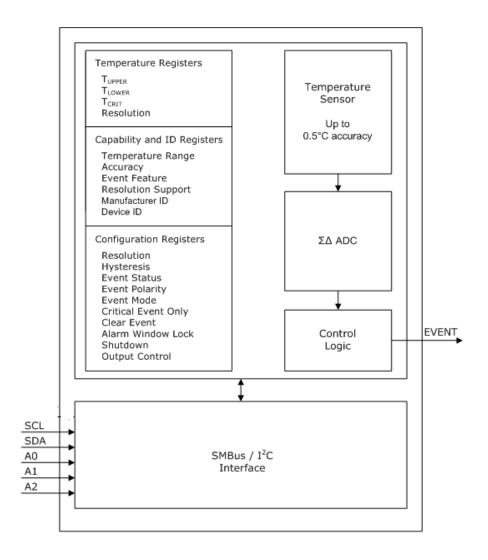

# **Block Diagram: Temperature Sensor**

## **Maximum Ratings**

Stressing the device above the rating listed in the Absolute Maximum Ratings table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

## **Absolute Maximum Ratings**

| Symbol           | Parameter                         | Min.  | Max. | Units |

|------------------|-----------------------------------|-------|------|-------|

| T <sub>STG</sub> | Storage Temperature               | -65   | 150  | °C    |

| V <sub>IO</sub>  | Input or output range, SA0        | -0.50 | 10   | V     |

|                  | Input or output range, other pins | -0.50 | 4.3  | V     |

| V <sub>DD</sub>  | Supply Voltage                    | -0.5  | 4.3  | V     |

## **DC and AC Parameters**

This section summarizes the operating and measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC and AC Characteristic tables that follow are derived from tests performed under the Measurement Conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parameters. DC Characteristics

## **Operating Conditions**

| Symbol          | Parameter                     | Min. | Max. | Units |

|-----------------|-------------------------------|------|------|-------|

| V <sub>DD</sub> | Supply Voltage                | 2.3  | 3.6  | V     |

| T <sub>A</sub>  | Ambient operating temperature | -20  | 125  | °C    |

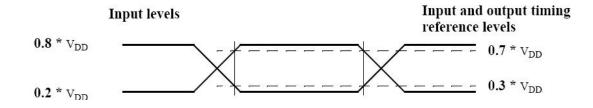

## **AC Measurement Conditions**

| Symbol         | Parameter                                | Min.                | Max.                    | Units |

|----------------|------------------------------------------|---------------------|-------------------------|-------|

| C <sub>L</sub> | Load capacitance                         |                     | 100                     | pF    |

|                | Input rise and fall times                |                     | 50                      | ns    |

|                | Input levels                             | 0.2*V <sub>DI</sub> | to 0.8*V <sub>DD</sub>  | V     |

|                | Input and output timing reference levels | 0.3*V <sub>DI</sub> | oto 0.7*V <sub>DD</sub> | V     |

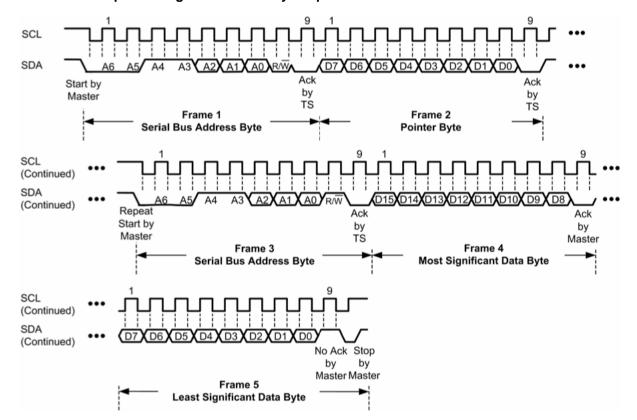

## AC Measurement I/O Waveform

## **Input Parameters for the TS3000GB2A1**

| Symbol           | Parameter <sup>1,2</sup>             | Test Condition                         | Min. | Max. | Units |

|------------------|--------------------------------------|----------------------------------------|------|------|-------|

| C <sub>IN</sub>  | Input capacitance (SDA)              |                                        |      | 8    | pF    |

| C <sub>IN</sub>  | Input rise and fall times            |                                        |      | 6    | ns    |

| Z <sub>EIL</sub> | Ei (SA0,SA1,SA2) input impedance     | $V_{IN} < 0.3 * V_{DD}$                | 30   |      | kΩ    |

| Z <sub>EIH</sub> | Ei (SA0,SA1,SA2) input impedance     | $V_{IN} > 0.7* V_{DD}$                 | 800  |      | kΩ    |

| t <sub>SP</sub>  | Pulse width ignored (input filter on | Single glitch, $f \le 100 \text{ KHz}$ |      | 100  | ns    |

|                  | SCL and SDA)                         | Single glitch, f> 100 KHz              |      | 50   |       |

1.T<sub>A</sub>=25°C, f=400 kHz

2. Verified by design and characterization not necessarily tested on all devices

## **DC Characteristics**

| Parameter                          | Symbol            | Conditions                                                                     | Min.                 | Max.                | Units |

|------------------------------------|-------------------|--------------------------------------------------------------------------------|----------------------|---------------------|-------|

| Input Leakage Current              | I <sub>LI</sub>   | $V_{IN} = V_{SS} \text{ or } V_{DD}$                                           |                      | ±1                  | μΑ    |

| Output Leakage Current             | I <sub>LO</sub>   | $V_{OUT} = V_{SS} \text{ or } V_{DD},$<br>SDA in Hi-Z                          |                      | ±1                  | μΑ    |

| Supply Current, temp sensor active | I <sub>DD</sub>   | $V_{DDSPD} = 3.3 \text{ V}, f_C = 100 \text{ kHz}$<br>(rise/fall time < 30 ns) |                      | 500                 | μΑ    |

| Standby Supply Current             | I <sub>DD1</sub>  | $V_{IN} = V_{SS} \text{ or } V_{DD},$<br>VDD= 3.6 V                            |                      | 40                  | μΑ    |

| Input Low Voltage (SCL, SDA)       | V <sub>IL</sub>   |                                                                                | -0.5                 | 0.3*V <sub>DD</sub> | V     |

| Input High Voltage (SCL, SDA)      | V <sub>IH</sub>   |                                                                                | 0.7* V <sub>DD</sub> | V <sub>DD</sub> +1  | V     |

| SA0 High Voltage                   | V <sub>HV</sub>   | $V_{\rm HV}$ - $V_{\rm DD} \ge 4.8 \ V$                                        | 7                    | 10                  | V     |

| Output Low Voltage                 | V <sub>OL</sub>   | $I_{OL} = 2.1 \text{ mA},$<br>3 V = $\leq$ V <sub>DD</sub> = $\leq$ 3.6 V      |                      | 0.4                 | V     |

|                                    |                   | $I_{OL} = 0.7 \text{ mA},$<br>$V_{DD} = 1.7 - 3.6 \text{ V}$                   |                      | 0.2                 | V     |

| Input hysteresis                   | V <sub>HYST</sub> | $V_{DD} \ge 2.2V$                                                              | $0.05*V_{DD}$        |                     | V     |

## AC Characteristics

|                                                             |                                   | $V_{DD} \ge 2.2 \text{ V}$ |      |       |

|-------------------------------------------------------------|-----------------------------------|----------------------------|------|-------|

| Parameter                                                   | Symbol                            | Min.                       | Max. | Units |

| Clock Frequency                                             | f <sub>SCL</sub>                  | 10                         | 400  | kHz   |

| Clock Pulse Width High Time                                 | t <sub>HIGH</sub>                 | 600                        |      | ns    |

| Clock Pulse Width Low Time                                  | t <sub>LOW</sub> <sup>5</sup>     | 1300                       |      | ns    |

| Detect clock low timeout, Capabilities<br>Register bit 6 =1 | t <sub>TIMEOUT</sub> <sup>6</sup> | 25                         | 35   | ms    |

| SDA Rise Time                                               | t <sub>R</sub> <sup>2</sup>       |                            | 300  | ns    |

| SDA Fall Time                                               | $t_{\rm F}^2$                     | 20                         | 300  | ns    |

| Data In Setup Time                                          | t <sub>SU:DAT</sub>               | 100                        |      | ns    |

| Data In Hold Time                                           | t <sub>HD:DI</sub>                | 0                          |      | ns    |

| Data Out Hold Time                                          | t <sub>HD:DAT</sub>               | 200                        | 900  | ns    |

| Start Condition Setup Time                                  | t <sub>SU:STA</sub> 1             | 600                        |      | ns    |

| Start Condition Hold Time                                   | t <sub>HD:STA</sub>               | 600                        |      | ns    |

| Stop Condition Setup Time                                   | t <sub>SU:STO</sub>               | 600                        |      | ns    |

| Time Between Stop Condition and Next<br>Start Condition     | t <sub>BUF</sub>                  | 1300                       |      | ns    |

| Write Time                                                  | t <sub>W</sub>                    |                            | 4.5  | ms    |

1. For a RESTART condition, or following a write cycle.

- 2. Guaranteed by design and characterization, not necessarily tested.

- 3. To avoid spurious START and STOP conditions, a minimum delay is placed between falling edge of SCL and the falling or rising edge of SDA.

- 4. The TS3000GB2A1 does not initiate clock stretching which is an optional  $I^2C$  bus feature

5. Devices participating in a transfer can abort the transfer in progress and release the bus when any single clock low interval exceeds the value of  $t_{TIMEOUT,MIN}$ . After the master in a transaction detects this condition, it must generate a stop condition within or after the current data byte in the transfer process. Devices that have detected this condition must reset their communication and be able to receive a new START condition no later than  $t_{TIMEOUT,MAX}$ . Typical device examples include the host controller and embedded controller and most devices that can master the SMBus. Some devices do not contain a clock low drive circuit; this simple kind of device typically may reset its communications port after a start or stop condition. A timeout condition can only be ensured if the device that is forcing the timeout holds SCL low for  $t_{TIMEOUT,MAX}$  or longer.

6. The temperature sensor family of devices are not required to support the SMBus ALERT function.

## **Temperature-to-Digital Conversion Performance**

| Parameter                   | Тур  | Max  | Unit | Test Conditions <sup>1</sup>            |

|-----------------------------|------|------|------|-----------------------------------------|

| Temperature Sensor Accuracy | ±0.5 | ±1.0 | °C   | $75^{\circ}C \leq T_A \leq 95^{\circ}C$ |

|                             | ±1.0 | ±2.0 | °C   | $40^\circ C \leq T_A \leq 125^\circ C$  |

|                             | ±2.0 | ±3.0 | °C   | $-20^\circ C \le T_A \le 125^\circ C$   |

1.  $V_{DDMIN} \le V_{DD} \le V_{DDMAX}$

## **Temperature Conversion Time**

| Resolution           | ADC Setting | t <sub>CONV</sub> (typ) | t <sub>CONV</sub> (Max) | Unit |

|----------------------|-------------|-------------------------|-------------------------|------|

| 0.5°C                | 9 bit       |                         | 100                     | ms   |

| 0.25°C (POR default) | 10 bit      |                         | 100                     | ms   |

| 0.125°C              | 11 bit      |                         | 100                     | ms   |

| 0.0625°C             | 12 bit      |                         | 100                     | ms   |

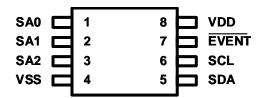

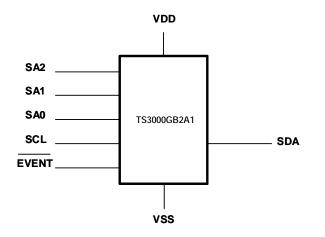

## Pin Assignment

## **Pin Description**

| Pin # | Pin Name        | Definition            |

|-------|-----------------|-----------------------|

| 1     | SA0             | Select Address 0      |

| 2     | SA1             | Select Address 1      |

| 3     | SA2             | Select Address 2      |

| 4     | V <sub>SS</sub> | Ground                |

| 5     | SDA             | Serial Data In        |

| 6     | SCL             | Serial Clock In       |

| 7     | EVENT           | Temperature Event Out |

| 8     | V <sub>DD</sub> | Supply Voltage        |

## **Pin Functional Descriptions**

## Serial Clock (SCL)

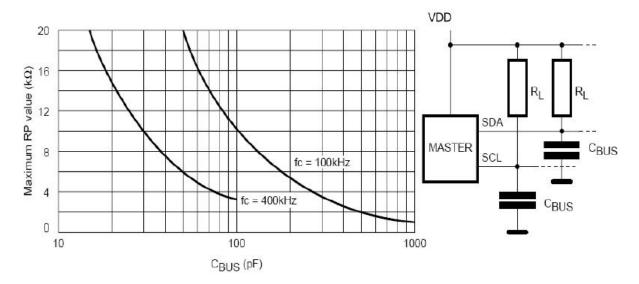

This input signal is used to strobe all data in and out of the device. In applications where this signal is used by slave devices to synchronize the bus to a slower clock, the bus master must have an open drain output, and a pull-up resistor can be connected from Serial Clock (SCL) to  $V_{DD}$ . (refer to the Maximum  $R_L$  Value vs. Bus Capacitance figure on how the value of the pull-up resistor can be calculated). In most applications, though, this method of synchronization is not employed, and so the pull-up resistor is not necessary, provided that the bus master has a push-pull (rather than open drain) output.

## Serial Data (SDA)

This bi-directional signal is used to transfer data in or out of the device. It is an open drain output that may be wire-ORed with other open drain or open collector signals on the bus. A pull up resistor must be connected from Serial Data (SDA) to the most positive  $V_{DD}$  in the  $I^2C$  chain. (refer to the Maximum  $R_L$  Value vs. Bus Capacitance figure on how the value of the pull-up resistor can be calculated).

## Maximum $R_L$ Value vs. Bus Capacitance ( $C_{BUS}$ ) for an $I^2C$ Bus

## Select Address (SA0, SA1, SA2)

These input signals are used to set the value that is to be looked for on the three least significant bits (b3, b2, b1) of the 7-bit Slave Address. In the end application, SA0, SA1 and SA2 must be directly (not through a pull-up or pull-down resistor) connected to  $V_{DD}$  or  $V_{SS}$  to establish the Slave Address. When these inputs are not connected, an internal pull-down circuitry makes (SA0, SA1, SA2) = (0, 0, 0).

## **EVENT**

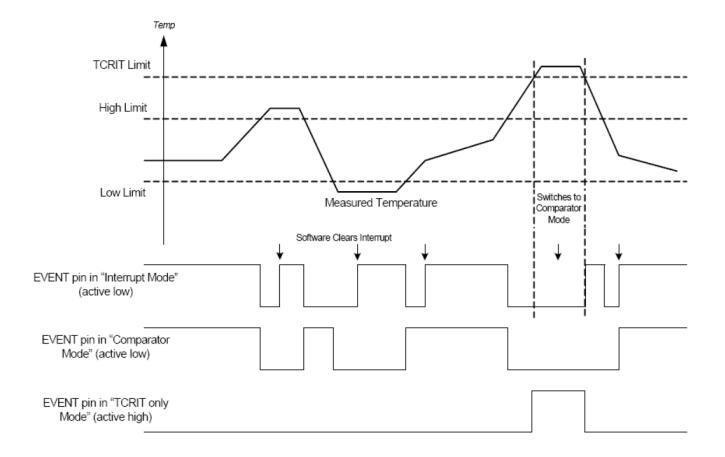

The TS3000GB2A1  $\overline{\text{EVENT}}$  pin is an open drain output that requires a pull-up to V<sub>DD</sub> on the system motherboard or integrated into the master controller. The TS3000GB2A1  $\overline{\text{EVENT}}$  pin has three operating modes, depending on configuration settings and any current out-of-limit conditions. These modes are Interrupt, Comparator, or TCRIT Only.

In Interrupt Mode the EVENT pin will remain asserted until it is released by writing a '1' to the "Clear Event" bit in the Status Register. The value to write is independent of the EVENT polarity bit.

In Comparator Mode the EVENT pin will clear itself when the error condition that caused the pin to be asserted is removed. When the temperature is compared against the TCRIT limit, then this mode is always used.

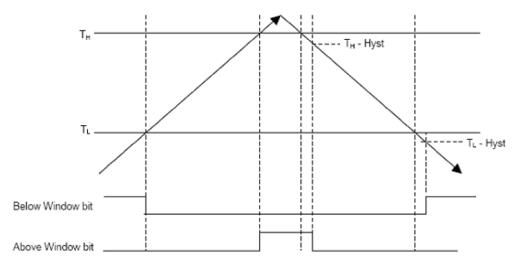

Finally, in the TCRIT Only Mode the EVENT pin will only be asserted if the measured temperature exceeds the TCRIT Limit. Once the pin has been asserted, it will remain asserted until the temperature drops below the TCRIT Limit minus the TCRIT hysteresis. The next figure illustrates the operation of the different modes over time and temperature.

Systems that use the active high mode for EVENT must be wired point to point between the TS3000GB2A1 and the sensing controller. Wire-OR configurations should not be used with active high EVENT since any device pulling the EVENT signal low will mask the other devices on the bus. Also note that the normal state of EVENT in active high mode is a 0 which will continually draw power through the pull-up resistor.

#### **EVENT Pin Mode Functionality**

## **Event Thresholds**

All event thresholds use hysteresis as programmed in register 0x01 bits 10:9 to set when they deassert (stop driving).

#### Alarm Window Trip

The device provides a comparison window with an upper temperature trip point in the Alarm Upper Boundary Register, and a lower trip point in the Alarm Lower Boundary Register. When enabled, the EVENT# output will be triggered whenever entering, or exiting (crossing above or below) the Alarm Window.

#### **Critical Window Trip**

The device can be programmed in such a way that the EVENT# output is only triggered when the temperature exceeds critical trip point. The Critical temperature setting is programmed in Critical Temperature Register. When the temperature sensor reaches the critical temperature value in this register, the device is automatically placed in comparator mode meaning that the Critical Event output cannot be cleared through software setting the "Clear Event" bit.

#### **Interrupt Mode**

After an Event occurs, Software may write a one ('1') to the "Clear Event" bit in the Configuration Register to de-assert the EVENT# Interrupt output, until the next trigger condition occurs.

#### **Comparator Mode**

Reads/writes on the device registers will not affect the EVENT# output in comparator mode. The EVENT# signal will remain asserted until the temperature drops outside the range, or the range is re-programmed such that the current temperature is outside the range.

#### **Serial Communications**

The TS3000GB2A1 temperature sensor circuitry continuously monitors the temperature and updates the temperature data minimum of eight times per second. Temperature data is latched internally by the device and may be read by software from the bus host at any time.

Internal registers are used to configure both the TS performance and response to over-temperature conditions. The device contains programmable high, low, and critical temperature limits. Finally, the device EVENT pin can be configured as active high or active low and can be configured to operate as an interrupt or as a comparator output.

#### **Device Diagram**

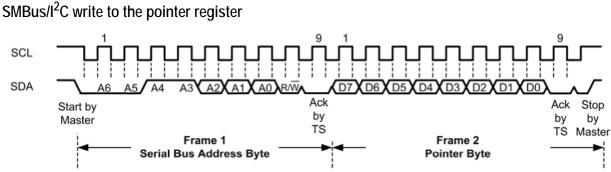

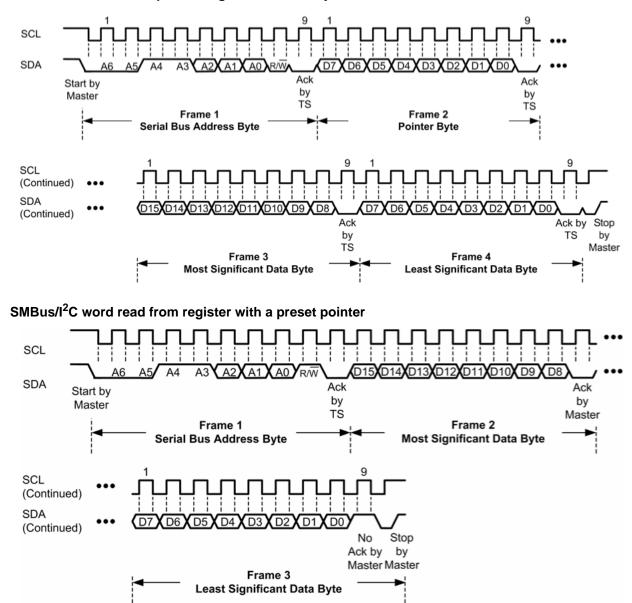

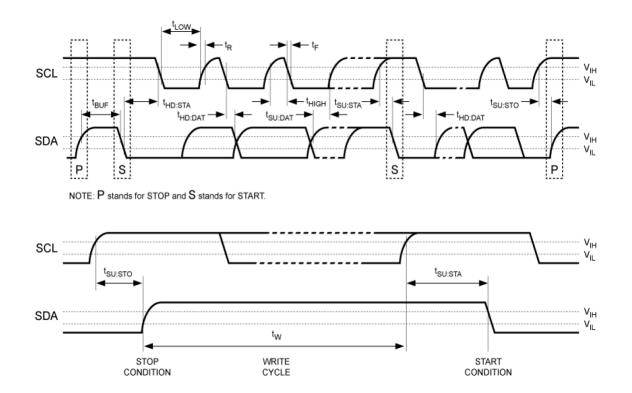

## SMBus/I<sup>2</sup>C Communications

The data registers in this device are selected by the Pointer Register. At power-up the Pointer Register is set to "00", the location for the Capability Register. The Pointer Register latches the last location it was set to. Each data register falls into one of three types of user accessibility:

1. Read only

2. Write only

3. Write/Read same address

A Write to this device will always include the address byte and the pointer byte. A write to any register, other than the pointer register, requires two data bytes.

Reading this device can take place either of two ways:

If the location latched in the Pointer Register is correct (most of the time it is expected that the Pointer Register will point to one of the Read Temperature Registers because that will be the data most frequently read), then the read can simply consist of an address byte, followed by retrieving the two data bytes.

If the Pointer Register needs to be set, then an address byte, pointer byte, repeat start, and another address byte will accomplish a read.

The data byte has the most significant bit first. At the end of a read, this device can accept either Acknowledge (Ack) or No Acknowledge (No Ack) from the Master (No Acknowledge is typically used as a signal for the slave that the Master has read its last byte).

SMBus/I<sup>2</sup>C write to the pointer register followed by a write data word

SMBus/I<sup>2</sup>C write to pointer register followed by a repeat start and an immediate data word read

## SMBus/I<sup>2</sup>C Slave Sub-Address Decoding

The physical address for TS is different than that used by current SPD devices. The physical address for thermal sensor is "0 0 1 1 A2 A1 A0 RW" in binary, where A2, A1, A0 are the three slave sub-address pins, and the least significant bit "RW" is the Read/Write flag.

Assuming the slave base address of the SPD+TS interface is fixed, for example at 0x30, then the pins set the sub-address bits of the slave address, allowing the device to be located anywhere within 8 slave address locations, for example from 0x30 to 0x3E.

| Slave | Address | Decoding |

|-------|---------|----------|

|-------|---------|----------|

| Slave Address | A2 | A1 | A0 |

|---------------|----|----|----|

| x0            | 0  | 0  | 0  |

| x2            | 0  | 0  | 1  |

| x4            | 0  | 1  | 0  |

| x6            | 0  | 1  | 1  |

| x8            | 1  | 0  | 0  |

| хA            | 1  | 0  | 1  |

| xC            | 1  | 1  | 0  |

| хE            | 1  | 1  | 1  |

The meaning of the A0/A1/A2 pin states is as follows:: 0= Pull-down to Thermal Sensor Vss, 1=Pull-up to Thermal Sensor VDD

## SMBus/I2 AC Timing Consideration

In order for this device to be both SMBus and I<sup>2</sup>C compliant, the device complies with a subset of each specification. This requires a few minor considerations to ensure interoperability. The time out requirements of SMBus are optional for this device. The minimum clock frequency of SMBus is a required feature. Note that the minimum data hold time (THD:DAT) of 200 ns is smaller than the 300 ns of the SMBus specification. With these minor considerations, this device is capable of co-existing with devices on either an SMBus or an I<sup>2</sup>C bus.

#### **TS Register Set Definition**

The register set address are shown in the Acknowledge When Writing Data or Defining Write Protection table. These values are used in the I<sup>2</sup>C operations as the "REG\_PTR" as shown in previous figures.

| ADDR | R/W | Name                | Function                                                           | Default |

|------|-----|---------------------|--------------------------------------------------------------------|---------|

| N/A  | W   | Address Pointer     | Address storage for subsequent operations                          | 00      |

| 00   | R   | Capabilities        | Indicates the functions and capabilities of the temperature sensor | 006F    |

| 01   | R/W | Configuration       | Controls the operation of the temperature monitor                  | 0000    |

| 02   | R/W | High Limit          | Temperature High Limit                                             | 0000    |

| 03   | R/W | Low Limit           | Temperature Low Limit                                              | 0000    |

| 04   | R/W | TCRIT Limit         | Critical Temperature                                               | 0000    |

| 05   | R   | Ambient Temperature | Current Ambient temperature                                        | N/A     |

| 06   | R   | Manufacturer ID     | PCI-SIG manufacturer ID                                            | 00B3    |

| 07   | R   | Device/Revision     | Device ID and Revision number                                      | 2912    |

| 08   | R/W | Resolution Register | Allows changing temperature sensor resolution                      | 002F    |

## **Temperature Register Addresses**

## **Capabilities Register**

The Capabilities Register indicates the supported features of the temperature sensor.

#### **Capabilities Register**

| ADDR | R/W  | B15/B7 | B14/B6 | B13/B5 | B12/B4 | B11/B3 | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default |

|------|------|--------|--------|--------|--------|--------|--------|--------------|--------------|---------|

| 00   | D    | RFU          | RFU          | 006F    |

| 00   | 00 R |        | TMOUT  | Х      | TRE    | S[1:0] | RANGE  | ACC          | EVENT        |         |

Bits 15 - Bit 8 – RFU; Reserved for future use. These bits will always read '0' and writing to them will have no affect.

Bit 7- EVSD-EVENT with Shutdown action.

'0' - (default) The EVENT output freezes in its current state when entering shutdown. Upon exiting shutdown, the EVENT output remains in the previous state until the next thermal sample is taken, or possibly sooner if EVENT is programmed for comparator mode.

'1' The EVENT output is deasserted (not driven) when entering shutdown and remains deasserted upon exit from shutdown until the next thermal sample is taken, or possibly sooner if EVENT is programmed for comparator mode.

Bit 6 - TMOUT – Bus timeout period for thermal sensor access during normal operation. Note that the TS3000GB2A1 supports timeout in both active and shutdown mode for temperature sensor and SPD (EEPROM) portions of the device.

'0' - Parameter  $t_{TIMEOUT}$  is supported within the range of 10 to 60 ms.

'1' - (default) Parameter t<sub>TIMEOUT</sub> is supported within the range of 25 to 35 ms (SMBus compatible).

Bit 5 - X – May be 0 or 1; applications must accept either code. (Default =1)

Bits 4 - 3 – TRES[1:0]; Indicates the resolution of the temperature monitor as shown in the TRES Bit Decode table. (Default =01)

## **TRES Bit Decode**

| TRES | S[1:0] | • Temperature Resolution  |  |  |  |  |

|------|--------|---------------------------|--|--|--|--|

| 1    | 0      | Temperature Resolution    |  |  |  |  |

| 0    | 0      | 0.5°C (9-bit)             |  |  |  |  |

| 0    | 1      | 0.25°C (10-bit) (default) |  |  |  |  |

| 1    | 0      | 0.125°C (11-bit)          |  |  |  |  |

| 1    | 1      | 0.0625°C (12-bit)         |  |  |  |  |

Note: Refer to section Resolution Register on page 21.

Bit 2 - RANGE; Indicates the supported temperature range.

'0' - The temperature monitor clamps values lower than 0 °C.

'1' (default) - The temperature monitor can read temperatures below 0 °C and sets the sign bit appropriately.

Bit 1 - ACC; Indicates the supported temperature accuracy.

'0' - The temperature monitor has ±2 °C accuracy of the active range (75 °C to 95 °C) and 3 °C accuracy over the entire operating range.

'1' (default) - Bgrade. The temperature monitor has  $\pm 1$  °C accuracy

Bit 0 - EVENT; Indicates whether the temperature monitor supports interrupt capabilities

'0'.-The device does not support interrupt capabilities.

'1' (default); The device supports interrupt capabilities.

## **Configuration Register**

## **Configuration Register**

| ADDR | R/W | B15/B7         | B14/B6         | B13/B5 | B12/B4        | B11/B3         | B10/B2         | <b>B9/B1</b>  | <b>B8/B0</b>   | Default |

|------|-----|----------------|----------------|--------|---------------|----------------|----------------|---------------|----------------|---------|

|      |     | RFU            | RFU            | RFU    | RFU           | RFU            | HYST           | [1:0]         | SHDN           |         |

| 01   | R/W | TCRIT_<br>LOCK | EVENT_<br>LOCK | CLEAR  | EVENT_<br>STS | EVENT_<br>CTRL | TCRIT_<br>ONLY | EVENT_<br>POL | EVENT_<br>MODE | 0000    |

The Configuration Register holds the control and status bits of the EVENT pin as well as general hysteresis on all limits.

Bits 15 - 11 – RFU; Reserved for future use. These bits will always read '0' and writing to them will have no affect. For future compatibility, all RFU bits must be programmed as '0'.

Bits 10 - 9 – HYST[1:0]; Control the hysteresis that is applied to all limits as shown in the HYST Bit Decode table that follows. This hysteresis applies to all limits when the temperature is dropping below the threshold so that once the temperature is above a given threshold, it must drop below the threshold minus the hysteresis in order to be flagged as an interrupt event. Note that hysteresis is also applied to EVENT pin functionality. When either of the lock bits is set, these bits cannot be altered.

## **Hysteresis**

|        | Below Alarn       | n Window Bit             | Above Alarm Window Bit |                      |  |  |

|--------|-------------------|--------------------------|------------------------|----------------------|--|--|

|        | Temperature slope | Threshold<br>Temperature | Temperature Slope      | Temperature          |  |  |

| Sets   | Falling           | T <sub>L</sub> -Hyst     | Rising                 | Тн                   |  |  |

| Clears | Rising            | TL                       | Falling                | T <sub>H</sub> -Hyst |  |  |

T<sub>LI</sub>= Value stored in Alarm Temperature Upper Boundary Trip Register

T<sub>L</sub>=Value stored in Alarm Temperature Lower Boundary Trip Register

Hyst= Absolute value of selected hysteresis

## **HYST Bit Decode**

| HYS | Г[1:0] | Hysteresis                   |

|-----|--------|------------------------------|

| 1   | 0      | Hysteresis                   |

| 0   | 0      | Disable hysteresis (default) |

| 0   | 1      | 1.5°C                        |

| 1   | 0      | 3°C                          |

| 1   | 1      | 6°C                          |

Bit 8 – SHDN-Shutdown. The thermal sensing device and A/D converters are disabled to save power, no events will be generated. When either of the lock bits is set, this bit cannot be set until unlocked. However it can be cleared at any time. When in shutdown mode, the TS3000GB2A1 still responds to commands normally, however bus timeout may or may not be supported in this mode.

'0' (default); The temperature monitor is active and converting

'1'; The temperature monitor is disabled and will not generate interrupts or update the temperature data.

Bit 7 – TCRIT\_LOCK; Locks the TCRIT Limit Register from being updated.

'0' (default; The TCRIT Limit Register can be updated normally.

'1'; The TCRIT Limit Register is locked and cannot be updated. Once this bit has been set, it cannot be cleared until an internal power on reset.

Bit 6 – EVENT\_LOCK; Locks the High and Low Limit Registers from being updated.

'0' (default); The High and Low Limit Registers can be updated normally.

'1'; The High and Low Limit Registers are locked and cannot be updated. Once this bit has been set, it cannot be cleared until an internal power on reset.

Bit 5 – CLEAR; Clears the EVENT pin when it has been asserted. This bit is write only and will always read '0'.

'0'; does nothing

'1'; The EVENT pin is released and will not be asserted until a new interrupt condition occurs. This bit is ignored if the device is operating in Comparator Mode. This bit is self clearing.

Bit 4 – EVENT\_STS; Indicates if the EVENT pin is asserted. This bit is read only.

'0' (default); The EVENT pin is not asserted.

'1'; The  $\overline{\text{EVENT}}$  pin is being asserted by the device.

Bit 3 – EVENT\_CTRL; Masks the EVENT pin from generating an interrupt. If either of the lock bits are set (bit 7 and bit 6), then this bit cannot be altered.

'0' (default); The EVENT pin is disabled and will not generate interrupts. '1'; The EVENT pin is enabled.

Bit 2 – TCRIT\_ONLY; Controls whether the EVENT pin will be asserted from a high / low out-of-limit condition. When the EVENT\_LOCK bit is set, this bit cannot be altered.

'0' (default); The **EVENT** pin will be asserted if the measured temperature is above the High Limit or below the Low Limit in addition to if the temperature is above the TCRIT Limit.

'I'; The EVENT pin will only be asserted if the measured temperature is above the TCRIT Limit.

Bit 1 – EVENT\_POL; Controls the "active" state of the EVENT pin. The EVENT pin is driven to this state when it is asserted.

'0' (default); The EVENT pin is active low. The "active" state of the pin will be logical '0'.

'1'; The EVENT pin is active high. The "active" state of the pin will be logical '1'.

Bit 0 – EVENT\_MODE; Controls the behavior of the EVENT pin. The EVENT pin may function in either comparator or interrupt mode.

'0'; The EVENT pin will function in comparator mode.

'1'; The EVENT pin will function in interrupt mode.

#### **Temperature Register Value Definitions**

Temperatures in the High Limit Register, Low Limit Register, TCRIT Register, and Temperature Data Register are expressed in two's complement format. Bits B 12 through B2 for each of these registers are defined for all device resolutions as defined in the TRES field of the Capabilities Register, hence a 0.25°C minimum granularity is supported in all registers. Examples of valid settings and interpretation of temperature register bits:

| Temperature Register Coding Examples |       |    |  |  |  |  |  |  |  |

|--------------------------------------|-------|----|--|--|--|--|--|--|--|

| B15~B0 (binary) Value Units          |       |    |  |  |  |  |  |  |  |

| xxx0 0000 0010 11xx                  | +2.75 | °C |  |  |  |  |  |  |  |

| xxx0 0000 0001 00xx                  | +1.00 | °C |  |  |  |  |  |  |  |

| xxx0 0000 0000 01xx                  | +0.25 | °C |  |  |  |  |  |  |  |

| xxx0 0000 0000 00xx                  | 0     | °C |  |  |  |  |  |  |  |

| Temperature Register Coding Examples |       |    |  |  |  |  |  |  |  |

|--------------------------------------|-------|----|--|--|--|--|--|--|--|

| B15~B0 (binary) Value Units          |       |    |  |  |  |  |  |  |  |

| xxx1 1111 1111 11xx                  | -0.25 | °C |  |  |  |  |  |  |  |

| xxx1 1111 1111 00xx                  | -1.00 | °C |  |  |  |  |  |  |  |

| xxx1 1111 1101 01xx                  | -2.75 | °C |  |  |  |  |  |  |  |

The TRES field of the Capabilities Register optionally defines higher resolution devices. For compatibility and simplicity, this additional resolution affects only the Temperature Data Register but none of the Limit Registers. When higher resolution devices generate status or  $\overline{EVENT}$  changes, only bits B12 through B2 are used in the comparison; however, all 11 bits (TRES[1-0] = 10) or all 12 bits (TRES[1-0] = 11) are visible in reads from the Temperature Data Register.

When a lower resolution device is indicated in the Capabilities Register (TRES[1-0] = 00), the finest resolution supported is 0.5°C. When this is detected, bit 2 of all Limit Registers should be programmed to 0 to assure correct operation of the temperature comparators.

## **High Limit Register**

The temperature limit registers (High, Low, and TCRIT) define the temperatures to be used by various on-chip comparators to determine device temperature status and thermal EVENTs. For future compatibility, unused bits "-" must be programmed as 0.

## **High Limit Register**

| ADDR   | R/W | B15/B7 | B14/B6 | B13/B5 | B12/B4 | B11/B3 | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default |

|--------|-----|--------|--------|--------|--------|--------|--------|--------------|--------------|---------|

| 02 R/W | —   | _      | -      | Sign   | 128    | 64     | 32     | 16           | 0000         |         |

|        | 8   | 4      | 2      | 1      | 0.5    | 0.25   | _      |              | 0000         |         |

The High Limit Register holds the High Limit for the nominal operating window. When the temperature rises above the High Limit, or drops below or equal to the High Limit, then the EVENT pin is asserted (if enabled). If the EVENT\_LOCK bit is set as shown in the Configuration Register table), then this register becomes read-only.

## Low Limit Register

#### Low Limit Register

| ADDR   | R/W | B15/B7 | B14/B6 | B13/B5 | B12/B4 | B11/B3 | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default |

|--------|-----|--------|--------|--------|--------|--------|--------|--------------|--------------|---------|

| 03 R/W | —   | _      | _      | Sign   | 128    | 64     | 32     | 16           | 0000         |         |

|        | 8   | 4      | 2      | 1      | 0.5    | 0.25   | _      | _            | 0000         |         |

The Low Limit Register holds the lower limit for the nominal operating window. When the temperature drops below the Low Limit or rises up to meet or exceed the Low Limit, then the EVENT pin is asserted (if enabled). If the EVENT\_LOCK bit is set as shown in the Configuration Register, then this register becomes read-only.

## **TCRIT Limit Register**

## **TCRIT Limit Register**

| ADDR   | R/W | B15/B7 | B14/B6 | B13/B5 | B12/B4 | B11/B3 | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default |

|--------|-----|--------|--------|--------|--------|--------|--------|--------------|--------------|---------|

| 04     |     | —      | _      | —      | Sign   | 128    | 64     | 32           | 16           | 0000    |

| 04 R/W | 8   | 4      | 2      | 1      | 0.5    | 0.25   | —      | —            | 0000         |         |

The TCRIT Limit Register holds the TCRIT Limit. If the temperature exceeds the limit, the EVENT pin will be asserted. It will remain asserted until the temperature drops below or equal to the limit minus hysteresis. If the TCRIT\_LOCK bit is set as shown in the Configuration Register table, then this register becomes read-only.

## **Temperature Data Register**

#### **Temperature Data Register**

| ADDR | R/W | B15/B7 | B14/B6 | B13/B5 | B12/B4 | B11/B3 | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default    |

|------|-----|--------|--------|--------|--------|--------|--------|--------------|--------------|------------|

| 05   | D   | TCRIT  | HIGH   | LOW    | Sign   | 128    | 64     | 32           | 16           | N/A (0000) |

| 03   | К   | 8      | 4      | 2      | 1      | 0.5    | 0.25*  | 0.125*       | 0.0625*      | N/A (0000) |

\* Resolution defined based on value of TRES field of the Capabilities Register. Unused/unsupported bits will read as 0.

The Temperature Data Register holds the 10-bit + sign data for the internal temperature measurement as well as the status bits indicating which error conditions, if any, are active. The encoding of bits B 12 through B0 is the same as for the temperature limit registers.

Bit 15 – TCRIT; When set, the temperature is above the TCRIT Limit. This bit will remain set so long as the temperature is above TCRIT and will automatically clear once the temperature has dropped below the limit minus the hysteresis.

Bit 14 – HIGH; When set, the temperature is above the High Limit. This bit will remain set so long as the temperature is above the HIGH limit. Once set, it will only be cleared when the temperature drops below or equal to the HIGH Limit minus the hysteresis.

Bit 13 – LOW; When set, the temperature is below the Low Limit. This bit will remain set so long as the temperature is below the Low Limit minus the hysteresis. Once set, it will only be cleared when the temperature meets or exceeds the Low Limit.

## **Manufacturer ID Register**

#### **Manufacturer ID Register**

| ADDR   | R/W | B15/B7 | B14/B6 | B13/B5 | B12/B4 | B11/B3 | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default |

|--------|-----|--------|--------|--------|--------|--------|--------|--------------|--------------|---------|

| 06     | DAV | 0      | 0      | 0      | 0      | 0      | 0      | 0            | 0            | 00B3    |

| 06 R/W | 1   | 0      | 1      | 1      | 0      | 0      | 1      | 1            | 0005         |         |

The Manufacturer ID Register holds the PCI SIG number assigned to the specific manufacturer.

#### **Device ID/Revision Register**

#### **Device ID/Revision Register**

| ADDR | R/W | B15/B7 | B14/B6 | B13/B5 | B12/B4 | B11/B3 | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default |

|------|-----|--------|--------|--------|--------|--------|--------|--------------|--------------|---------|

| 07   | R/W | 0      | 0      | 1      | 0      | 1      | 0      | 0            | 1            | 2912    |

|      |     | 0      | 0      | 0      | 1      | 0      | 0      | 1            | 0            |         |

The upper byte of the Device ID / Revision Register stores a unique number indicating the TS3000GB2A1 from other devices. The lower byte holds the revision value.

## **Resolution Register**

This register allows the user to change the resolution of the temperature sensor. The POR default resolution is 0.25°C. The resolution implemented via this register is also reflected in the capability register.

## **Resolution Register**

| ADDR | R/W | B15/B7 | B14/B6 | B13/B5 | B12/B4  | B11/B3  | B10/B2 | <b>B9/B1</b> | <b>B8/B0</b> | Default<br>Value |

|------|-----|--------|--------|--------|---------|---------|--------|--------------|--------------|------------------|

| 08h  | R/W | 0      | 0      | 0      | 0       | 0       | 0      | 0            | 0            | 002F             |

|      |     | 0      | 0      | 1      | TRES[1] | TRES[0] | 1      | 1            | 1            |                  |

#### Legend:

Resolution bits 4-3 TRES[4:3]

00 = LSB = 0.5°C (register value = 0007)

$01 = LSB = 0.25^{\circ}C$  (register value = 000F)

10 = LSB = 0.125°C (register value = 0017)

11 = LSB = 0.0625°C (register value = 001F)

Conversion times for each resolution are less than 100ms (worst case).

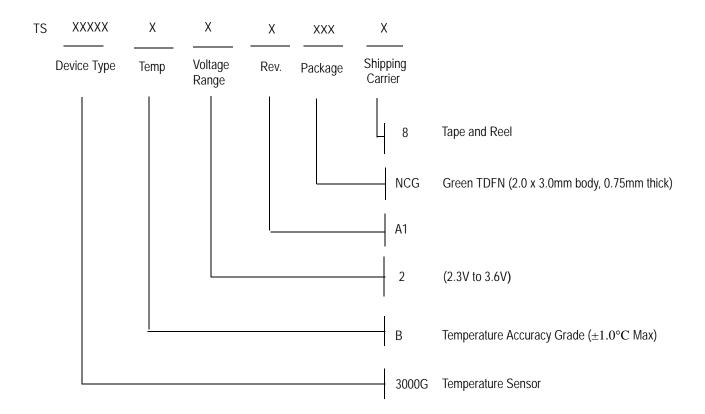

## **Ordering Information**

Example: TS3000GB2A1 NCG8

*CORPORATE HEADQUARTERS* 6024 Silver Creek Valley Road San Jose, CA 95138 for SALES: 800-345-7015 or 408-284-8200 fax: 408-284-2775 www.idt.com *for Tech Support:* email: <u>memorymodule-help@idt.com</u> phone: 408-284-8208