## . . eescale Semiconductor

Technical Data

MRF6S9045NR1 replaced by MRFE6S9045NR1. Refer to Device Migration PCN12895 for more details. MRF6S9045NBR1 no longer manufactured.

**RF Power Field Effect Transistors**

## N-Channel Enhancement-Mode Lateral MOSFETs

Designed for broadband commercial and industrial applications with frequencies up to 1000 MHz. The high gain and broadband performance of these devices make them ideal for large-signal, common-source amplifier applications in 28 volt base station equipment.

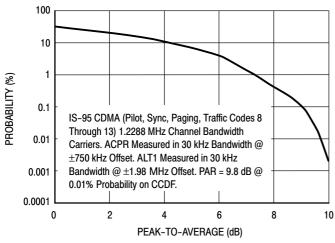

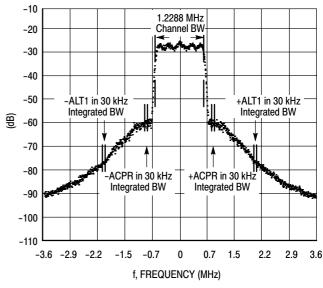

Typical Single-Carrier N-CDMA Performance @ 880 MHz,  $V_{DD}$  = 28 Volts, I<sub>DQ</sub> = 350 mA, P<sub>out</sub> = 10 Watts Avg., IS-95 CDMA (Pilot, Sync, Paging, Traffic Codes 8 Through 13) Channel Bandwidth = 1.2288 MHz. PAR = 9.8 dB @ 0.01% Probability on CCDF.

Power Gain — 22.7 dB

Drain Efficiency — 32%

ACPR @ 750 kHz Offset — -47 dBc in 30 kHz Bandwidth

## **GSM EDGE Application**

• Typical GSM EDGE Performance:  $V_{DD}$  = 28 Volts,  $I_{DQ}$  = 350 mA, P<sub>out</sub> = 16 Watts Avg., Full Frequency Band (921-960 MHz)

Power Gain — 20 dB

Drain Efficiency — 46%

Spectral Regrowth @ 400 kHz Offset = -62 dBc

Spectral Regrowth @ 600 kHz Offset = -78 dBc

**EVM** — 1.5% rms

## **GSM Application**

Typical GSM Performance:  $V_{DD}$  = 28 Volts,  $I_{DQ}$  = 350 mA,  $P_{out}$  = 45 Watts, Full Frequency Band (921-960 MHz)

Power Gain — 20 dB

Drain Efficiency — 68%

Capable of Handling 5:1 VSWR, @ 28 Vdc, 880 MHz, 45 Watts CW **Output Power**

- Characterized with Series Equivalent Large-Signal Impedance Parameters

- Integrated ESD Protection

- 225°C Capable Plastic Package

- N Suffix Indicates Lead-Free Terminations. RoHS Compliant.

- TO-270-2 in Tape and Reel. R1 Suffix = 500 Units per 24 mm,

- TO-272-2 in Tape and Reel. R1 Suffix = 500 Units per 44 mm, 13 inch Reel.

Document Number: MRF6S9045N

Rev. 4, 8/2008

# MRF6S9045NR1 MRF6S9045NBR1

880 MHz, 10 W AVG., 28 V SINGLE N-CDMA LATERAL N-CHANNEL **BROADBAND RF POWER MOSFETs**

**CASE 1265-09, STYLE 1** TO-270-2 PLASTIC MRF6S9045NR1

CASE 1337-04, STYLE 1 TO-272-2 **PLASTIC** MRF6S9045NBR1

## **Table 1. Maximum Ratings**

| Rating                               | Symbol           | Value        | Unit |

|--------------------------------------|------------------|--------------|------|

| Drain-Source Voltage                 | V <sub>DSS</sub> | - 0.5, +68   | Vdc  |

| Gate-Source Voltage                  | V <sub>GS</sub>  | - 0.5, +12   | Vdc  |

| Storage Temperature Range            | T <sub>stg</sub> | - 65 to +150 | °C   |

| Case Operating Temperature           | T <sub>C</sub>   | 150          | °C   |

| Operating Junction Temperature (1,2) | TJ               | 225          | °C   |

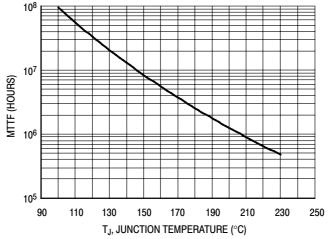

- 1. Continuous use at maximum temperature will affect MTTF.

- 2. MTTF calculator available at http://www.freescale.com/rf. Select Software & Tools/Development Tools/Calculators to access MTTF calculators by product.

## **Table 2. Thermal Characteristics**

| Characteristic                       | Symbol          | Value (1,2) | Unit |

|--------------------------------------|-----------------|-------------|------|

| Thermal Resistance, Junction to Case | $R_{\theta JC}$ |             | °C/W |

| Case Temperature 81°C, 45 W CW       |                 | 1.0         |      |

| Case Temperature 79°C, 10 W CW       |                 | 1.1         |      |

## **Table 3. ESD Protection Characteristics**

| Test Methodology                      | Class        |

|---------------------------------------|--------------|

| Human Body Model (per JESD22-A114)    | 1A (Minimum) |

| Machine Model (per EIA/JESD22-A115)   | A (Minimum)  |

| Charge Device Model (per JESD22-C101) | IV (Minimum) |

## **Table 4. Moisture Sensitivity Level**

| Test Methodology                      | Rating | Package Peak Temperature | Unit |

|---------------------------------------|--------|--------------------------|------|

| Per JESD 22-A113, IPC/JEDEC J-STD-020 | 3      | 260                      | °C   |

## Table 5. Electrical Characteristics (T<sub>C</sub> = 25°C unless otherwise noted)

| Characteristic                                                                              | Symbol           | Min | Тур | Max | Unit |  |

|---------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|--|

| Off Characteristics                                                                         |                  |     |     |     |      |  |

| Zero Gate Voltage Drain Leakage Current (V <sub>DS</sub> = 68 Vdc, V <sub>GS</sub> = 0 Vdc) | I <sub>DSS</sub> | _   | _   | 10  | μAdc |  |

| Zero Gate Voltage Drain Leakage Current (V <sub>DS</sub> = 28 Vdc, V <sub>GS</sub> = 0 Vdc) | I <sub>DSS</sub> | _   | _   | 1   | μAdc |  |

| Gate-Source Leakage Current (V <sub>GS</sub> = 5 Vdc, V <sub>DS</sub> = 0 Vdc)              | I <sub>GSS</sub> | _   | _   | 1   | μAdc |  |

## On Characteristics

| Gate Threshold Voltage ( $V_{DS}$ = 10 Vdc, $I_{D}$ = 200 $\mu$ A)                                           | V <sub>GS(th)</sub> | 1 | 2    | 3   | Vdc |

|--------------------------------------------------------------------------------------------------------------|---------------------|---|------|-----|-----|

| Gate Quiescent Voltage<br>(V <sub>DD</sub> = 28 Vdc, I <sub>D</sub> = 350 mAdc, Measured in Functional Test) | V <sub>GS(Q)</sub>  | 2 | 2.9  | 4   | Vdc |

| Drain-Source On-Voltage<br>(V <sub>GS</sub> = 10 Vdc, I <sub>D</sub> = 1.0 Adc)                              | V <sub>DS(on)</sub> | _ | 0.22 | 0.3 | Vdc |

## **Dynamic Characteristics**

| Input Capacitance ( $V_{DS}$ = 28 Vdc, $V_{GS}$ = 0 Vdc $\pm$ 30 mV(rms)ac @ 1 MHz)                                       | C <sub>iss</sub> | _ | 77   | _ | pF |

|---------------------------------------------------------------------------------------------------------------------------|------------------|---|------|---|----|

| Output Capacitance ( $V_{DS}$ = 28 Vdc $\pm$ 30 mV(rms)ac @ 1 MHz, $V_{GS}$ = 0 Vdc)                                      | C <sub>oss</sub> | _ | 27   | _ | pF |

| Reverse Transfer Capacitance $(V_{DS} = 28 \text{ Vdc} \pm 30 \text{ mV(rms)ac} @ 1 \text{ MHz}, V_{GS} = 0 \text{ Vdc})$ | C <sub>rss</sub> | _ | 0.78 | _ | pF |

Functional Tests (In Freescale Test Fixture, 50 ohm system)  $V_{DD}$  = 28 Vdc,  $I_{DQ}$  = 350 mA,  $P_{out}$  = 10 W Avg., f = 880 MHz, Single-Carrier N-CDMA, 1.2288 MHz Channel Bandwidth Carrier. ACPR measured in 30 kHz Channel Bandwidth @  $\pm$ 750 kHz Offset. PAR = 9.8 dB @ 0.01% Probability on CCDF

| Power Gain                                     | G <sub>ps</sub> | 21   | 22.7       | 25       | dB  |

|------------------------------------------------|-----------------|------|------------|----------|-----|

| Drain Efficiency                               | $\eta_{D}$      | 30.5 | 32         | _        | %   |

| Adjacent Channel Power Ratio                   | ACPR            | _    | -47        | - 45     | dBc |

| Input Return Loss  MRF6S9045NR1  MRF6S9045NBR1 | IRL             | _    | -20<br>-20 | -9<br>-7 | dB  |

MTTF calculator available at <a href="http://www.freescale.com/rf">http://www.freescale.com/rf</a>. Select Software & Tools/Development Tools/Calculators to access MTTF calculators by product.

(continued)

<sup>2.</sup> Refer to AN1955, *Thermal Measurement Methodology of RF Power Amplifiers*. Go to <a href="http://www.freescale.com/rf">http://www.freescale.com/rf</a>. Select Documentation/Application Notes - AN1955.

Table 5. Electrical Characteristics (T<sub>C</sub> = 25°C unless otherwise noted) (continued)

| Charac | teristic | Symbol | Min     | Тур | Max | Unit |

|--------|----------|--------|---------|-----|-----|------|

|        |          |        | <b></b> |     |     |      |

$\begin{tabular}{ll} \textbf{Typical GSM EDGE Performances} & (In Freescale GSM EDGE Test Fixture Optimized for 921-960 MHz, 50 ohm system) \\ V_{DD} = 28 \ Vdc, \ I_{DQ} = 350 \ mA, \ P_{out} = 16 \ W \ Avg., \ f = 921-960 \ MHz, \ GSM EDGE Signal \\ \end{tabular}$

| Power Gain                          | G <sub>ps</sub> | _ | 20  | _ | dB  |

|-------------------------------------|-----------------|---|-----|---|-----|

| Drain Efficiency                    | $\eta_{D}$      | _ | 46  | _ | %   |

| Error Vector Magnitude              | EVM             | _ | 1.5 | _ | %   |

| Spectral Regrowth at 400 kHz Offset | SR1             | _ | -62 | _ | dBc |

| Spectral Regrowth at 600 kHz Offset | SR2             | = | -78 | = | dBc |

$\textbf{Typical CW Performances} \text{ (In Freescale GSM Test Fixture Optimized for 921-960 MHz, 50 ohm system) } V_{DD} = 28 \text{ Vdc}, \\ I_{DQ} = 350 \text{ mA, } P_{out} = 45 \text{ W, } f = 921-960 \text{ MHz}$

| Power Gain                                                 | $G_{ps}$   | _ | 20  | _ | dB |

|------------------------------------------------------------|------------|---|-----|---|----|

| Drain Efficiency                                           | $\eta_{D}$ | _ | 68  | _ | %  |

| Input Return Loss                                          | IRL        | _ | -12 | _ | dB |

| P <sub>out</sub> @ 1 dB Compression Point<br>(f = 940 MHz) | P1dB       | _ | 52  | _ | W  |

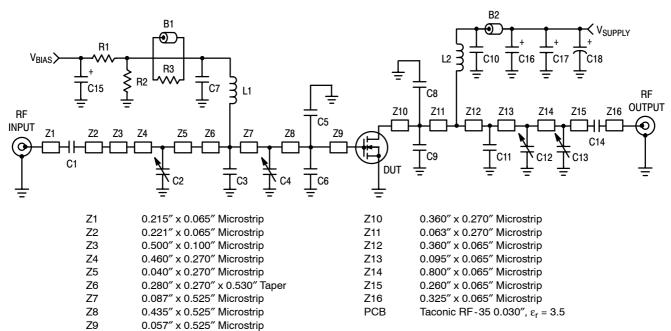

Figure 1. MRF6S9045NR1(NBR1) Test Circuit Schematic

Table 6. MRF6S9045NR1(NBR1) Test Circuit Component Designations and Values

| Part             | Description                              | Part Number        | Manufacturer     |

|------------------|------------------------------------------|--------------------|------------------|

| B1               | Ferrite Bead                             | 2743019447         | Fair Rite        |

| B2               | Ferrite Bead                             | 2743021447         | Fair Rite        |

| C1, C7, C10, C14 | 47 pF Chip Capacitors                    | ATC100B470JT500XT  | ATC              |

| C2, C4, C12      | 0.8-8.0 pF Variable Capacitors, Gigatrim | 27291SL            | Johanson         |

| C3               | 15 pF Chip Capacitor                     | ATC100B150JT500XT  | ATC              |

| C5, C6           | 12 pF Chip Capacitors                    | ATC100B120JT500XT  | ATC              |

| C8, C9           | 13 pF Chip Capacitors                    | ATC100B130JT500XT  | ATC              |

| C11              | 7.5 pF Chip Capacitor                    | ATC100B7R5JT500XT  | ATC              |

| C13              | 0.6-4.5 pF Variable Capacitor, Gigatrim  | 27271SL            | Johanson         |

| C15, C16, C17    | 10 μF, 35 V Tantalum Capacitors          | T491D106K035AT     | Kemet            |

| C18              | 220 μF, 50 V Electrolytic Capacitor      | EMVY500ADA221MJA0G | Nippon Chemi-Con |

| L1, L2           | 12.5 nH Inductor                         | A04T-5             | Coilcraft        |

| R1               | 1 kΩ, 1/4 W Chip Resistor                | CRCW12061001FKEA   | Vishay           |

| R2               | 560 kΩ, 1/4 W Chip Resistor              | CRCW12065600FKEA   | Vishay           |

| R3               | 12 Ω, 1/4 W Chip Resistor                | CRCW120612R0FKEA   | Vishay           |

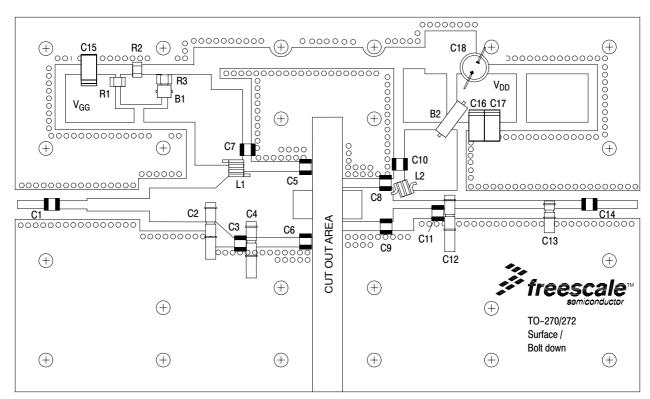

Figure 2. MRF6S9045NR1(NBR1) Test Circuit Component Layout

## TYPICAL CHARACTERISTICS

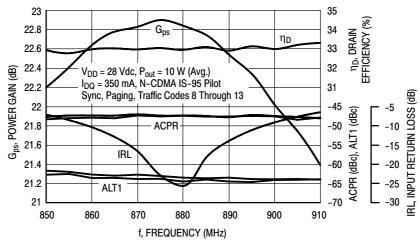

Figure 3. Single-Carrier N-CDMA Broadband Performance @ Pout = 10 Watts Avg.

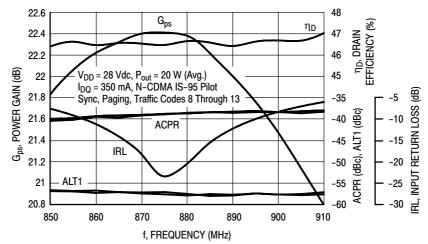

Figure 4. Single-Carrier N-CDMA Broadband Performance @ Pout = 20 Watts Avg.

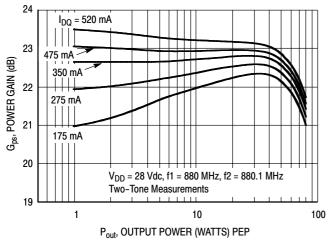

Figure 5. Two-Tone Power Gain versus

Output Power

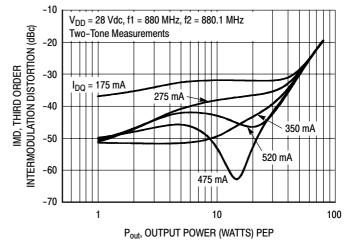

Figure 6. Third Order Intermodulation Distortion versus Output Power

## **TYPICAL CHARACTERISTICS**

$V_{DD} = 28 \text{ Vdc}, P_{out} = 45 \text{ W (PEP)}, I_{DQ} = 350 \text{ mA}$ IMD, INTERMODULATION DISTORTION (dBc) f1 = 880 MHz, f2 = 880.1 MHz, Two-Tone Measurements -10 (f1 + f2)/2 = Center Frequency of 880 MHz -20 -30 3rd Order -40 5th Order -50 7th Order -60 0.1 10 100 0.05 TWO-TONE SPACING (MHz)

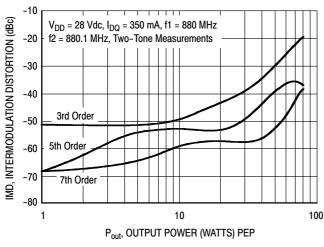

Figure 7. Intermodulation Distortion Products versus Output Power

Figure 8. Intermodulation Distortion Products versus Tone Spacing

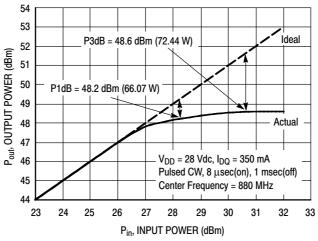

Figure 9. Pulsed CW Output Power versus Input Power

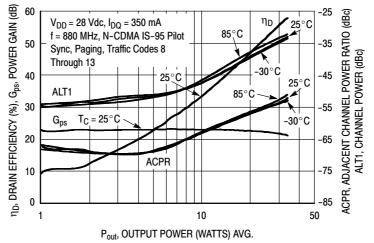

Figure 10. Single-Carrier N-CDMA ACPR, ALT1, Power Gain and Drain Efficiency versus Output Power

## **TYPICAL CHARACTERISTICS**

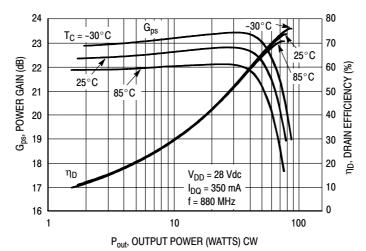

Figure 11. Power Gain and Drain Efficiency versus CW Output Power

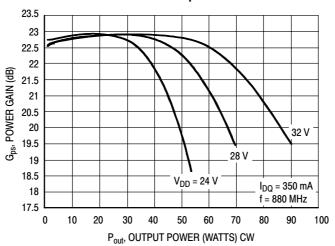

Figure 12. Power Gain versus Output Power

This above graph displays calculated MTTF in hours when the device is operated at V<sub>DD</sub> = 28 Vdc, P<sub>out</sub> = 10 W Avg., and  $\eta_D$  = 32%.

MTTF calculator available at http://www.freescale.com/rf. Select Software & Tools/Development Tools/Calculators to access MTTF calculators by product.

Figure 13. MTTF Factor versus Junction Temperature

## **N-CDMA TEST SIGNAL**

Figure 14. Single-Carrier CCDF N-CDMA

Figure 15. Single-Carrier N-CDMA Spectrum

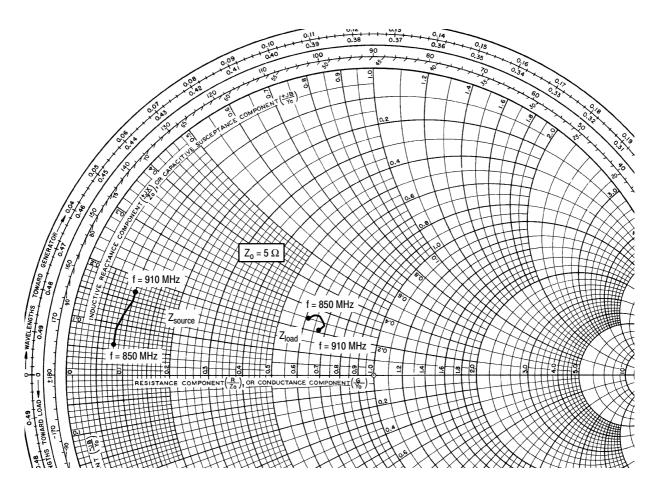

$V_{DD}$  = 28 Vdc,  $I_{DQ}$  = 350 mA,  $P_{out}$  = 10 W Avg.

| f<br>MHz | $\mathbf{Z_{source}}_{\Omega}$ | $\mathbf{Z_{load}}_{\Omega}$ |

|----------|--------------------------------|------------------------------|

| 850      | 0.42 + j0.30                   | 3.05 + j1.27                 |

| 865      | 0.42 + j0.44                   | 3.16 + j1.33                 |

| 880      | 0.45 + j0.60                   | 3.31 + j1.33                 |

| 895      | 0.48 + j0.74                   | 3.43 + j1.20                 |

| 910      | 0.50 + j0.85                   | 3.35 + j1.05                 |

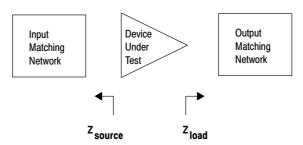

Z<sub>source</sub> = Test circuit impedance as measured from gate to ground.

Z<sub>load</sub> = Test circuit impedance as measured from drain to ground.

Figure 16. Series Equivalent Source and Load Impedance

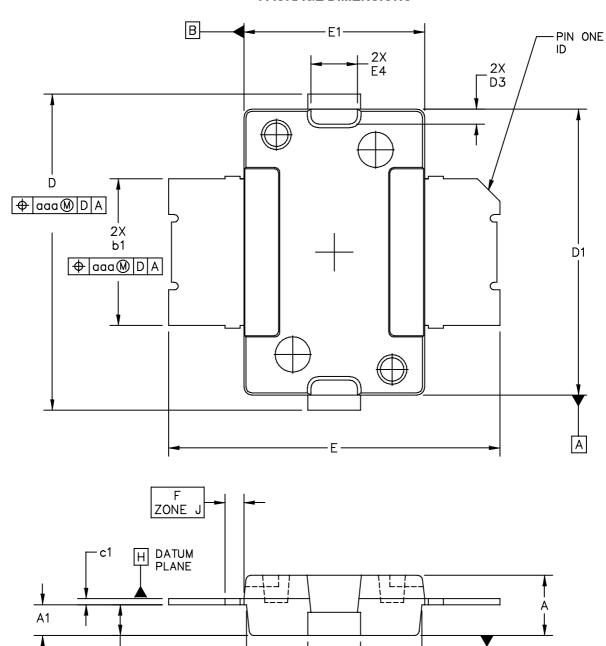

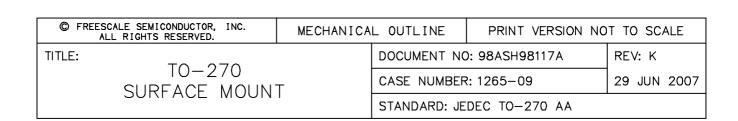

## **PACKAGE DIMENSIONS**

2X E2

E5

D

A2 NOTE 7

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE    | PRINT VERSION NOT TO SCALE |        |  |

|------------------------------------------------------|-----------|--------------|----------------------------|--------|--|

| TITLE:                                               |           | DOCUMENT NO  | ): 98ASH98117A             | REV: K |  |

| TO-270<br>SURFACE MOUN                               | -         | CASE NUMBER  | 29 JUN 2007                |        |  |

| SON ACE MOON                                         | I         | STANDARD: JE | DEC TO-270 AA              |        |  |

## NOTES:

- 1. CONTROLLING DIMENSION: INCH

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. DATUM PLANE -H- IS LOCATED AT TOP OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE TOP OF THE PARTING LINE.

- 4. DIMENSIONS "D1" AND "E1" DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS .006 PER SIDE. DIMENSIONS "D1 AND "E1" DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- 5. DIMENSION "b1" DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE .005 TOTAL IN EXCESS OF THE "b1" DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-.

- 7. DIMENSION "A2" APPLIES WITHIN ZONE "J" ONLY.

- 8. DIMENSIONS "D" AND "E2" DO NOT INCLUDE MOLD PROTRUSION. OVERALL LENGTH INCLUDING MOLD PROTRUSION SHOULD NOT EXCEED 0.430 INCH FOR DIMENSION "D" AND 0.080 INCH FOR DIMENSION "E2". DIMENSIONS "D" AND "E2" DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -D-.

STYLE 1:

PIN 1 - DRAIN

PIN 2 - GATE PIN 3 - SOURCE

|     | FIN 3 - SOURCE |      |        |         |     |      |      |            |      |

|-----|----------------|------|--------|---------|-----|------|------|------------|------|

|     | INCH MI        |      | MILLIN | LIMETER |     | INCH |      | MILLIMETER |      |

| DIM | MIN            | MAX  | MIN    | MAX     | DIM | MIN  | MAX  | MIN        | MAX  |

| Α   | .078           | .082 | 1.98   | 2.08    | F   | .025 | BSC  | 0.64 BSC   |      |

| A1  | .039           | .043 | 0.99   | 1.09    | b1  | .193 | .199 | 4.90       | 5.06 |

| A2  | .040           | .042 | 1.02   | 1.07    | c1  | .007 | .011 | 0.18       | 0.28 |

| D   | .416           | .424 | 10.57  | 10.77   | aaa | .004 |      | 0.10       |      |

| D1  | .378           | .382 | 9.60   | 9.70    |     |      |      |            |      |

| D2  | .290           |      | 7.37   |         |     |      |      |            |      |

| D3  | .016           | .024 | 0.41   | 0.61    |     |      |      |            |      |

| E   | .436           | .444 | 11.07  | 11.28   |     |      |      |            |      |

| E1  | .238           | .242 | 6.04   | 6.15    |     |      |      |            |      |

| E2  | .066           | .074 | 1.68   | 1.88    |     |      |      |            |      |

| E3  | .150           |      | 3.81   |         |     |      |      |            |      |

| E4  | .058           | .066 | 1.47   | 1.68    |     |      |      |            |      |

| E5  | .231           | .235 | 5.87   | 5.97    |     |      |      |            |      |

|     |                |      | ·      |         | -   |      |      | •          |      |

© FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. MECHANICAL OUTLINE PRINT VERSION NOT TO SCALE

TITLE:

TO - 270SURFACE MOUNT DOCUMENT NO: 98ASH98117A REV: K CASE NUMBER: 1265-09 29 JUN 2007 STANDARD: JEDEC TO-270 AA

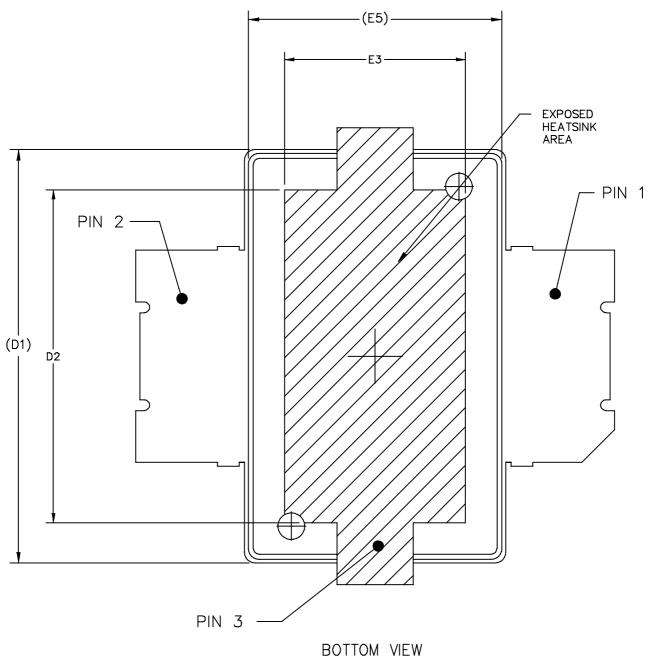

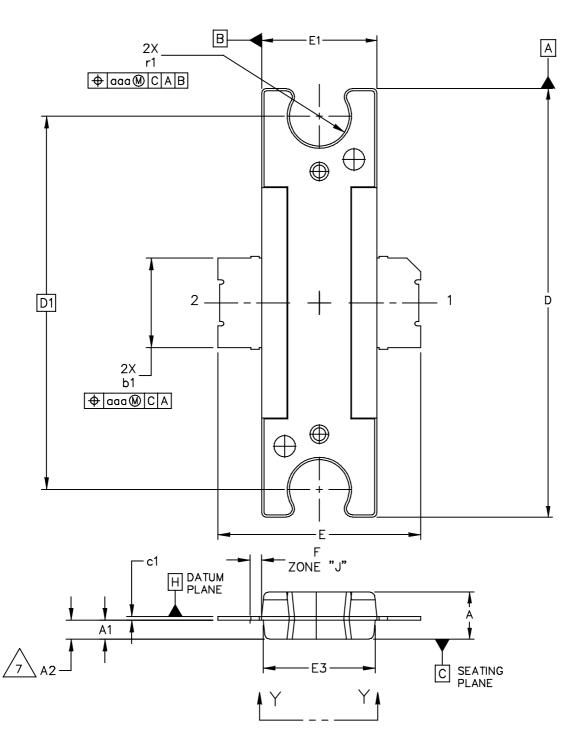

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICA | L OUTLINE                | PRINT VERSION NO | T TO SCALE  |

|------------------------------------------------------|-----------|--------------------------|------------------|-------------|

| TITLE:                                               |           | DOCUMENT NO: 98ASA99191D |                  | REV: E      |

| TO-272<br>2 LEAD                                     |           | CASE NUMBER: 1337-04     |                  | 10 SEP 2007 |

| Z LLAD                                               |           | STANDARD: JE             | DEC TO-272 BC    |             |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. |        | MECHANICAL OUTLINE |                      | PRINT VERSION NOT TO SCALE |             |  |

|------------------------------------------------------|--------|--------------------|----------------------|----------------------------|-------------|--|

| TITLE:                                               | TO 070 |                    | DOCUMENT NO          | ): 98ASA99191D             | REV: E      |  |

| TO-272<br>2 LEAD                                     |        |                    | CASE NUMBER: 1337-04 |                            | 10 SEP 2007 |  |

|                                                      | Z LLAD |                    | STANDARD: JE         | DEC TO-272 BC              |             |  |

## NOTES:

- 1. CONTROLLING DIMENSION: INCH

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.

- 3. DATUM PLANE -H- IS LOCATED AT THE TOP OF LEAD AND IS COINCIDENT WITH THE LEAD WHERE THE LEAD EXITS THE PLASTIC BODY AT THE TOP OF THE PARTING LINE.

- 4. DIMENSIONS "D" AND "E1" DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS .006 PER SIDE. DIMENSIONS "D" AND "E1" DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE -H-.

- 5. DIMENSIONS "b1" DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE .005 TOTAL IN EXCESS OF THE "b1" DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 6. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-.

- 7. DIMENSION A2 APPLIES WITHIN ZONE "J" ONLY.

- 8. HATCHING REPRESENTS THE EXPOSED AREA OF THE HEAT SLUG.

STYLE 1:

PIN 1 - DRAIN

PIN 2 - GATE

PIN 3 - SOURCE

|     | INCH |      |       |       |     | IN   | CH   | MILLIN | /ETER |

|-----|------|------|-------|-------|-----|------|------|--------|-------|

| DIM | MIN  | MAX  | MIN   | MAX   | DIM | MIN  | MAX  | MIN    | MAX   |

| Α   | .100 | .104 | 2.54  | 2.64  | b1  | .193 | .199 | 4.90   | 5.05  |

| A1  | .039 | .043 | 0.99  | 1.09  | c1  | .007 | .011 | 0.18   | 0.28  |

| A2  | .040 | .042 | 1.02  | 1.07  | r1  | .063 | .068 | 1.60   | 1.73  |

| D   | .928 | .932 | 23.57 | 23.67 | aaa | .0   | 04   | 0.1    |       |

| D1  | .810 | BSC  | 20.57 | BSC   |     |      |      |        |       |

| D2  | .604 |      | 15.34 |       |     |      |      |        |       |

| E   | .438 | .442 | 11.12 | 11.23 |     |      |      |        |       |

| E1  | .248 | .252 | 6.30  | 6.40  |     |      |      |        |       |

| E2  | .162 |      | 4.11  |       |     |      |      |        |       |

| E3  | .241 | .245 | 6.12  | 6.22  |     |      |      |        |       |

| F   | .025 | BSC  | 0.64  | BSC   |     |      |      |        |       |

|     |      |      |       |       |     |      |      |        |       |

|     |      |      |       |       |     |      |      |        |       |

© FREESCALE SEMICONDUCTOR, INC.

MECHANICAL OUTLINE

DOCUMENT NO 98ASA99191D

TO-272

2 LEAD

DOCUMENT NO 98ASA99191D

CASE NUMBER: 1337-04

STANDARD: JEDEC TO-272 BS

## PRODUCT DOCUMENTATION

Refer to the following documents to aid your design process.

## **Application Notes**

- AN1907: Solder Reflow Attach Method for High Power RF Devices in Plastic Packages

- AN1955: Thermal Measurement Methodology of RF Power Amplifiers

- AN3263: Bolt Down Mounting Method for High Power RF Transistors and RFICs in Over-Molded Plastic Packages

## **Engineering Bulletins**

• EB212: Using Data Sheet Impedances for RF LDMOS Devices

## **REVISION HISTORY**

The following table summarizes revisions to this document.

| Revision | Date      | Description                                                                                                                                                                                                                                                                                                               |

|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4        | Aug. 2008 | Listed replacement part and Device Migration notification reference number, p. 1                                                                                                                                                                                                                                          |

|          |           | Listed MRF6S9045NBR1 as no longer manufactured, p. 1                                                                                                                                                                                                                                                                      |

|          |           | Replaced Case Outline 1265-08 with 1265-09, Issue K, p. 1, 11-13. Corrected cross hatch pattern in bottom view and changed its dimensions (D2 and E3) to minimum value on source contact (D2 changed from Min-Max .290320 to .290 Min; E3 changed from Min-Max .150180 to .150 Min). Added JEDEC Standard Package Number. |

|          |           | Replaced Case Outline 1337-03 with 1337-04, p. 1, 14-16. Issue D: Removed Drain-ID label from View Y-Y on Sheet 2. Renamed E2 to E3. Added cross-hatch region dimensions D2 and E2. Added JEDEC Standard Package Number. Issue E: Corrected document number 98ASA99191D on Sheet 3.                                       |

|          |           | Removed Total Device Dissipation from Max Ratings table as data was redundant (information already provided in Thermal Characteristics table), p. 1                                                                                                                                                                       |

|          |           | Added Case Operating Temperature limit to the Maximum Ratings table and set limit to 150°C, p. 1                                                                                                                                                                                                                          |

|          |           | Operating Junction Temperature increased from 200°C to 225°C in Maximum Ratings table, related<br>"Continuous use at maximum temperature will affect MTTF" footnote added and changed 200°C to 225°C in Capable Plastic Package bullet, p. 1                                                                              |

|          |           | <ul> <li>Corrected V<sub>DS</sub> to V<sub>DD</sub> in the RF test condition voltage callout for V<sub>GS(Q)</sub> and added "Measured in<br/>Functional Test", On Characteristics table, p. 2</li> </ul>                                                                                                                 |

|          |           | Removed Forward Transconductance from On Characteristics table as it no longer provided usable information, p. 2                                                                                                                                                                                                          |

|          |           | Corrected C <sub>iss</sub> test condition to indicate AC stimulus on the V <sub>GS</sub> connection versus the V <sub>DS</sub> connection,<br>Dynamic Characteristics table, p. 2                                                                                                                                         |

|          |           | Updated Part Numbers in Table 6 Component Designations and Values, to latest RoHS compliant part numbers, p. 4                                                                                                                                                                                                            |

|          |           | Adjusted scale for Fig. 5, Two-Tone Power Gain versus Output Power, to better match the device's capabilities, p. 6                                                                                                                                                                                                       |

|          |           | Removed lower voltage tests from Fig. 12, Power Gain versus Output Power, due to fixed tuned fixture limitations, p. 8                                                                                                                                                                                                    |

|          |           | Replaced Fig. 13, MTTF versus Junction Temperature with updated graph. Removed Amps <sup>2</sup> and listed operating characteristics and location of MTTF calculator for device, p. 8                                                                                                                                    |

|          |           | Added Product Documentation and Revision History, p. 17                                                                                                                                                                                                                                                                   |

## How to Reach Us:

#### Home Page:

www.freescale.com

## Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan

RCHIVE INFORMATION

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or +1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005-2006, 2008. All rights reserved.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Document Number: MRF6S9045N

Rev. 4, 8/2008