LM10503

www.ti.com

# LM10503 Triple Buck Converter Energy Management Unit (EMU) with PowerWise<sup>™</sup> 2.0 Adaptive Voltage Scaling (AVS) and ADC

Check for Samples: LM10503

### **FEATURES**

- **Three High-Efficiency Programmable Bucks:**

- Integrated FETs with Low R<sub>DSON</sub>

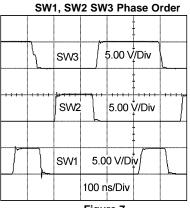

- Bucks Operate at 120° Phase to Reduce the Input Current Ripple and Capacitor Size

- Input Under Voltage Lock-out

- Enable Pin and Internal Soft Start

- Current Overload and Thermal Shutdown

- 4-Channel Multi-Function Port (MFP) that Includes:

- 8-Bit ADC with Integrated Reference

- Comparator Input/General Purpose Output

- Interrupt Request Output with Multiple Sources

- PWI<sup>™</sup> 2.0 Open-Standard Interface

- Power-On Reset (POR) Open-Drain Output with Delay

- LM10503-1 with Start-up Sequence Option

### APPLICATIONS

The LM10503 and LM10503-1 are Suitable for Applications that Require Multiple Supplies in the Range of 0.7 to 3.5V and up to 2A:

- Point of Load Regulation for ASICs •

- NVM Memory Drives (HDD or FLASH)

- Servers and Networking Cards

- PCI Cards, Set-Top-Box Processors

- Video Processors and Graphic Cards

- **High-Performance Medical and Industrial** Processors

### DESCRIPTION

LM10503 is an advanced EMU containing three configurable, high-efficiency bucks for supplying variable voltages to a diverse range of applications. The device is ideal for supporting ASIC and SOC designs which use voltage scaling for reducing power consumption.

The device is digitally controlled via the PWI 2.0 interface. LM10503 open-standard operates cooperatively with a PowerWise technologycompatible ASIC to optimize the supply voltage adaptively (AVS - Adaptive Voltage Scaling) over process and temperature variations. It also supports dynamic voltage-scaling (DVS) using frequency/voltage pairs from pre-characterized lookup tables.

### **KEY SPECIFICATIONS**

- Single input rail with wide range: 3.0V 5.5V

- Buck 1 (AVS): Programmable output: 0.7V -• 1.2V, 2A

- Bucks 2 & 3: Adjustable output: 1.0V 3.5V, 1A

- ±2% Feedback voltage accuracy ٠

- Up to 96% peak efficiency buck regulators ٠

- 2MHz switching frequency for smaller inductor size

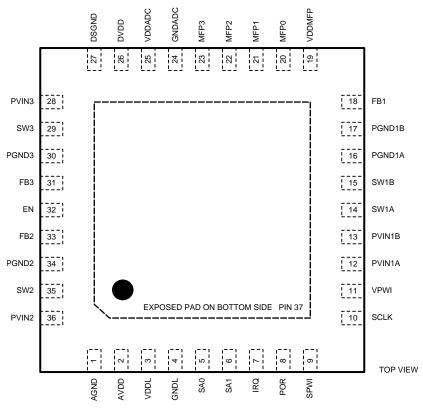

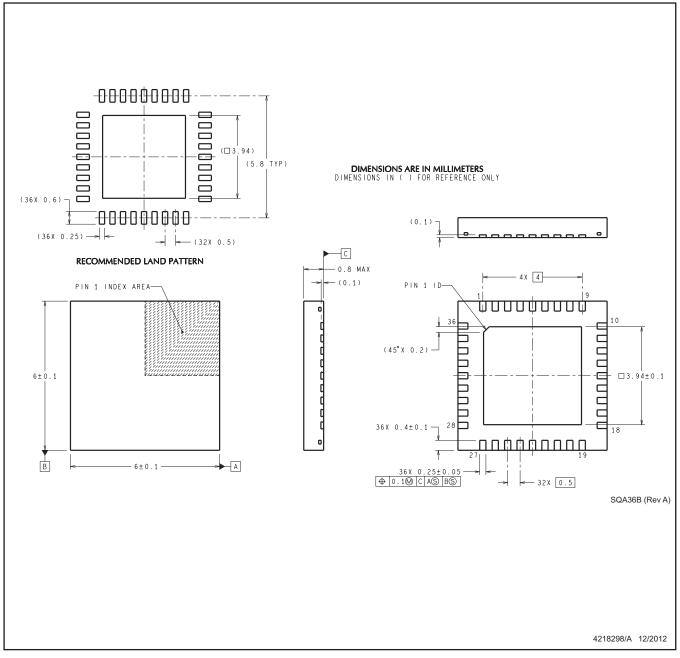

- WQFN-36 package (36 pins, 6mm x 6mm x 0.8mm, 0.5mm pitch)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

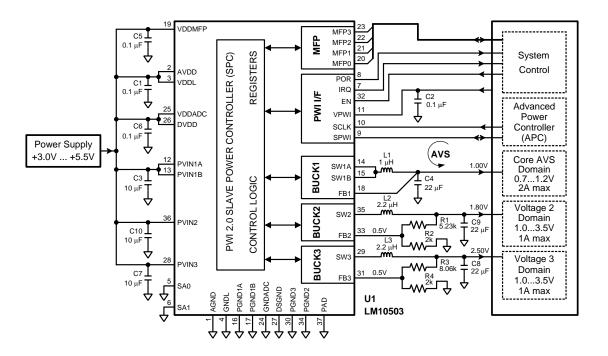

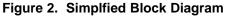

# **Typical Application Circuit**

#### Overview

The device contains three buck converters. The table below lists the output characteristics of the three converters.

#### Table 1. SUPPLY SPECIFICATIONS

| Supply | Output Voltage<br>Range (V) | Output Voltage Programming<br>Resolution (mV) | Maximum Output<br>Current (A) | Typical Application         |

|--------|-----------------------------|-----------------------------------------------|-------------------------------|-----------------------------|

| VSW1   | 0.700 to 1.208              | 4                                             | 2                             | Core Voltage Scaling Domain |

| VSW2,3 | 1.000 to 3.500              | N/A                                           | 1                             | I/O, aux voltage            |

SNVS644A - DECEMBER 2011 - REVISED MARCH 2013

### **Connection Diagrams and Package Mark Information**

|       | PIN DESCRIPTIONS |     |                     |                                                                                  |              |  |

|-------|------------------|-----|---------------------|----------------------------------------------------------------------------------|--------------|--|

| Pin # | Pin Name         | I/O | Type <sup>(1)</sup> | Functional Description                                                           |              |  |

| 1     | AGND             | G   | G                   | Analog ground for Bucks 1, 2 and 3                                               |              |  |

| 2     | AVDD             | Р   | Р                   | Analog power for Bucks 1, 2 and 3                                                |              |  |

| 3     | VDDL             | Р   | Р                   | Power for logic block                                                            |              |  |

| 4     | GNDL             | G   | G                   | Ground for logic block                                                           |              |  |

| 5     | SA0              | I   | D                   | PWI Slave Address Bit 0. Tie to ground or VPWI for '0' or '1, re                 | espectively. |  |

| 6     | SA1              | I   | D                   | PWI Slave Address Bit 1. Tie to ground or VPWI for '0' or '1, respectively.      |              |  |

| 7     | IRQ              | 0   | OD                  | Interrupt request. This open drain output is asserted low on an interrupt event. |              |  |

| 8     | POR              | 0   | OD                  | Power On Reset. This open drain output is asserted low on reset.                 |              |  |

| 9     | SPWI             | I/O | D                   | PowerWise Interface (PWI) bi-directional data                                    |              |  |

| 10    | SCLK             | I   | D                   | PowerWise Interface (PWI) clock input                                            |              |  |

| 11    | VPWI             | Р   | Р                   | Power supply voltage input for PWI and logic interfaces                          |              |  |

| 12    | PVIN1A           | Р   | Р                   | Power supply voltage input for power stage PFET                                  |              |  |

| 13    | PVIN1B           | Р   | Р                   | Power supply voltage input for power stage PFET                                  |              |  |

| 14    | SW1A             | 0   | 0                   | Switching node, connect to inductor                                              |              |  |

| 15    | SW1B             | 0   | 0                   | Switching node, connect to inductor                                              | Buck #1      |  |

| 16    | PGND1A           | G   | G                   | Power ground, connect to system ground.                                          |              |  |

| 17    | PGND1B           | G   | G                   | Power ground, connect to system ground.                                          |              |  |

| 18    | VFB1             | I   | А                   | Feedback input                                                                   |              |  |

(1) A: Analog Pin, D: Digital Pin, G: Ground Pin, P: Power Pin, I: Input Pin, I/O: Input/Output Pin, O: Output Pin, OD: Open Drain Output Pin

#### 3

www.ti.com

INSTRUMENTS

Texas

|       | PIN DESCRIPTIONS (continued) |     |                     |                                                                 |          |  |

|-------|------------------------------|-----|---------------------|-----------------------------------------------------------------|----------|--|

| Pin # | Pin Name                     | I/O | Type <sup>(1)</sup> | Functional Description                                          |          |  |

| 19    | VDDMFP                       | Р   | Р                   | Power supply voltage input for the multifunction pins, GPO mo   | de.      |  |

| 20    | MFP0                         | I/O | A/D                 | Multifunction pin, ADC input, comparator input, GPO, channel    | 0        |  |

| 21    | MFP1                         | I/O | A/D                 | Multifunction pin, ADC input, comparator input, GPO, channel 1  |          |  |

| 22    | MFP2                         | I/O | A/D                 | Multifunction pin, ADC input, comparator input, GPO, channel    | 2        |  |

| 23    | MFP3                         | I/O | A/D                 | Multifunction pin, ADC input, comparator input, GPO, channel 3  |          |  |

| 24    | GNDADC                       | G   | G                   | Ground for ADC. Connect to system Ground.                       |          |  |

| 25    | VDDADC                       | Р   | Р                   | Power for ADC                                                   |          |  |

| 26    | DVDD                         | Р   | Р                   | Power for digital block of Bucks 1, 2 and 3                     |          |  |

| 27    | DSGND                        | G   | G                   | Ground for digital block of Bucks 1, 2 and 3                    |          |  |

| 28    | PVIN3                        | Р   | Р                   | Power supply voltage input for power stage PFET                 |          |  |

| 29    | SW3                          | 0   | 0                   | Switching node, connect to inductor.                            | Duals #2 |  |

| 30    | PGND3                        | G   | G                   | Power ground, connect to system ground.                         | Buck #3  |  |

| 31    | VFB3                         | I   | А                   | Feedback input                                                  |          |  |

| 32    | EN                           | I   | D                   | Enable input. Set this digital input high for normal operation. |          |  |

| 33    | VFB2                         | I   | А                   | Feedback input                                                  |          |  |

| 34    | PGND2                        | G   | G                   | Power ground, connect to system ground.                         | Duals #0 |  |

| 35    | SW2                          | 0   | 0                   | Switching node, connect to inductor.                            | Buck #2  |  |

| 36    | PVIN2                        | Р   | Р                   | Power supply voltage input for power stage PFET                 |          |  |

| 37    | PAD                          | G   | G                   | Exposed pad, connect to system ground                           |          |  |

www.ti.com

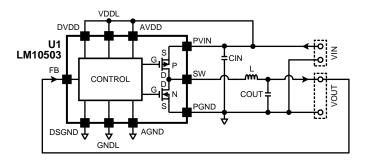

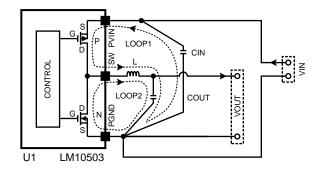

Figure 3. Typical Application Circuit (Detailed)

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### Absolute Maximum Ratings (1) (2) (3) (4) (5)(6)

| Any supply pin (VIN) to GND <sup>(3)</sup> | -0.3 to +6.5V                         |

|--------------------------------------------|---------------------------------------|

| Any signal pin, VPWI, VDDMFP               | -0.3 to +(VIN+0.3V) but not over 6.5V |

| Between any GND pins <sup>(4)</sup>        | -0.3 to +0.3V                         |

| Junction Temperature (T <sub>J-MAX</sub> ) | +150°C                                |

| Storage Temperature Range                  | -65°C to +150°C                       |

| Maximum Lead Temperature (Soldering 4 sec) | +260°C                                |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are with respect to the potential at the GND pin.

- (3) VIN refers to these power pins connected together: AVDD = VDDL = VDDADC = DVDD = PVIN1A = PVIN1B = PVIN2 = PVIN3

- (4) GND Pins means all ground pins must be connected together: AGND = GNDL = PGND1A = PGND1B = GNDADC = DSGND = PGND3 = PGND2 = PAD.

- (5) Signal pins include SW1-3, SA0-1, IRQ, POR, SPWI, SCLK, FB1-3, MFP0-3 and EN.

- (6) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

# LM10503

#### SNVS644A – DECEMBER 2011 – REVISED MARCH 2013

**ISTRUMENTS**

#### ESD Ratings (1)

| LOD Ratings      |       |

|------------------|-------|

| Human Body Model | 2000V |

| Machine Model    | 200V  |

|                  |       |

Applies to all pins. The Human Body Model (HBM) is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin (MIL-STD-883 3015.7). The Machine Model (MM) is a 200 pF capacitor discharged directly into each pin (EAIJ).

### Recommended Operating Ratings <sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup> <sup>(4)</sup>

| VIN                                                                                                                    | 3.0V to 5.5V                    |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| VPWI <sup>(5)</sup>                                                                                                    | 1.62V to 3.63V but not over VIN |

| VDDMFP <sup>(5)</sup>                                                                                                  | 1.62V to VIN                    |

| VFB1,2,3                                                                                                               | 0 to VOUT1,2,3                  |

| EN                                                                                                                     | 0 to VIN                        |

| MFP0-3                                                                                                                 | 0 to VDDMFP                     |

| SPWI, SCLK, SA0-1, POR, IRQ                                                                                            | 0 to VPWI                       |

| Junction Temperature (T <sub>J</sub> ) Range                                                                           | -40°C to +105°C                 |

| Ambient Temperature (T <sub>A</sub> ) Range <sup>(6)</sup> <sup>(7)</sup> <sup>(8)</sup> <sup>(9)</sup>                | -40°C to +70°C                  |

| Maximum Continuous Power Dissipation (P <sub>D-MAX</sub> ) <sup>(6)</sup> <sup>(7)</sup> <sup>(8)</sup> <sup>(9)</sup> | 1.33W                           |

(1) All voltages are with respect to the potential at the GND pin.

(2) VIN refers to these power pins connected together: AVDD = VDDL = VDDADC = DVDD = PVIN1A = PVIN1B = PVIN2 = PVIN3

(3) GND Pins means all ground pins must be connected together: AGND = GNDL = PGND1A = PGND1B = GNDADC = DSGND = PGND3 = PGND2 = PAD.

(4) Signal pins include SW1-3, SA0-1, IRQ, POR, SPWI, SCLK, FB1-3, MFP0-3 and EN.

(5) VPWI, VDDMFP sequencing requirements: voltage on VPWI and VDDMFP must be less than, or equal to, VIN, including during ramp up and ramp down of power supplies.

(6) For detailed soldering specifications and information, please refer to Application Note 1187 Leadless Leadframe Package (LLP) SNOA401

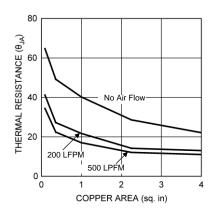

- (7) The amount of Absolute Maximum power dissipation allowed for the device depends on the ambient temperature and can be calculated using the formula:  $P = (T_J T_A)/\theta_{JA}$ , (1) where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.  $\theta_{JA}$  is highly application and board-layout dependent. Internal thermal shutdown circuitry protects the device from permanent damage. (See General Electrical Characteristics.)

- (8) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 105°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>) and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

- (9) θ<sub>JC</sub> refers to the bottom metal surface of the LLP as the CASE. θ<sub>JB</sub> is the junction-to-board thermal resistance. Junction-to-ambient thermal resistance (θ<sub>JA</sub>) is taken from a thermal modeling result and is based on a power dissipation of 1.33W, using a 4-layer FR-4 standard JEDEC thermal test board (4LJEDEC): 4"x3" (102 mm x 76 mm x 1.6 mm) in size. Ambient temperature in simulation is 22°C, under stationary airflow condition. The board has 2 internal copper layers which cover roughly the same size as the board. The copper thickness for the four layers, starting from the top one are: 36/18/18/36 [µm] (2/1/1/2 [oz]). A minimum number of 9 thermal vias are placed between the pad on the top side and the 2nd copper layer. Detailed description of the board can be found in JEDEC standard JESD 51-7 (High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages) and JESD51-5 (Extension of Thermal Test Board Standards for Packages with Direct Thermal Attachment Mechanisms). The junction-to-ambient thermal resistance (θ<sub>JA</sub>) is highly dependent on application and board layout. The value of θ<sub>JA</sub> of this product can vary significantly, depending on PCB material, layout, and environmental conditions. In applications where high maximum power dissipation exists (high V<sub>IN</sub>, high I<sub>OUT</sub>), special care must be paid to thermal dissipation issues. For more information on these topics, please refer to Application Note 1187: Leadless Leadframe Package (LLP) SNOA401 and the Power Efficiency and Power Dissipation section of this datasheet.

### Thermal Properties <sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup> <sup>(4)</sup>

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )   | 2.2°C/W  |

|----------------------------------------------------------|----------|

| Junction-to-Board Thermal Resistance $(\theta_{JA})$     | 12.4°C/W |

| Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) | 27.0°C/W |

(1) For detailed soldering specifications and information, please refer to Application Note 1187 Leadless Leadframe Package (LLP) SNOA401

- (2) The amount of Absolute Maximum power dissipation allowed for the device depends on the ambient temperature and can be calculated using the formula:  $P = (T_J T_A)/\theta_{JA}$ , (1) where  $T_J$  is the junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.  $\theta_{JA}$  is highly application and board-layout dependent. Internal thermal shutdown circuitry protects the device from permanent damage. (See General Electrical Characteristics.)

- (3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 105°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>) and the junction-to ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

- part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

(4) θ<sub>JC</sub> refers to the bottom metal surface of the LLP as the CASE. θ<sub>JB</sub> is the junction-to-board thermal resistance. Junction-to-ambient thermal resistance (θ<sub>JA</sub>) is taken from a thermal modeling result and is based on a power dissipation of 1.33W, using a 4-layer FR-4 standard JEDEC thermal test board (4LJEDEC): 4"x3" (102 mm x 76 mm x 1.6 mm) in size. Ambient temperature in simulation is 22°C, under stationary airflow condition. The board has 2 internal copper layers which cover roughly the same size as the board. The copper thickness for the four layers, starting from the top one are: 36/18/18/36 [µm] (2/1/1/2 [oz]). A minimum number of 9 thermal vias are placed between the pad on the top side and the 2nd copper layer. Detailed description of the board can be found in JEDEC standard JESD 51-7 (High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages) and JESD51-5 (Extension of Thermal Test Board Standards for Packages with Direct Thermal Attachment Mechanisms). The junction-to-ambient thermal resistance (θ<sub>JA</sub>) is highly dependent on application and board layout. The value of θ<sub>JA</sub> of this product can vary significantly, depending on PCB material, layout, and environmental conditions. In applications where high maximum power dissipation exists (high V<sub>IN</sub>, high I<sub>OUT</sub>), special care must be paid to thermal dissipation issues. For more information on these topics, please refer to Application Note 1187: Leadless Leadframe Package (LLP) SNOA401 and the Power Efficiency and Power Dissipation section of this datasheet.

### General Electrical Characteristics (1) (2)

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range -40°C ≤  $T_J$ ≤ +105°C.

| Symbol                     | Parameter                                                                                          | Conditions                                                                             | Min  | TYP  | Max  | Units |

|----------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|-------|

| I <sub>Q-VIN-SD</sub>      | Quiescent supply current of<br>all VIN supply pins combined;<br>part is shut down                  | Device is shut down by:<br>a) driving EN pin low or<br>b) issuing the Shutdown Command |      | 2    | 20   | μΑ    |

| I <sub>Q-VIN-NO-LOAD</sub> | Quiescent supply current of<br>all VIN supply pins combined;<br>part is enabled, but not<br>loaded | Switching in forced PWM, ADC disabled,<br>MFP pins set as inputs, driven LOW           |      | 16   | 25   | mA    |

| I <sub>Q-VPWI-SD</sub>     | Quiescent supply current of<br>VPWI supply pin; part is shut<br>down                               | Device is shut down by:<br>a) driving EN pin low or<br>b) issuing the Shutdown Command |      | 0.1  | 1    |       |

| I <sub>Q-VPWI-IDLE</sub>   | Quiescent supply current of<br>VPWI supply pin; part is<br>enabled, PWI bus is idle                | Device is enabled, PWI bus is idle (no<br>load on SPWI, SCLK)                          |      | 0.1  | 1    | μA    |

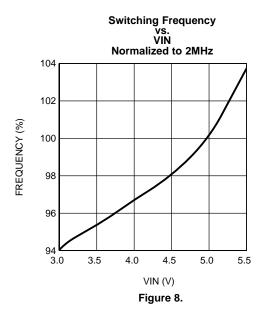

| F <sub>SW</sub>            | Switching Frequency of all 3 bucks                                                                 | PWM-mode measured at SW1, 2, 3 pins, 120° out of phase (by design)                     | 1.75 | 2.00 | 2.30 | MHz   |

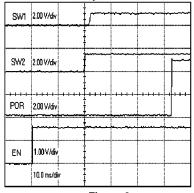

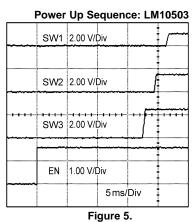

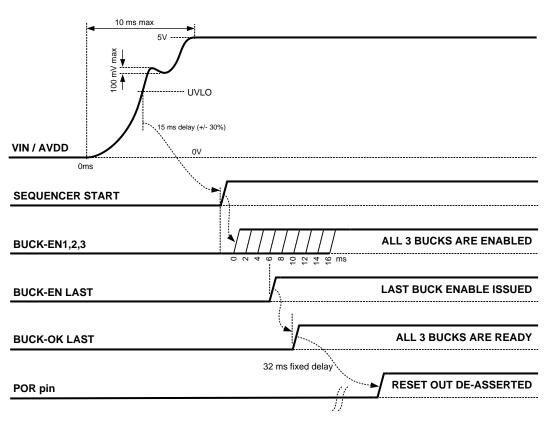

| T <sub>POR-DELAY</sub>     | Delay from EN-pin rising edge to POR-pin rising edge                                               | All 3 bucks are unloaded                                                               |      | 53   |      | ms    |

| EN, FB PINS                |                                                                                                    |                                                                                        |      |      |      |       |

| T <sub>EN_LOW</sub>        | EN pin minimum low pulse                                                                           | To trigger a startup sequence                                                          | 100  |      |      | nS    |

| V <sub>IL-EN</sub>         | EN pin logic low input                                                                             |                                                                                        |      |      | 0.2  | v     |

| V <sub>IH-EN</sub>         | EN pin logic high input                                                                            | VIN = 5V                                                                               | 2.0  |      |      | v     |

| I <sub>IH-EN</sub>         | EN pin input current, driven high                                                                  | V_EN = VIN                                                                             |      | +0.1 | +1   |       |

| I <sub>IL-EN</sub>         | EN pin input current, driven low                                                                   | V_EN = 0.0V                                                                            | -1   | -0.1 |      | μA    |

(1) All voltages are with respect to the potential at the GND pin.

(2) VIN refers to these power pins connected together: AVDD = VDDL = VDDADC = DVDD = PVIN1A = PVIN1B = PVIN2 = PVIN3

www.ti.com

TRUMENTS

### General Electrical Characteristics <sup>(1) (2)</sup> (continued)

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range  $-40^{\circ}C \le T_J \le +105^{\circ}C$ .

| Symbol                          | Parameter                                                                                 | Conditions                                                              | Min                                                          | TYP    | Max      | Units |

|---------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|--------|----------|-------|

| V <sub>IL_UVLO-AVDD</sub>       | UVLO falling threshold                                                                    |                                                                         | 2.4                                                          | 2.6    |          |       |

| VIH_UVLO-AVDD                   | UVLO rising threshold                                                                     | Measured on AVDD pin ramping,<br>monitored at POR pin.                  |                                                              | 2.8    | 2.9      | V     |

| V <sub>HYST_UVLO-AVDD</sub>     | UVLO hysteresis window                                                                    |                                                                         |                                                              | 0.24   |          |       |

| V <sub>POR-L</sub>              | POR pin is asserted when<br>target voltage of Buck1 or 2<br>or 3 is lower than this level | Percentage values with respect to target                                |                                                              | 85     |          | - %   |

| V <sub>POR-H</sub>              | POR pin is de-asserted when target voltage of Buck1 and 2 and 3 is higher than this level | values of V <sub>FB1,2,3</sub> monitored at the respective buck outputs |                                                              | 94     |          | 70    |

|                                 | 1-0, IRQ, POR PINS<br>powered from VPWI.)                                                 |                                                                         |                                                              |        |          |       |

| V <sub>IL</sub>                 | Logic Input Low                                                                           | SPWI, SCLK, SA1-0 pins                                                  |                                                              |        | 30%      | VPWI  |

| V <sub>IH</sub>                 | Logic Input High                                                                          | SPWI, SCLK, SAT-0 pins                                                  | 70%                                                          |        |          |       |

| IIL                             | Input Current, pin driven low                                                             | SPWI, SCLK, SA1-0 pins                                                  | -2                                                           |        |          | μA    |

| I <sub>IH</sub>                 | Input current, pin driven high                                                            | SA1-0 pins                                                              |                                                              |        | +2<br>+5 | ۵     |

|                                 | (VPWI)                                                                                    | SPWI & SCLK have internal pulldown                                      |                                                              |        |          | μA    |

| M                               | Logic Output Low                                                                          |                                                                         |                                                              |        | 0.2      | VPWI  |

| V <sub>OL</sub>                 | Logic Oulput Low                                                                          | SPWI, IRQ, POR for $I_{SINK} \le 2mA$                                   |                                                              |        | 20%      |       |

| V <sub>OH</sub>                 | Logic Output High                                                                         | SPWI for I <sub>SOURCE</sub> ≤ 2mA                                      | 80%                                                          |        |          |       |

| I <sub>OZ</sub>                 | Output Leakage Current                                                                    | IRQ, POR pins when open drain                                           | -2                                                           |        | +2       | μA    |

| MFP0-3 PINS<br>(Pins used in Ge | neral Purpose Outputs (GPO)                                                               | or comparator inputs; these pins are po                                 | wered from V                                                 | DDMFP) |          |       |

| IIL                             | Input current, pin driven low                                                             |                                                                         | -2                                                           |        |          |       |

| I <sub>IH</sub>                 | Input current, pin driven high (VDDMFP)                                                   | Open drain or comparator input mode                                     |                                                              |        | +2       | μA    |

| V <sub>OL</sub>                 | Logic Output Low                                                                          | Pin in GPO mode, I <sub>SINK</sub> ≤ 1mA                                |                                                              |        | 0.2      |       |

| V <sub>OH</sub>                 | Logic Output High                                                                         | Pin in GPO mode, $I_{SOURCE} \le 1$ mA                                  | in GPO mode, I <sub>SOURCE</sub> ≤ 1mA <b>VDDMFP-</b><br>0.2 |        |          | V     |

| THERMAL SHUT                    | DOWN                                                                                      | ·                                                                       | ·                                                            |        |          | •     |

| T <sub>SD</sub>                 | Thermal Shutdown<br>Temperature                                                           |                                                                         |                                                              | 160    |          | - °C  |

| T <sub>SD-HYST</sub>            | Thermal Shutdown<br>Hysteresis                                                            |                                                                         |                                                              | 20     |          |       |

### Buck 1 Electrical Characteristics <sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup>

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range -40°C  $\leq T_I \leq$  +105°C.

| Symbol                 | Parameter                                                         | Conditions                                                                        | Min  | Тур  | Max  | Unit |

|------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| I <sub>Q-NO-LOAD</sub> | Quiescent supply current of<br>PVIN1A and PVIN1B pins<br>combined | Buck 1 is enabled, but not loaded,<br>V <sub>OUT1</sub> = 1.05V, switching in PWM |      | 1    | 3    | mA   |

| I <sub>OUT-MAX</sub>   | Continuous maximum load current                                   | Buck 1 is enabled, V <sub>OUT1</sub> = 1.05V, switching in PWM*                   | 2    |      |      | ٨    |

| I <sub>PEAK</sub>      | Peak switching current limit                                      | Buck 1 is enabled, V <sub>OUT1</sub> = 1.05V, switching in PWM                    | 2.33 | 2.75 | 3.90 | A    |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are with respect to the potential at the GND pin.

(3) VIN refers to these power pins connected together: AVDD = VDDL = VDDADC = DVDD = PVIN1A = PVIN1B = PVIN2 = PVIN3

8 Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

www.ti.com

### Buck 1 Electrical Characteristics <sup>(1) (2) (3)</sup> (continued)

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range  $-40^{\circ}C \le T_J \le +105^{\circ}C$ .

| Symbol                      | Parameter                                                 | Conditions                                                                                                                                                  | Min | Тур   | Max  | Unit |

|-----------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|------|

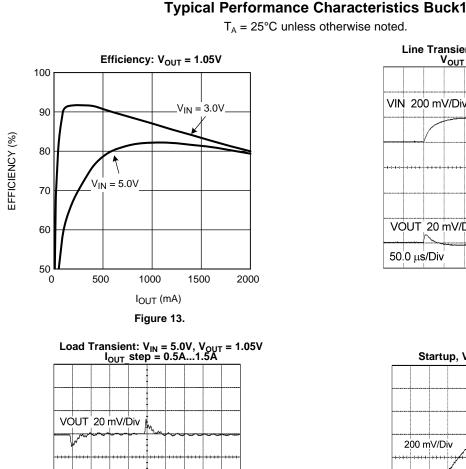

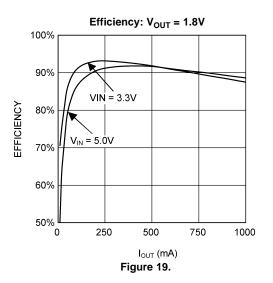

| η <sub>SW1-3V</sub>         | <b>F</b> (0)                                              | V <sub>IN</sub> = 3.3V, V <sub>OUT</sub> = 1.05V, I <sub>OUT</sub> = 0.2A                                                                                   |     | 92%   |      |      |

| η <sub>SW1-5V</sub>         | Efficiency peak                                           | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 1.05V, I <sub>OUT</sub> = 1A                                                                                       |     | 82%   |      | %    |

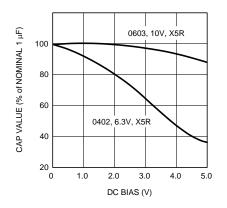

| C <sub>IN</sub>             | Input Capacitor                                           |                                                                                                                                                             | 7   | 10    |      |      |

|                             | Output Filter Capacitor                                   |                                                                                                                                                             | 14  | 22    | 100  | μF   |

| C <sub>OUT</sub>            | Output Filter Capacitor ESR                               | $0mA \le I_{OUT} \le I_{OUT-MAX}$                                                                                                                           | 0   |       | 20   | mΩ   |

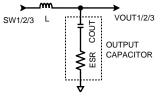

| L                           | Output Filter Inductance                                  | $\begin{array}{c c} \hline \\ \hline $                                      |     | 1     |      | μH   |

| V <sub>OUT-TOP</sub>        | Output voltage top range,<br>with Register R0 = 7Fh       | Feedback pin connected to V <sub>OUT</sub>                                                                                                                  |     | 1.208 |      | V    |

| V <sub>FB-TOP-</sub> TOL    | Feedback pin voltage tolerance                            | $V_{OUT} = V_{OUT-TOP}, I_{OUT} = 0.1*I_{OUT-MAX}$                                                                                                          | -2% |       | +2.5 | %    |

| V <sub>OUT-DEFAULT</sub>    | Output voltage, power-up default                          | $-V_{OUT} = V_{OUT-DEFAULT}, I_{OUT} = 0.1*I_{OUT}$                                                                                                         |     | 1.05  |      | V    |

| V <sub>FB-DEFAULT-TOL</sub> | Feedback pin voltage tolerance                            |                                                                                                                                                             | -2% |       | +2   | %    |

| V <sub>OUT-BOTTOM</sub>     | Output voltage bottom<br>range, with Register R0 =<br>00h | Vout = Vout-Bottom, Iout = 0.1*Iout-                                                                                                                        |     | 0.7   |      | V    |

| V <sub>FB-</sub> BOTTOM-TOL | Feedback pin voltage tolerance                            |                                                                                                                                                             | -2% |       | +2.5 | %    |

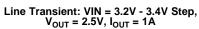

| A)/                         | DC Line regulation                                        | $\begin{array}{l} 3V \leq V_{\text{IN}} \leq 5V,  V_{\text{OUT}} = V_{\text{OUT-DEFAULT}}, \\ I_{\text{OUT}} = 0.5 \ ^{*} \ I_{\text{OUT-MAX}} \end{array}$ |     | 0.2   |      | %/V  |

| ΔV <sub>OUT</sub>           | DC Load regulation                                        | $V_{IN} = 5V, V_{OUT} = V_{OUT-DEFAULT}, 0.1 * I_{OUT-MAX} \le I_{OUT} \le I_{OUT-MAX}$                                                                     |     | 0.1   |      | %/A  |

| I <sub>FB</sub>             | Feedback pin input bias<br>current                        | V <sub>FB</sub> = 1.208V ; (pin has internal resistor divider)                                                                                              |     | 2.3   | 5    | μA   |

| R <sub>DS-ON-HS</sub>       | High Side Switch On Resistance                            | Management alia ta alia                                                                                                                                     |     | 50    | 105  |      |

| R <sub>DS-ON-LS</sub>       | Low Side Switch On Resistance                             | Measured pin-to-pin                                                                                                                                         |     | 65    | 100  | mΩ   |

| T <sub>SCALING</sub>        | V <sub>OUT</sub> Scaling Step Time                        | 100 mV steps on $V_{SW1}$ ,<br>C <sub>OUT-TOTAL</sub> = 22 $\mu$ F                                                                                          |     | 25    |      | μS   |

| STARTUP                     |                                                           | · · · · · · · · · · · · · · · · · · ·                                                                                                                       |     |       |      |      |

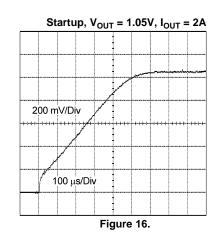

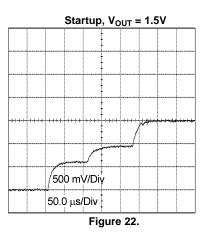

| T <sub>START</sub>          | Internal soft-start (turn on tim                          | ne)                                                                                                                                                         |     | 0.5   |      | ms   |

### Bucks 2 and 3 Electrical Characteristics <sup>(1) (2) (3)</sup>

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range  $-40^{\circ}C \le T_J \le +105^{\circ}C$ .

| Symbol                   | Parameter                                | Conditions                                          | Min  | Тур | Max  | Unit |

|--------------------------|------------------------------------------|-----------------------------------------------------|------|-----|------|------|

| I <sub>Q-NO-LOAD-2</sub> | Quiescent supply current off PVIN2 pin   | Buck 2 is enabled, but not loaded, switching in PWM |      | 3   | 8    | 0    |

| I <sub>Q-NO-LOAD-3</sub> | Quiescent supply current of<br>PVIN3 pin | Buck 3 is enabled, but not loaded, switching in PWM |      | 3   | 8    | mA   |

| I <sub>OUT-MAX</sub>     | Continuous maximum load current          | Bucks 2 and 3 are enabled, switching in PWM*        | 1    |     |      |      |

| I <sub>PEAK</sub>        | Peak switching current limit             | Bucks 2 and 3 are enabled, switching in PWM         | 1.25 | 1.5 | 1.75 | A    |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are with respect to the potential at the GND pin.

(3) VIN refers to these power pins connected together: AVDD = VDDL = VDDADC = DVDD = PVIN1A = PVIN1B = PVIN2 = PVIN3

Copyright © 2011–2013, Texas Instruments Incorporated

www.ti.com

TRUMENTS

XAS

### Bucks 2 and 3 Electrical Characteristics (1) (2) (3) (continued)

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range  $-40^{\circ}C \le T_J \le +105^{\circ}C$ .

| Symbol                  | Parameter                                                            | Conditions                                                             | Min                                                                                                                                                                                                                                                                           | Тур | Max | Unit |

|-------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

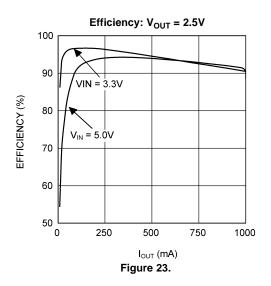

| η <sub>SW2-5V</sub>     | Efficiency needs Duck 2                                              | $I_{OUT} = 0.4A, V_{IN} = 5.0V$                                        |                                                                                                                                                                                                                                                                               | 92% |     | 0/   |

| η <sub>SW2-3.3V</sub>   | Efficiency peak, Buck 2                                              | I <sub>OUT</sub> = 0.2A, V <sub>IN</sub> = 3.3V                        |                                                                                                                                                                                                                                                                               | 93% |     | %    |

| η <sub>SW3-5V</sub>     | Efficiency needs Duck 2                                              | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                 | 0/                                                                                                                                                                                                                                                                            |     |     |      |

| η <sub>SW3-3.3V</sub>   | Efficiency peak, Buck 3                                              |                                                                        | %                                                                                                                                                                                                                                                                             |     |     |      |

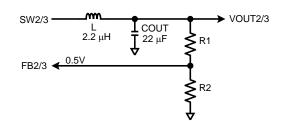

| C <sub>IN</sub>         | Input Capacitor                                                      |                                                                        | 7                                                                                                                                                                                                                                                                             | 10  |     |      |

| 0                       | Output Filter Capacitor                                              |                                                                        | 14                                                                                                                                                                                                                                                                            | 22  | 100 | μF   |

| C <sub>OUT</sub>        | Output Filter Capacitor ESR                                          | $IOUT \le IOUT \le IOUT-MAX$                                           | 0                                                                                                                                                                                                                                                                             |     | 20  | mΩ   |

| L                       | Output Filter Inductance                                             |                                                                        | $0V$ 92% $3V$ 93% $0V$ 94% $3V$ 97% $7$ 10 $14$ 22 $0$ 1 $0$ 1 $0.5$ $0.5$ $.5V$ , $I_{OUT} = 0$ $3.5$ $.5V$ , $I_{OUT} = 0$ $3.5$ $.5V$ , $I_{OUT} = 0$ $0.2$ $\le I_{OUT-MIN}$ $0.3$ $0.1$ $170$ $125$ $0.5$ |     | μH  |      |

| V <sub>FB</sub>         | Feedback voltage                                                     | $I_{OUT} = 0.1^* I_{OUT-MAX}$                                          |                                                                                                                                                                                                                                                                               | 0.5 |     | V    |

| V <sub>FB-TOL</sub>     | Feedback pin voltage tolerance                                       | Output voltage set using external                                      | -2%                                                                                                                                                                                                                                                                           |     | +2  | %    |

| V <sub>OUT-TOP</sub>    | Output voltage highest<br>setting using external<br>resistor divider |                                                                        |                                                                                                                                                                                                                                                                               | 3.5 |     | v    |

| V <sub>OUT-BOTTOM</sub> | Output voltage lowest<br>setting using external<br>resistor divider  |                                                                        |                                                                                                                                                                                                                                                                               | 1.0 |     | V    |

| A) /                    | DC Line regulation                                                   |                                                                        |                                                                                                                                                                                                                                                                               | 0.2 |     | %/V  |

| ΔV <sub>OUT</sub>       | DC Load regulation                                                   |                                                                        |                                                                                                                                                                                                                                                                               | 0.3 |     | %/A  |

| I <sub>FB</sub>         | Feedback pin input bias current                                      | V <sub>FB</sub> = 0.5V                                                 |                                                                                                                                                                                                                                                                               | 0.1 | 1   | μA   |

| R <sub>DS-ON-HS</sub>   | High Side Switch On Resistance                                       | Macaurad ain to nin                                                    |                                                                                                                                                                                                                                                                               | 170 | 300 |      |

| R <sub>DS-ON-LS</sub>   | Low Side Switch On Resistance                                        | weasured pin-to-pin                                                    |                                                                                                                                                                                                                                                                               | 125 | 190 | mΩ   |

| STARTUP                 |                                                                      | •                                                                      | •                                                                                                                                                                                                                                                                             | •   |     |      |

| T <sub>START</sub>      |                                                                      | T = 0V, no load, LC = recommended<br>to $V_{OUT}$ = 95% of final value |                                                                                                                                                                                                                                                                               | 0.5 |     | ms   |

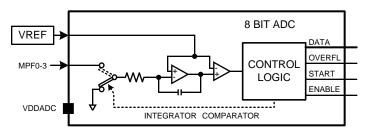

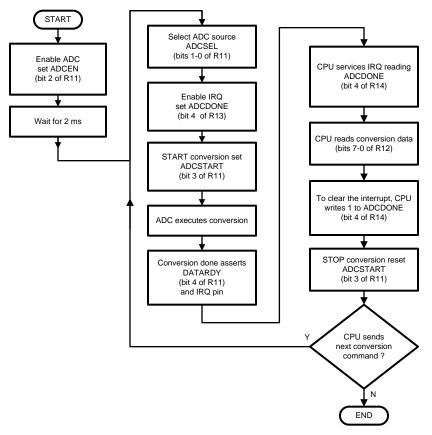

# ADC and Comparators Electrical Characteristics <sup>(1) (2) (3)</sup>

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range -40°C ≤  $T_J$  ≤ +105°C.

| Symbol                 | Parameter                                                              | Conditions                          | Min | Тур | Max | Units |

|------------------------|------------------------------------------------------------------------|-------------------------------------|-----|-----|-----|-------|

| I <sub>QSC-ADC-0</sub> | VDDADC pin quiescent<br>current, part disabled                         | EN pin LOW                          |     | 0.1 | 10  |       |

| I <sub>QSC-ADC-1</sub> | VDDADC pin quiescent<br>current, part enabled but<br>ADC not enabled   | EN pin HIGH, ADCEN=0                |     | 45  |     |       |

| I <sub>ADC-0</sub>     | VDDADC pin operating<br>current with ADC enabled<br>but not converting | EN pin HIGH, ADCEN=1,<br>ADCSTART=0 |     | 260 |     | μA    |

| I <sub>ADC-1</sub>     | VDDADC pin operating<br>current with ADC enabled<br>and converting     | EN pin HIGH, ADCEN=1,<br>ADCSTART=1 |     | 150 |     |       |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are with respect to the potential at the GND pin.

(3) VIN refers to these power pins connected together: AVDD = VDDL = VDDADC = DVDD = PVIN1A = PVIN1B = PVIN2 = PVIN3

10 Submit Documentation Feedback

#### SNVS644A - DECEMBER 2011 - REVISED MARCH 2013

# ADC and Comparators Electrical Characteristics <sup>(1) (2) (3)</sup> (continued)

Unless otherwise noted,  $V_{IN}$ = 5.0V where:  $V_{IN}$ =AVDD=VDDL=VDDADC=DVDD=VDDMFP=PVIN1A=PVIN1B=PVIN2=PVIN3, except VPWI=2.5V. The application circuit used is the one shown in Figure 3. Limits in standard type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the full operating junction temperature range  $-40^{\circ}C \le T_J \le +105^{\circ}C$ .

| Symbol                     | Parameter                               | Conditions                                                    | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Тур                    | Max   | Units |

|----------------------------|-----------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|-------|

| N/                         |                                         | T = 25°C                                                      | 1.220                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.225                  | 1.230 |       |

| V <sub>REF</sub>           | Internal Reference Voltage              | T= 0 to 105°C                                                 | 1.220         1.225         1.23           1.200         1.225         1.23           -2         +2         +2           -0.5         0.5         0.5           -0.5         2 * V <sub>REF</sub> -0.5           2         VREF         -0.5           -0.5         0.5         0.5           -0.5         2 * V <sub>REF</sub> -0.5           -0.5         0.5         0.5           -0.5         2 * V <sub>REF</sub> -0.5           -0.5         0.5         0.5           -0.5         2 * V <sub>REF</sub> -0.5           -0.5         0.1         1           0.1         1         1           CMPxHYS are         V <sub>REF</sub> -0.08         -0.1           CMPxHYS are         V <sub>REF</sub> -0.1 | 1.250                  | V     |       |

| INL                        | Core ADC integral non-<br>linearity     | V <sub>REF</sub> = 1.225*                                     | -2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        | +2    | LSB   |

| DNL                        | Core ADC differential non-<br>linearity | V <sub>REF</sub> = 1.225*                                     | -0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        | 0.5   | LSB   |

| V <sub>ADC_IN_TOP</sub>    | ADC input voltage range, top            |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 * V <sub>REF</sub>   |       | V     |

| V <sub>ADC_IN_BOTTOM</sub> | ADC input voltage range, bottom         |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>REF</sub>       |       | V     |

| t <sub>CONV</sub>          | Conversion time                         |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        | 5     | ms    |

| t <sub>WARM-REF</sub>      | Warm-up time of reference               | After EN pin high <sup>(1)</sup>                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                      |       | ms    |

| tu                         | Warm-up time of ADC                     | After enabling the ADC <sup>(1)</sup>                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                      |       | ms    |

| COMPARATOR (               | The comparators use the sa              | me reference as the ADC.)                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |       |       |

| I <sub>Q-VDDMFP</sub>      | Quiescent current of<br>VDDMFP pin      | MFP pins are configured as<br>comparator inputs, all grounded |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.1                    | 1     | μA    |

| V_comp_rise                | Comparator rising edge trigger level    | Hysteresis window bits CMPxHYS are                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>REF</sub>       |       | M     |

| V_comp_fall                | Comparator falling edge trigger level   | 0.                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>REF</sub> -0.08 |       | V     |

| V_comp_rise                | Comparator rising edge trigger level    | Hysteresis window bits CMPxHYS are                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>REF</sub>       |       | v     |

| V_comp_fall                | Comparator falling edge trigger level   | 1.                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | V <sub>REF</sub> -0.05 |       | V     |

### TEXAS INSTRUMENTS

#### SNVS644A – DECEMBER 2011 – REVISED MARCH 2013

www.ti.com

-

Figure 7.

### **FEXAS NSTRUMENTS**

www.ti.com

#### SNVS644A - DECEMBER 2011 - REVISED MARCH 2013

IOUT 1A/Div

50.0 µs/Div

#### Figure 14.

Figure 15.

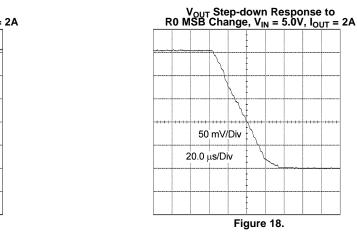

$V_{OUT}$  Step-up Response to R0 MSB Change,  $V_{IN} = 5.0V$ ,  $I_{OUT} = 2A$ 50 mV/Div 10.0 µs/Div

Figure 18.

#### SNVS644A - DECEMBER 2011 - REVISED MARCH 2013

### **Typical Performance Characteristics, Buck 2**

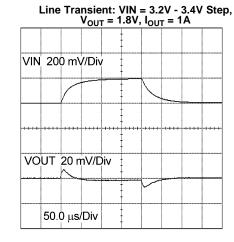

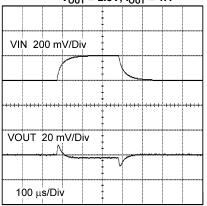

Load Transient:  $V_{IN} = 5.0V$ ,  $V_{OUT} = 1.8V$  $I_{OUT}$  step = 0A...1.0A

20 mV/Div

0.5A/Ďiv 20.0 μs/Div

Figure 21.

#### Figure 20.

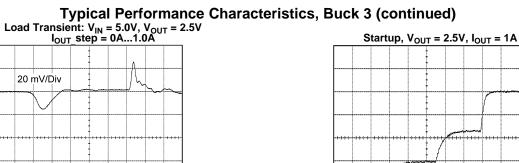

### **Typical Performance Characteristics, Buck 3**

Figure 24.

Texas Instruments

www.ti.com

SNVS644A – DECEMBER 2011 – REVISED MARCH 2013

0.5A/Div

20.0 µs/Div

Figure 25.

500 mV/Div

50.0 μs/Div

Figure 26.

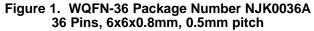

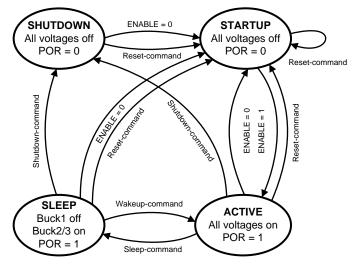

### LM10503 GENERAL DESCRIPTION

LM10503 is a PWI 2.0 compliant Energy Management Unit for reducing power consumption of the digital core of Systems-on-a-Chip (SoCs), ASICs, and processors. It operates cooperatively with processors that incorporate Advanced Power Controller (APC) to provide Adaptive or Dynamic Voltage Scaling (AVS or DVS) which significantly improves the system efficiency when compared to fixed output voltage implementations.

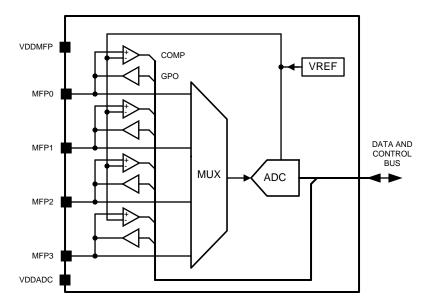

The device incorporates three high-efficiency synchronous buck regulators that deliver three output voltages from a single power source. The device also includes a Multifunctional Block that comprises a 4-channel ADC, comparators and GPOs.

The following table summarizes the key features of the device:

| Functionality                                        | BUCK1                  | BUCK2                             | BUCK3                     |  |

|------------------------------------------------------|------------------------|-----------------------------------|---------------------------|--|

| Power on output voltage default                      | 1.05V                  | Configurable using an             | external resistor divider |  |

| Output voltage, range minimum                        | 0.7                    | 1                                 | 1                         |  |

| Output voltage, range maximum                        | 1.2                    | 3.5                               | 3.5                       |  |

| Output voltage programming resolution                | 4mV                    | N/A                               | N/A                       |  |

| Output voltage register                              | R0                     | N/A                               | N/A                       |  |

| Output voltage change with external resistor divider | No                     | Yes                               | Yes                       |  |

| Maximum output current                               | 2A                     | 1A                                | 1A                        |  |

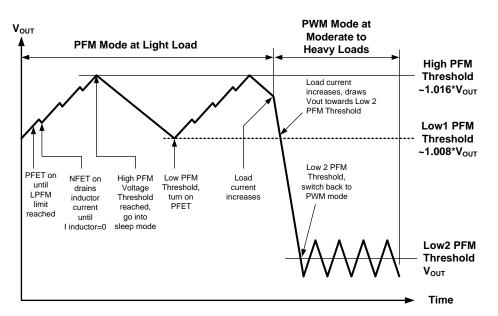

| Operation mode                                       | PWM Only               | PWM or                            | PWM/PFM                   |  |

| Enable pin LOW                                       | All bucks disabled, F  | B pins pulled low with a 22 k     | Ω internal resistor.      |  |

| Enable pin HIGH                                      |                        | All bucks are enabled.            |                           |  |

| Enable Bit                                           | N/A                    | BUCK2EN                           | BUCK3EN                   |  |

| SHUTDOWN Command                                     |                        | Turns off all bucks               |                           |  |

| RESET Command                                        | Turns on all bucks and | brings all registers to their pov | wer on default values     |  |

| SLEEP Command                                        | Turns off this buck    | No                                | effect                    |  |

| WAKEUP Command                                       | Turns on this buck     | No                                | effect                    |  |

#### Table 2. Feature Summary

### DIGITALLY ASSISTED VOLTAGE SCALING

The device is designed to be used in a voltage scaling system to lower the power dissipation by scaling the supply voltage with the clock frequency. Buck 1 supports two modes of voltage scaling: Dynamic Voltage Scaling (DVS) and Adaptive Voltage Scaling (AVS).

- DVS mode: the voltage changes are initiated by the system firmware as a result of changes in the operating frequency of the system. Pre-characterized voltage clock frequency pairs are used. This is an open loop system because it does not adapt to temperature changes or other factors.

- AVS mode: the voltage changes are initiated by the Advanced Power Controller (APC, residing in the powered IC) as a result of changes in the operating performance of the monitored system. Pre-characterized voltage clock frequency pairs are not needed. AVS is a closed loop system that provides an automatic process and temperature compensation such that for any given process, temperature, or clock frequency, the minimum supply voltage is delivered. AVS systems continuously track the system's performance and immediately optimize the supply voltage to the required lowest value. An added benefit is the automatic compensation for voltage drops caused by the power routing from the AVS regulator all the way to the internal circuitry of the powered device. As a result, maximum power savings are achieved.

The device delivers fast and controlled voltage scaling transients with the help of a digital state machine. The state machine automatically optimizes the control loop of the buck regulator to provide large voltage steps with minimal over- and undershoot. This is an important characteristic for voltage scaling systems that rely on minimal over- and undershoot to set voltages as low as possible in order to maximize the energy savings.

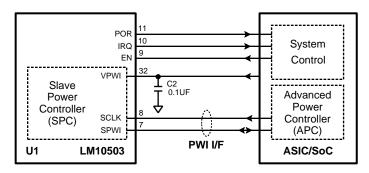

# DATA INTEFACE

The device is programmable via the low power, 2-wire PowerWise Interface (PWI). The signals associated with this interface are SPWI and SCLK. Through this interface, the user can enable/disable the device as well as select between DVS and AVS modes. By accessing the registers in the device through this interface, the user can get access and control the operation of the buck controllers, ADC, comparators and GPOs in the device. For maximum flexibility, the logic levels of these signals can be matched with the host by supplying the corresponding I/O voltage level to the VPWI pin as shown in the figure below.