## 56F8300

Peripheral User Manual Also Supports 56F8100 Device Family

56F8300 16-bit Hybrid Controllers

MC56F8300UM Rev. 10 10/2007

This manual is one of a set of three documents. For complete product information, it is necessary to have all three documents. They are: DSP56800E Reference Manual, MC56F8300 Peripheral User Manual, and Device Technical Data Sheet.

Order this document by MC56F8300UM/D - Rev. 10

**Revision History:**

See each chapter for changes

### TABLE OF CONTENTS

#### **Preface**

| Manua<br>Sugge | nce                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | oter 1<br>rview                                                                                                                                                                                                                                                                                                                                                                                                                             |

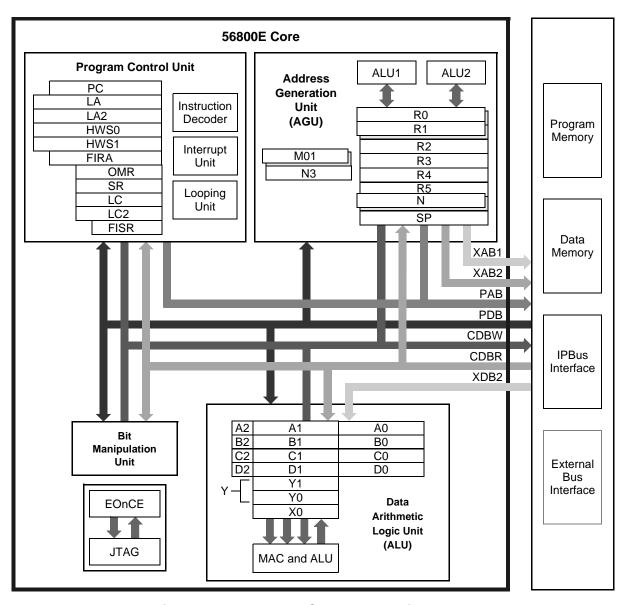

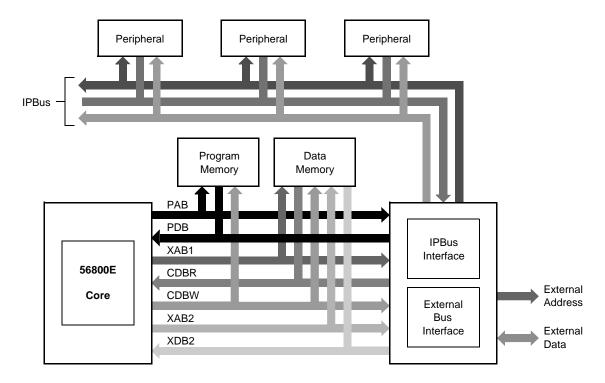

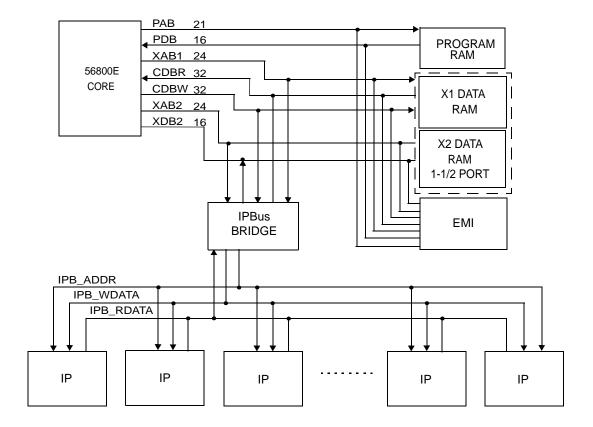

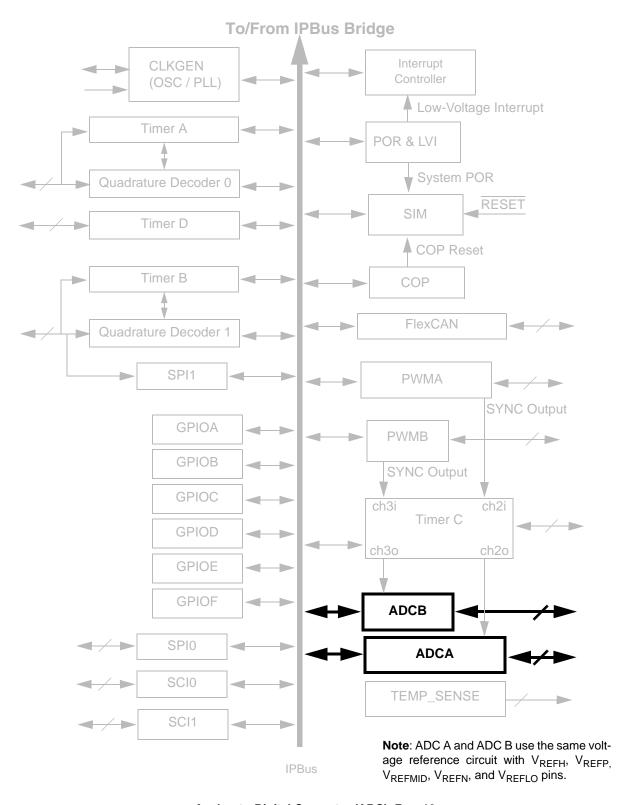

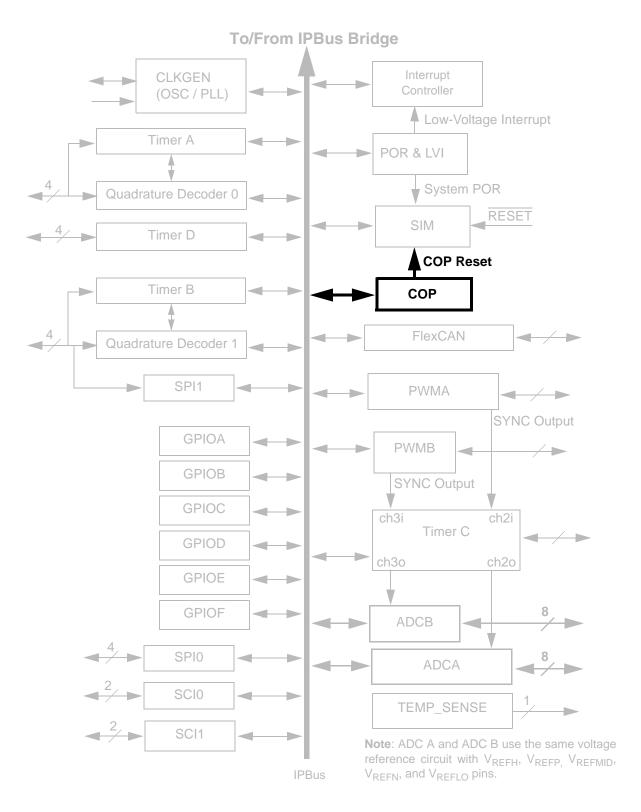

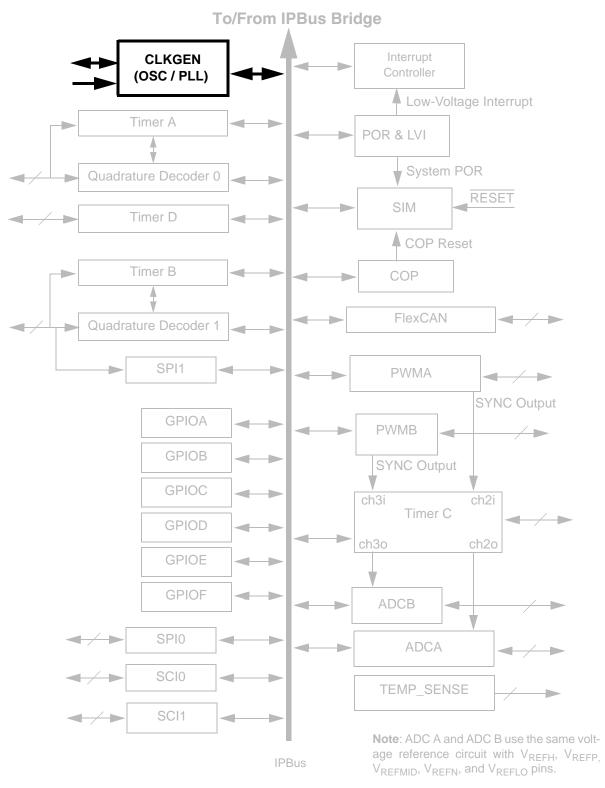

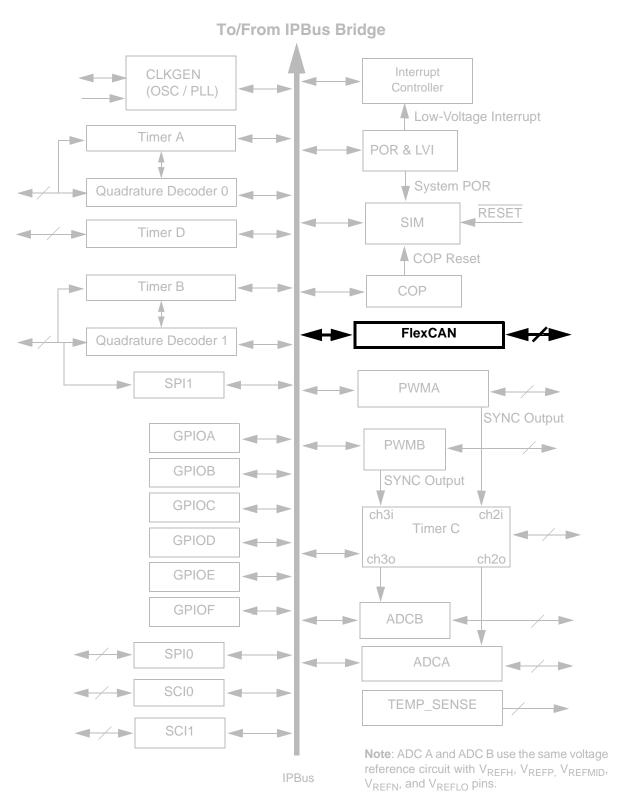

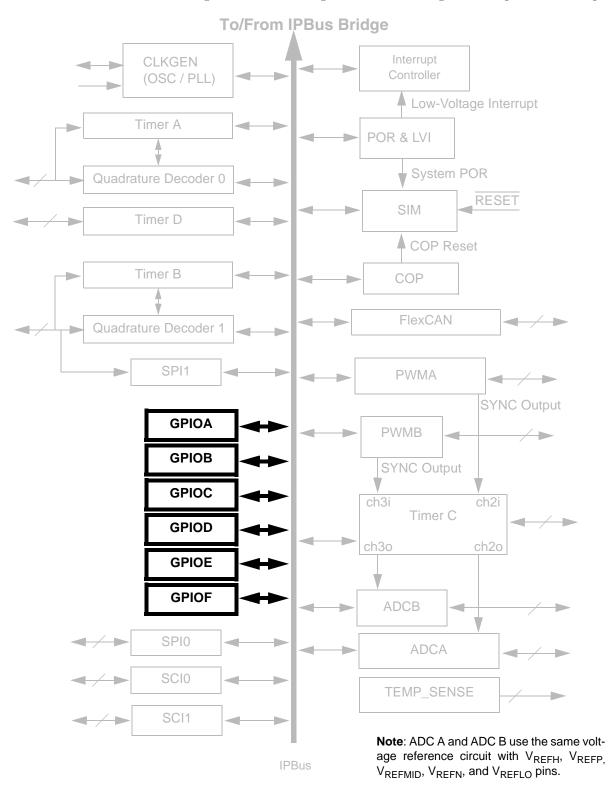

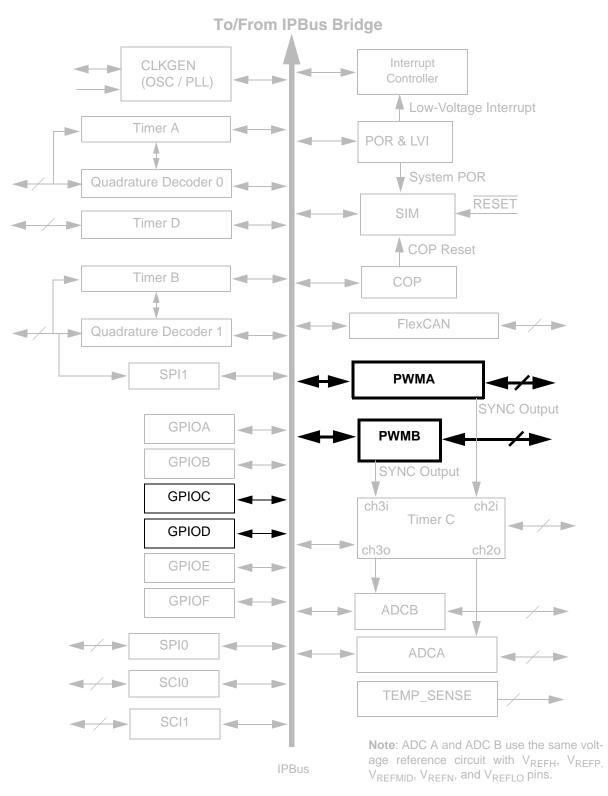

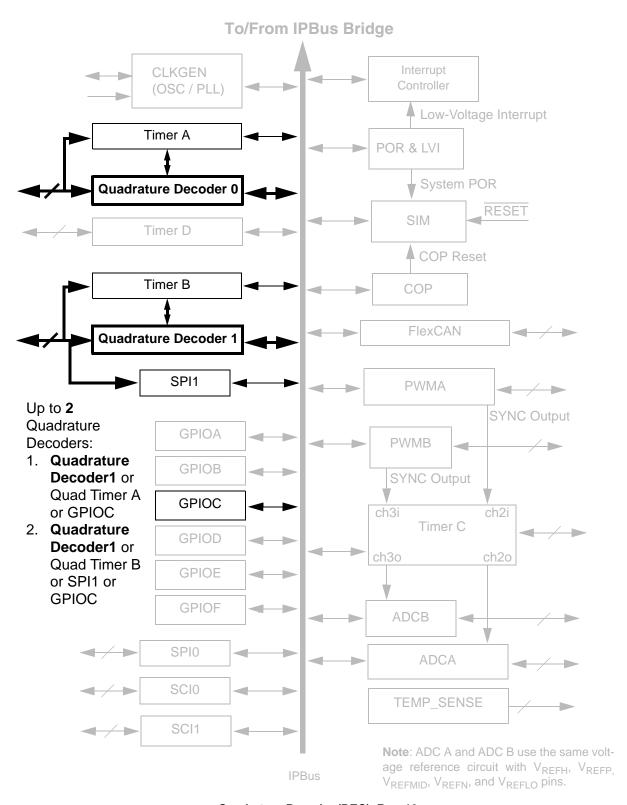

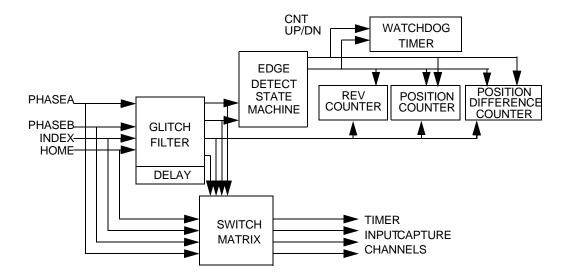

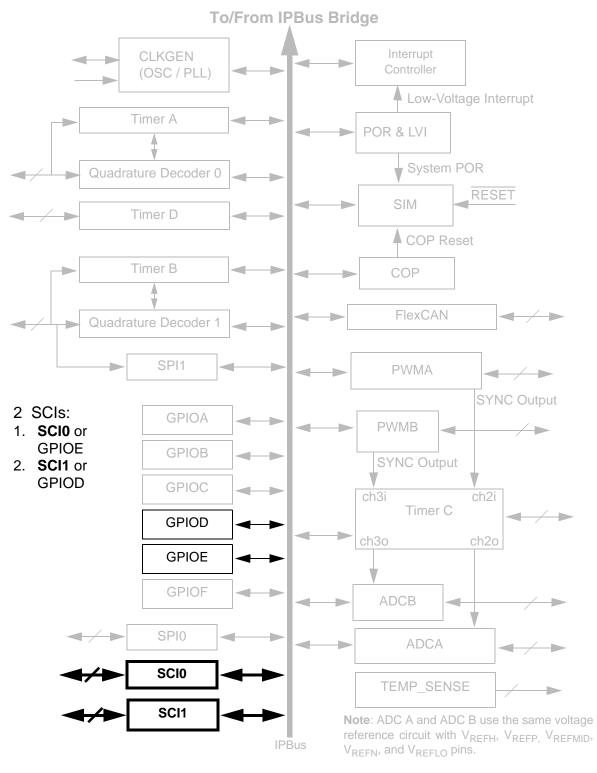

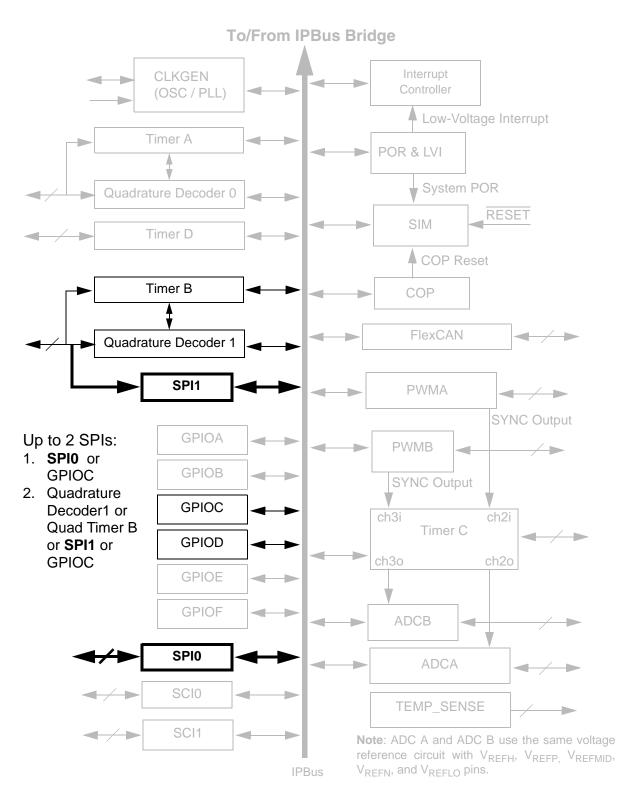

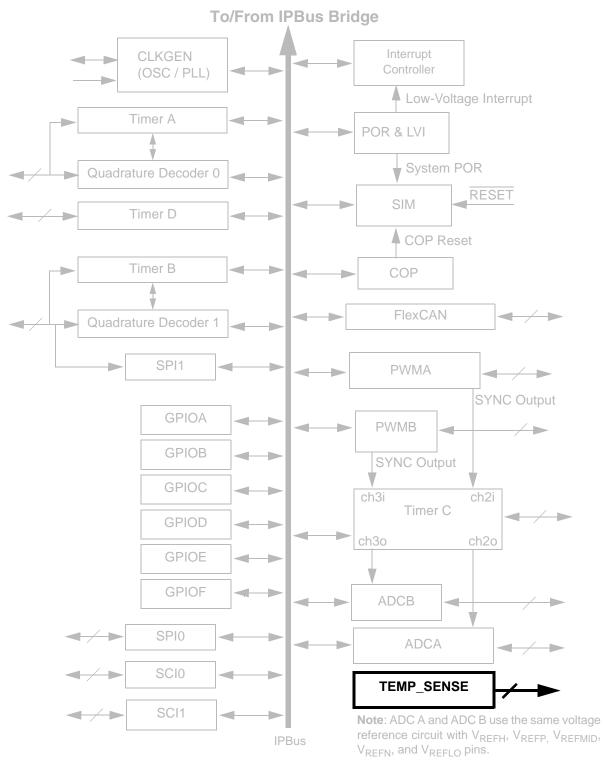

|                | Introduction to the 56800E Core. 1-3 56800E Core Enhancements 1-3 56800E Core. 1-4 System Bus Controller 1-9 Operation Method 1-10 Introduction to 56F8300/56F8100 Devices. 1-10 Applications. 1-10 Features 1-11 System Architecture and Peripheral Interface 1-11 IPBus Bridge (IPBB) 1-12 Peripheral Interrupts/Interrupt Controller Module 1-14 Peripheral Features. 1-15 Energy Information 1-21  oter 2 og-to-Digital Converter (ADC) |

| 2.1            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.1            | Features                                                                                                                                                                                                                                                                                                                                                                                                                                    |

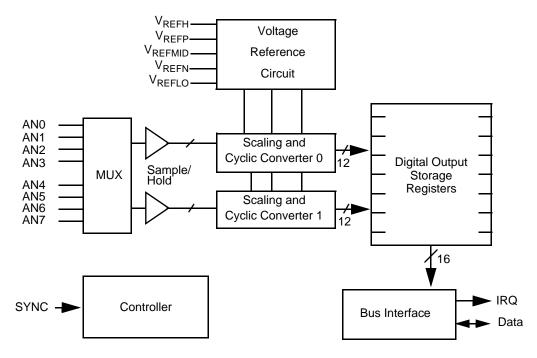

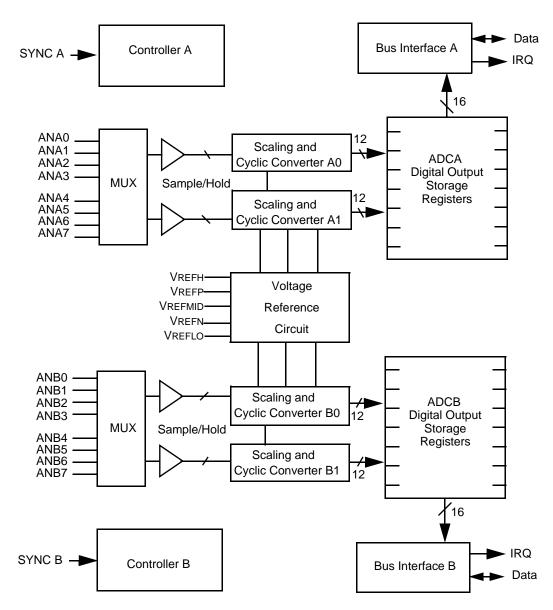

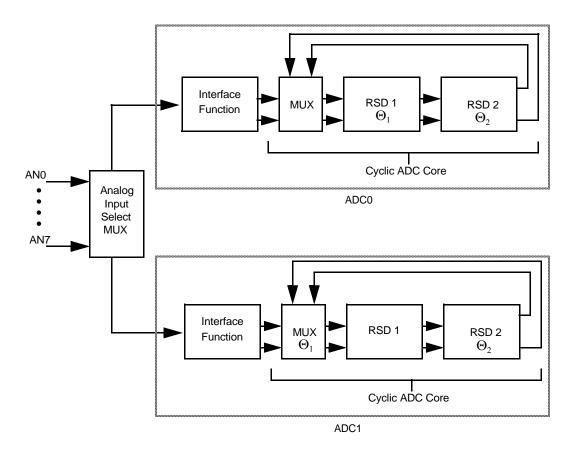

| 2.3            | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4            | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

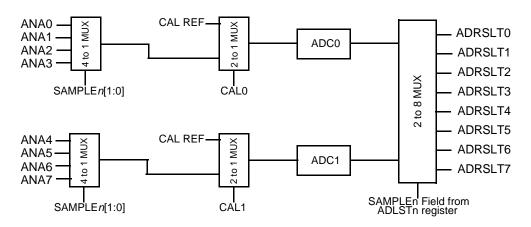

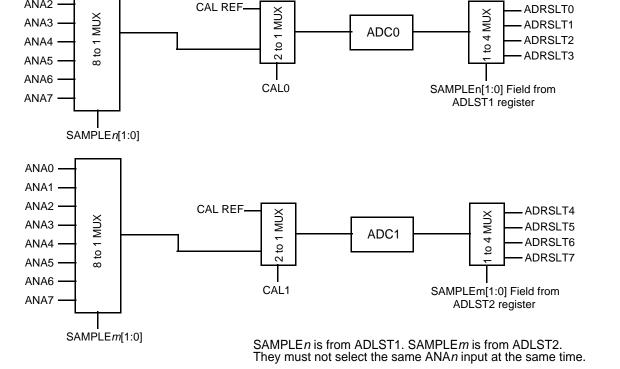

| 2.5            | Input MUX Function                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.6            | ADC Sample Conversion Operation Modes                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.6.1          | Normal Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                       |

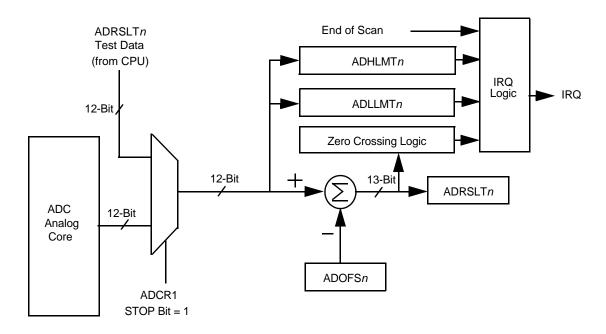

| 2.7            | ADC Data Processing                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.8            | Sequential Vs. Simultaneous Sampling                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.9            | Scan Sequencing                                                                                                                                                                                                                                                                                                                                                                                                                             |

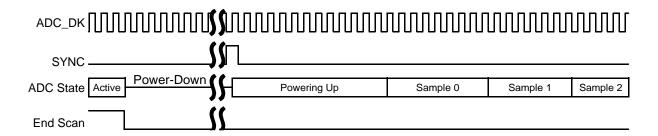

| 2.9.1          | Low Power Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.9.2          | ADC STOP Operating Mode2-16                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.10   | Calibration                                                                                                                        | 2-16 |

|--------|------------------------------------------------------------------------------------------------------------------------------------|------|

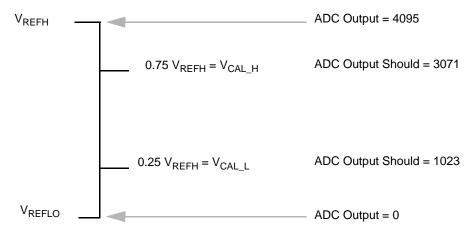

| 2.10.1 | Calibration Overview                                                                                                               | 2-16 |

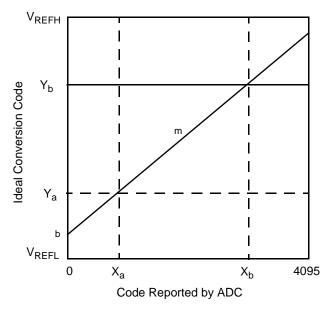

| 2.10.2 | Calibration Correction Factors                                                                                                     | 2-18 |

| 2.10.3 | Calibration Procedure                                                                                                              | 2-19 |

| 2.11   | Pin Descriptions                                                                                                                   | 2-24 |

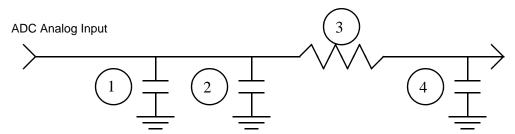

| 2.11.1 | AN0-AN7 — Analog Input Pins                                                                                                        | 2-24 |

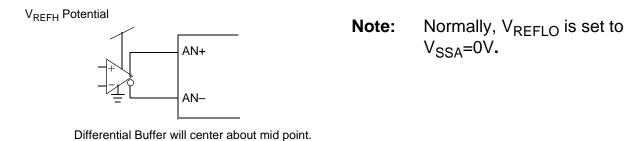

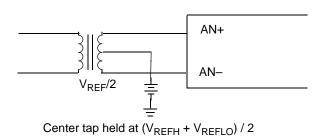

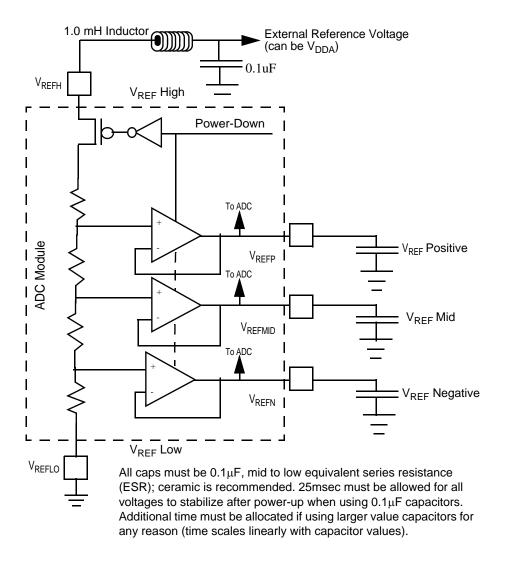

| 2.11.2 | Voltage Reference Pins—(V <sub>REFH</sub> , V <sub>REFP</sub> , V <sub>REFMID</sub> , V <sub>REFN</sub> , and V <sub>REFLO</sub> ) | 2-25 |

| 2.12   |                                                                                                                                    |      |

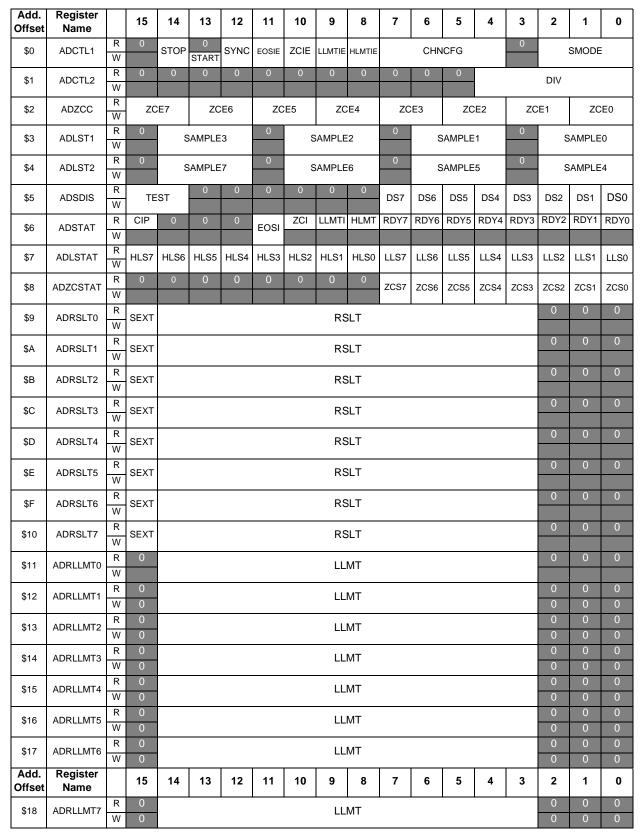

| 2.12.1 | ADC Control Register 1 (ADCTL1)                                                                                                    | 2-29 |

| 2.12.2 | ADC Control Register 2 (ADCTL2)                                                                                                    | 2-33 |

| 2.12.3 | ADC Zero Crossing Control Register (ADZCC)                                                                                         | 2-34 |

| 2.12.4 | ADC Channel List Registers (ADLST1 and ADLST2)                                                                                     | 2-35 |

| 2.12.5 | ADC Sample Disable Register (ADSDIS)                                                                                               | 2-36 |

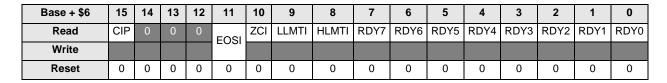

| 2.12.6 | 3                                                                                                                                  |      |

| 2.12.7 | - · · · · · · · · · · · · · · · · · · ·                                                                                            |      |

| 2.12.8 | · · · · · · · · · · · · · · · · · · ·                                                                                              |      |

| 2.12.9 |                                                                                                                                    |      |

| 2.12.1 |                                                                                                                                    |      |

| 2.12.1 | 3 /                                                                                                                                |      |

| 2.12.1 |                                                                                                                                    |      |

| 2.12.1 | 3 ( = /                                                                                                                            |      |

|        | Clocks                                                                                                                             |      |

| 2.13.1 |                                                                                                                                    |      |

| 2.14   | Interrupts                                                                                                                         | 2-48 |

|        |                                                                                                                                    |      |

|        | pter 3                                                                                                                             |      |

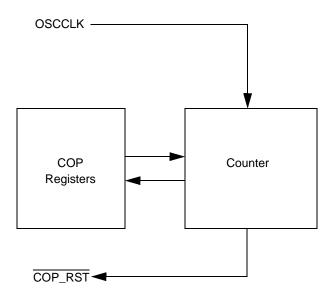

| Com    | nputer Operating Properly (COP)                                                                                                    |      |

| 3.1    | Introduction                                                                                                                       | 3-3  |

| 3.2    | Features                                                                                                                           |      |

| 3.3    | Block Diagram                                                                                                                      |      |

| 3.4    | Functional Description                                                                                                             |      |

| 3.5    | Register Definitions                                                                                                               |      |

| 3.5.1  | Control Register (COPCTL)                                                                                                          |      |

| 3.5.2  | Timeout Register (COPTO)                                                                                                           |      |

| 3.5.3  | Count Register (COPCTR)                                                                                                            |      |

| 3.6    | Timeout Specifications                                                                                                             |      |

| 3.7    | COP After Reset.                                                                                                                   |      |

| 3.8    | Clocks                                                                                                                             |      |

| 3.9    | Interrupts                                                                                                                         |      |

| J.J    | interrupto                                                                                                                         | 5-0  |

| 3.10  | Resets 3-8                                                    |

|-------|---------------------------------------------------------------|

| 3.11  | Wait Mode Operation                                           |

| 3.12  | Stop Mode Operation                                           |

| 3.13  | Debug Mode Operation                                          |

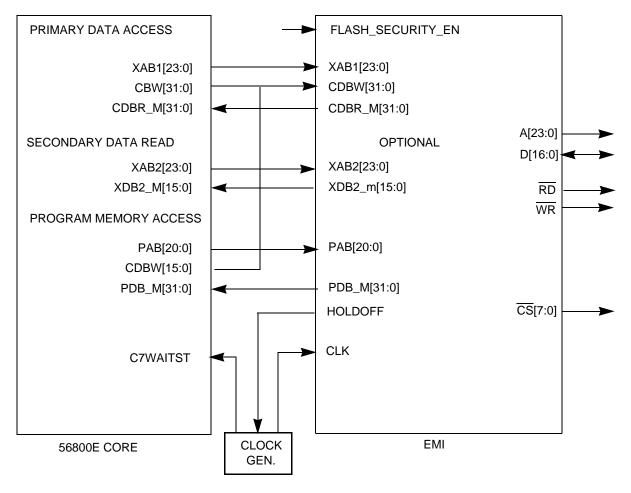

|       | pter 4<br>ernal Memory Interface (EMI)                        |

| 4.1   | Introduction                                                  |

| 4.2   | Features                                                      |

| 4.3   | Functional Description                                        |

| 4.3.1 | Core Interface Detail                                         |

| 4.4   | Block Diagram                                                 |

| 4.5   | Register Definitions                                          |

| 4.6   | Register Descriptions                                         |

| 4.6.1 | Chip Select Base Address Registers 0–3 (CSBAR0–CSBAR3)        |

| 4.6.2 | Chip Select Option Registers 0–3 (CSOR0–CSOR3)                |

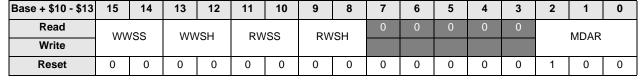

| 4.6.3 | Chip Select Timing Control Registers 0–3 (CSTC0–CSTC3)4-10    |

| 4.6.4 | Bus Control Register (BCR)                                    |

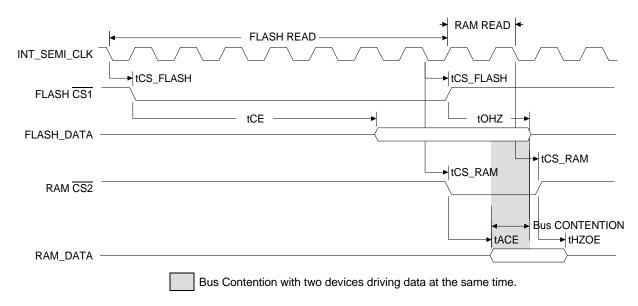

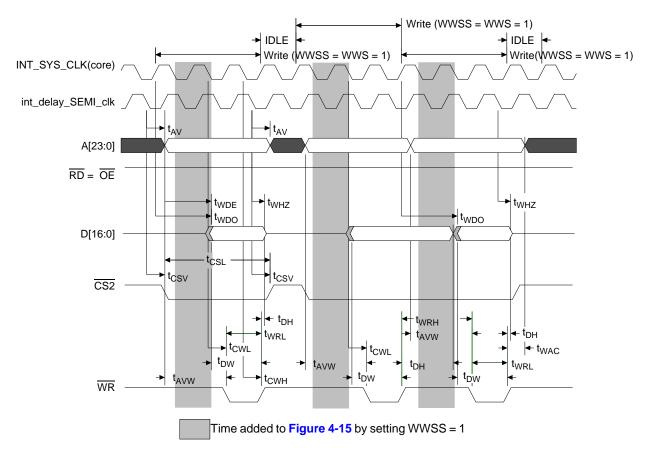

| 4.7   | Timing Specifications                                         |

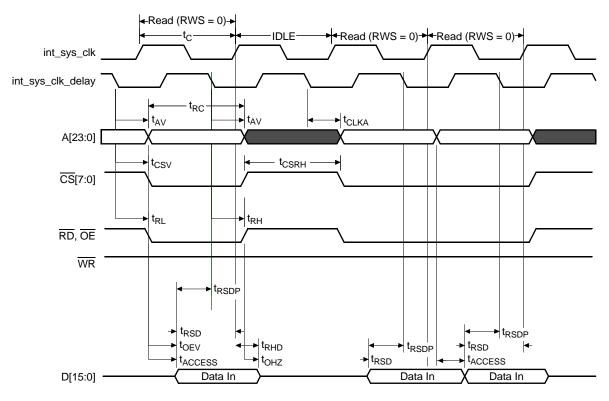

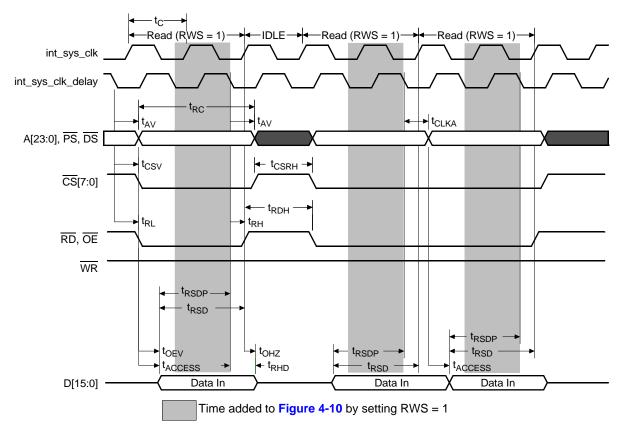

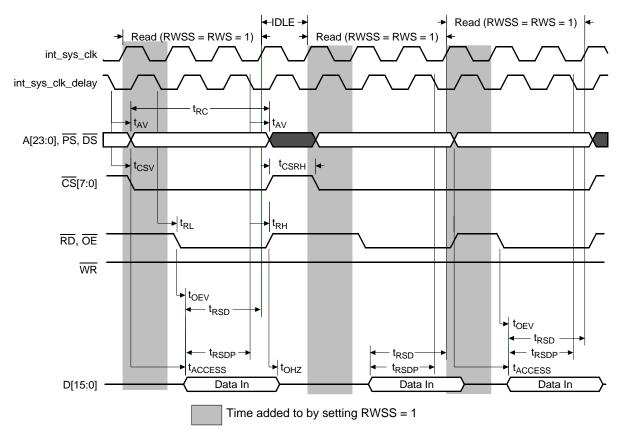

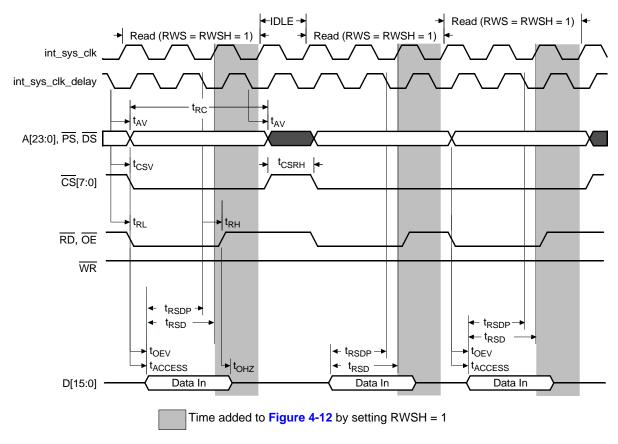

| 4.7.1 | Read Timing                                                   |

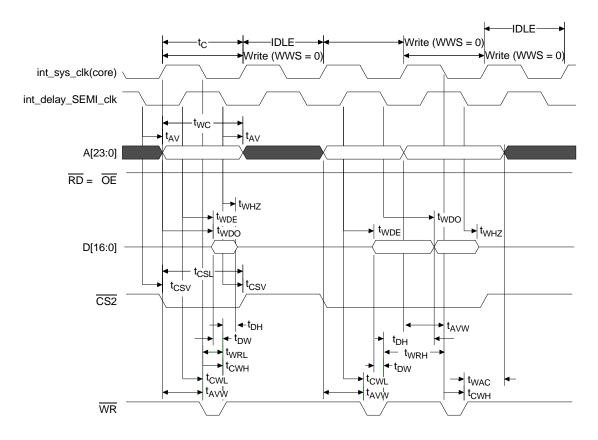

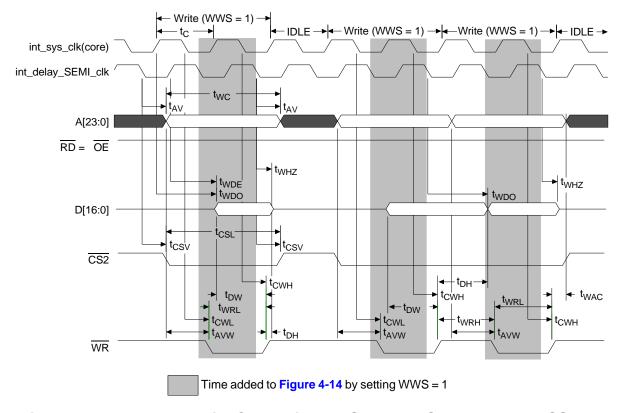

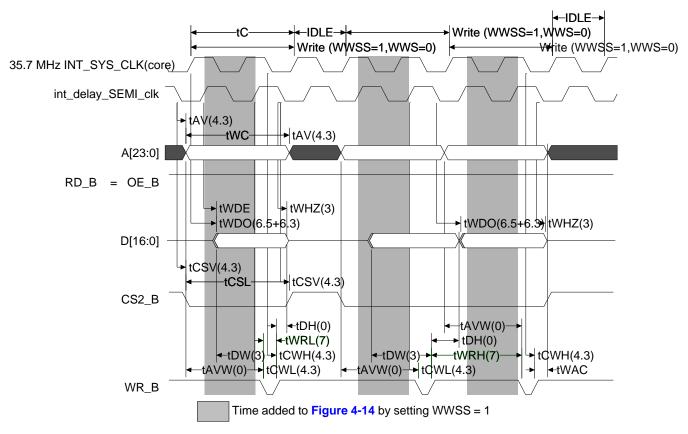

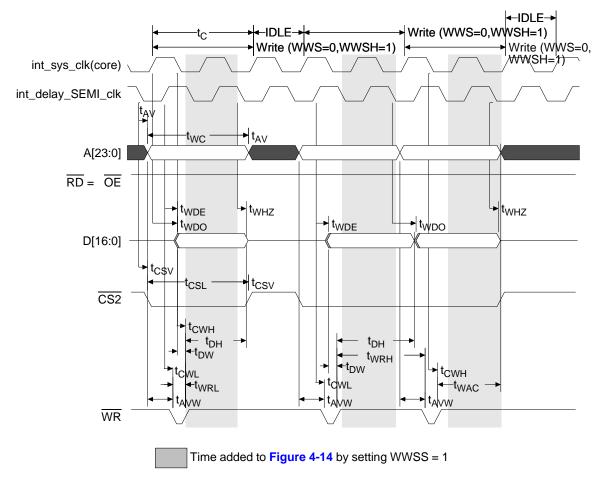

| 4.7.2 | Write Timing                                                  |

| 4.8   | Clocks                                                        |

| 4.9   | Interrupts                                                    |

| 4.10  | Resets                                                        |

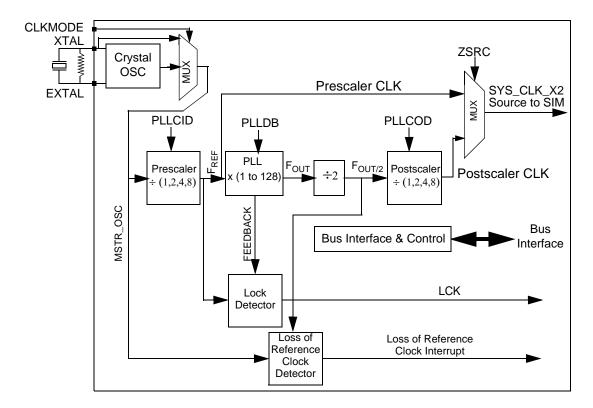

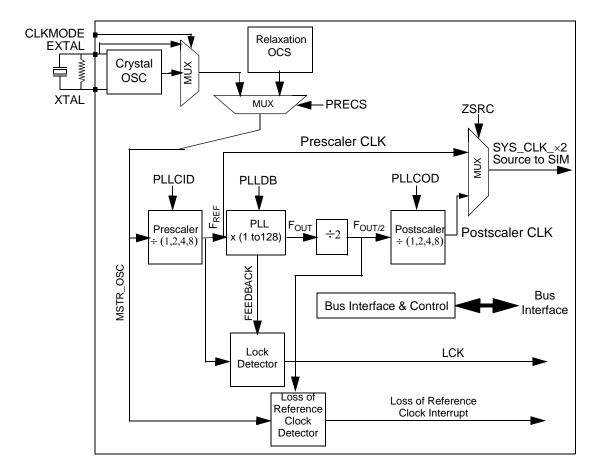

|       | pter 5<br>Chip Clock Synthesis (OCCS)                         |

| 5.1   | Introduction                                                  |

| 5.2   | Features                                                      |

| 5.3   | Block Diagram                                                 |

| 5.4   | Functional Description                                        |

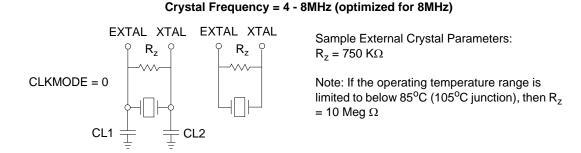

| 5.5   | Crystal Oscillator                                            |

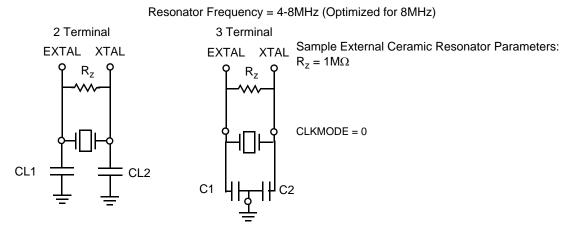

| 5.6   | Relaxation Oscillator                                         |

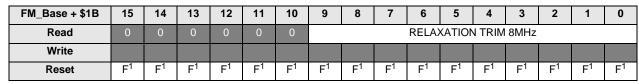

| 5.6.1 | Trimming Frequency on the Internal Relaxation Oscillator 5-10 |

| 5.6.2 | Switching Clock Sources                                       |

| 5.7   | Phase Locked Loop                                             |

| 5.7.1 | PLL Recommended Range of Operation                            |

| 5.7.2 | PLL Lock Time Specification                                   |

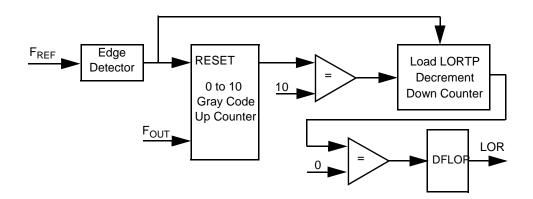

| 5.8   | PLL Frequency Lock Detector Block                             |

| 5.9   | Loss of Reference Clock Detector                              |

| 5.10   | Operating Modes                                               | 5-19        |

|--------|---------------------------------------------------------------|-------------|

| 5.10.1 | Crystal Oscillator                                            | <b>5-20</b> |

| 5.10.2 | 2 Ceramic Resonator                                           | <b>5-20</b> |

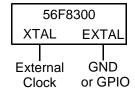

| 5.10.3 | B External Clock Source                                       | 5-21        |

| 5.10.4 | Internal Clock Source                                         | 5-21        |

| 5.11   | Register Definitions                                          | 5-22        |

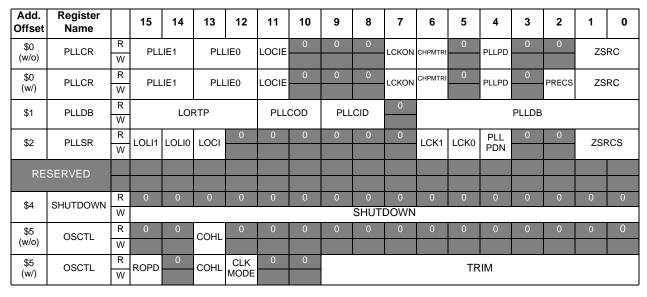

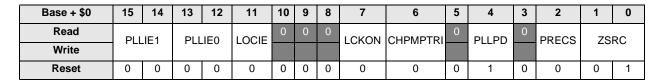

| 5.11.1 | PLL Control Register (PLLCR)                                  | 5-23        |

| 5.11.2 | PLL Divide-By Register (PLLDB)                                | 5-26        |

| 5.11.3 | PLL Status Register (PLLSR)                                   | 5-27        |

| 5.11.4 |                                                               |             |

| 5.11.5 | Oscillator Control Register w/o Relaxation Oscillator (OSCTL) | 5-30        |

| 5.11.6 | Oscillator Control Register w/ Relaxation Oscillator (OSCTL)  | 5-31        |

| 5.12   | Interrupts                                                    | 5-32        |

|        |                                                               |             |

| Cha    | pter 6                                                        |             |

| Flas   | h Memory (FM)                                                 |             |

| 6.1    | Introduction                                                  | . 6-3       |

| 6.2    | Features                                                      |             |

| 6.3    | Block Diagram                                                 |             |

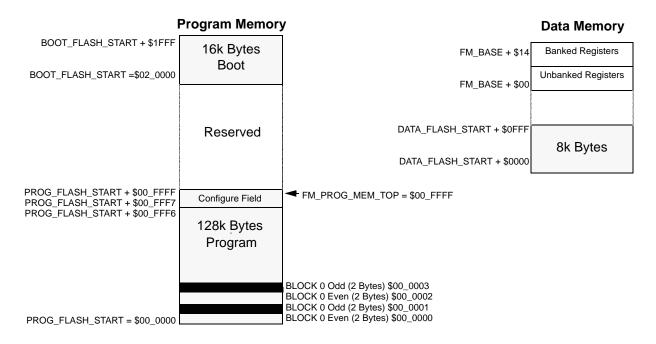

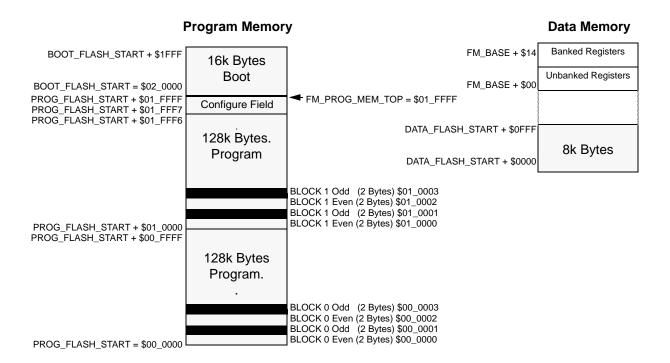

| 6.4    | Memory Map                                                    |             |

| 6.5    | Functional Description                                        |             |

| 6.5.1  | Read Operation                                                |             |

| 6.5.2  | Write Operation                                               |             |

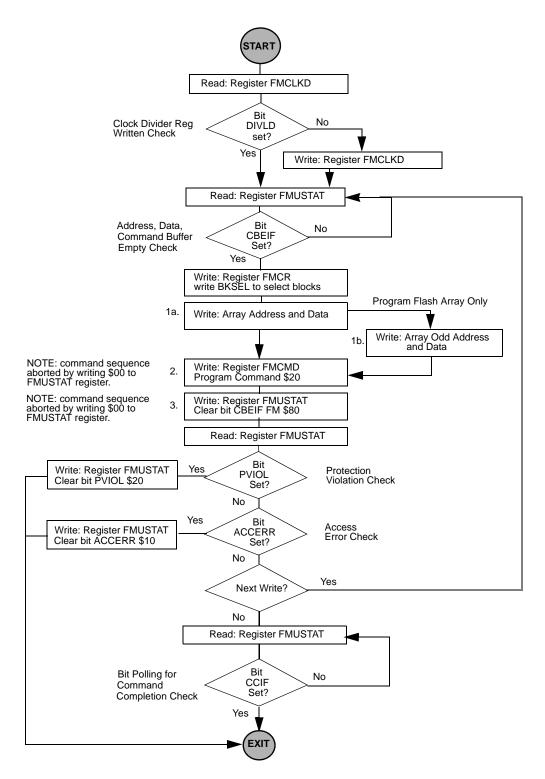

| 6.5.3  | Program and Erase Operation                                   |             |

| 6.5.4  | Flash Security Operation                                      |             |

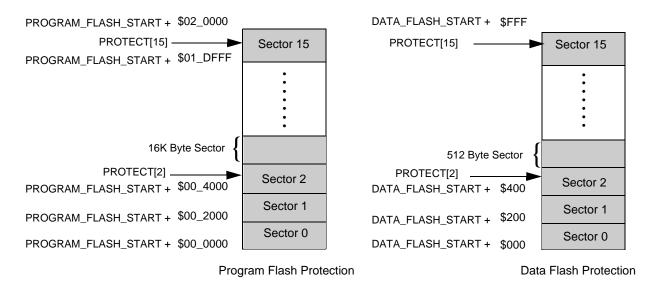

| 6.5.5  | Flash Protection Operation                                    |             |

| 6.6    | Pin Definitions                                               | 6-17        |

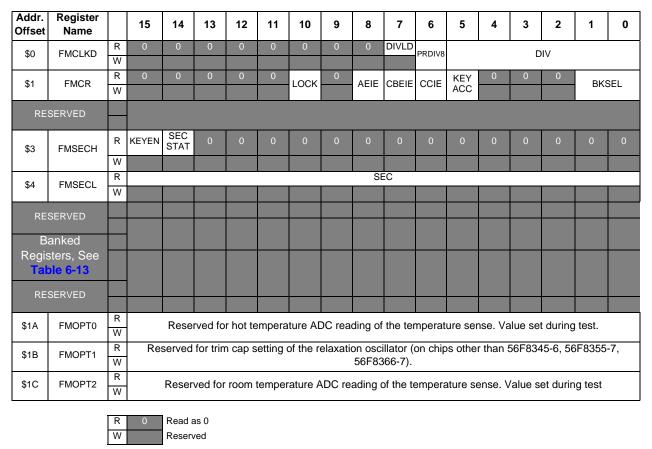

| 6.7    | Unbanked Register Definition                                  |             |

| 6.7.1  | Clock Divider Register (FMCLKD)                               |             |

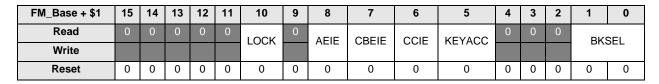

| 6.7.2  | Configuration Register (FMCR)                                 | 6-19        |

| 6.7.3  | Security Registers (FMSECH and FMSECL)                        |             |

| 6.7.4  | Flash Optional Data Registers (FMOPTn)                        | 6-23        |

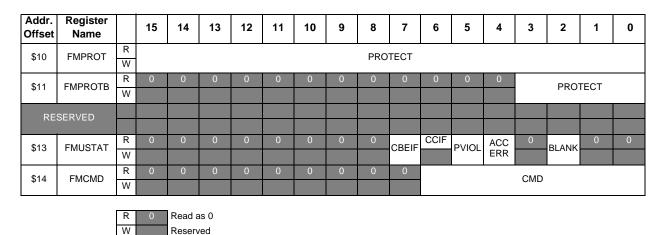

| 6.8    | Banked Register Definition                                    | 6-24        |

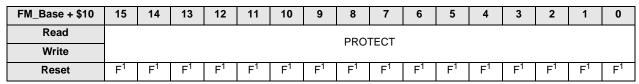

| 6.8.1  | Protection Register (FMPROT)                                  | 6-25        |

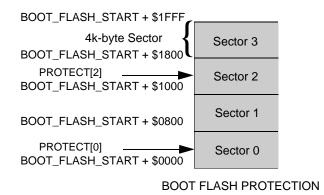

| 6.8.2  | Protection Boot Register (FMPROTB)                            |             |

| 6.8.3  | User Status Register (FMUSTAT)                                |             |

| 6.8.4  | Command Buffer Register (FMCMD)                               |             |

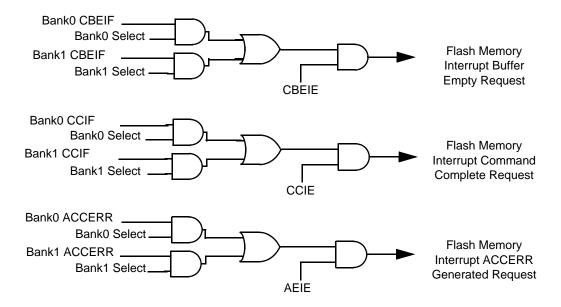

| 6.9    | Interrupts                                                    | 6-31        |

| 6.9.1  | Interrupt Operation Description                               |             |

| 6.10   | Resets                                                        |             |

|        |                                                               |             |

## Chapter 7 FlexCAN (FC)

| 7.1    | Introduction                                                    | . 7-3 |

|--------|-----------------------------------------------------------------|-------|

| 7.2    | Features                                                        | . 7-3 |

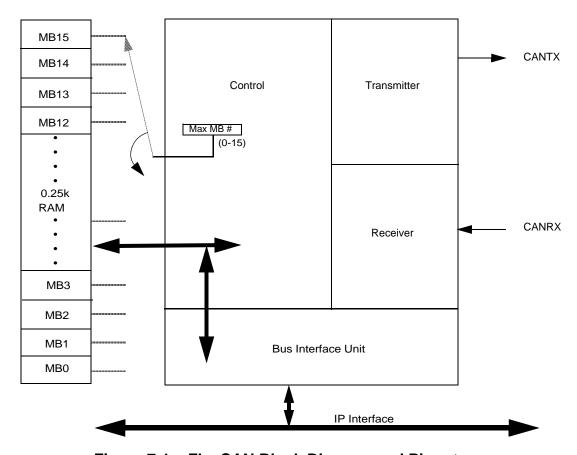

| 7.3    | Block Diagram                                                   | . 7-4 |

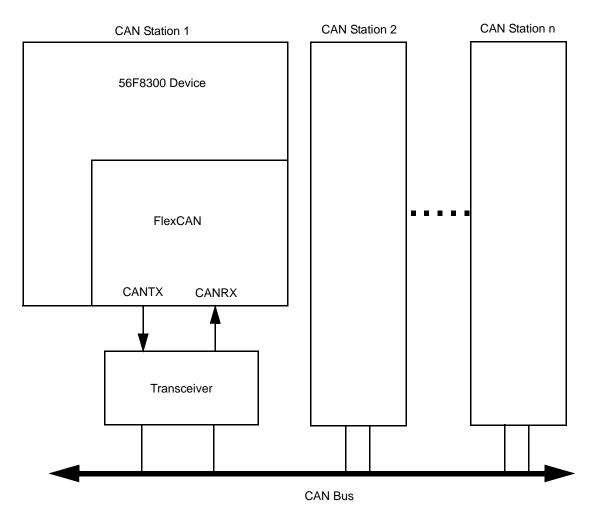

| 7.4    | Typical CAN System Diagram                                      | . 7-4 |

| 7.5    | Message Buffers                                                 |       |

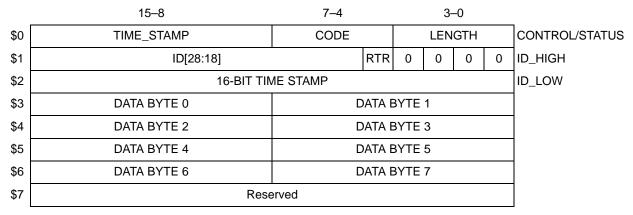

| 7.5.1  | Message Buffer Structure                                        | . 7-6 |

| 7.6    | Functional Overview                                             |       |

| 7.6.1  | Transmit Process                                                |       |

| 7.6.2  | Receive Process                                                 |       |

| 7.6.3  | Message Buffer Handling                                         |       |

| 7.6.4  | Lock/Release/Busy Mechanism and SMB Usage                       |       |

| 7.6.5  | Remote Frames                                                   |       |

| 7.6.6  | Overload Frames                                                 | 7-14  |

| 7.6.7  | Time Stamp                                                      |       |

| 7.6.8  | Listen-Only Mode                                                | 7-15  |

| 7.6.9  | Bit Timing                                                      | 7-15  |

| 7.6.10 | FlexCAN Initialization/Reset Sequence                           | 7-16  |

| 7.7    | Special Operating Modes                                         | 7-17  |

| 7.7.1  | Debug Mode                                                      | 7-17  |

| 7.7.2  | Stop Mode for Power Saving                                      | 7-18  |

| 7.7.3  | Auto Power Save Mode                                            | 7-20  |

| 7.8    | Register Defintions                                             | 7-20  |

| 7.8.1  | Module Configuration Register (FCMCR)                           | 7-25  |

| 7.8.2  | Control Register 0 (FCCTL0)                                     | 7-28  |

| 7.8.3  | Control Register 1 (FCCTL1)                                     | 7-30  |

| 7.8.4  | Free-Running Timer (FCTMR)                                      | 7-31  |

| 7.8.5  | Maximum Message Buffer Register (FCMAXMB)                       | 7-32  |

| 7.8.6  | Receive Mask Registers                                          |       |

| 7.8.7  | Receive Global Mask (FCRXGMASK_H and FCRXGMASK_L)               |       |

| 7.8.8  | Receive Buffer 14 Mask Registers (FCRX14MASK_H /_L)             |       |

| 7.8.9  | Receive Buffer 15 Mask Registers (FCRX15MASK_H /_L)             |       |

| 7.8.10 | J ( )                                                           |       |

| 7.8.11 |                                                                 |       |

| 7.8.12 |                                                                 |       |

| 7.8.13 | ( = = /                                                         |       |

| 7.9    | Interrupts                                                      |       |

| 7.10   | Resets                                                          | 7-42  |

| 7.11   | Interaction of FlexCAN Message Buffers and CodeWarrior Debugger | 7-42  |

| 7.12   | Use of Message Buffers as Data RAM                              | 7-43  |

## Chapter 8 General Purpose Input/Output (GPIO)

| 8.1                                                                                 | Introduction                                                                                                                                                                                                                                                                            | 8-3                                                             |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 8.2                                                                                 | Features                                                                                                                                                                                                                                                                                | 8-3                                                             |

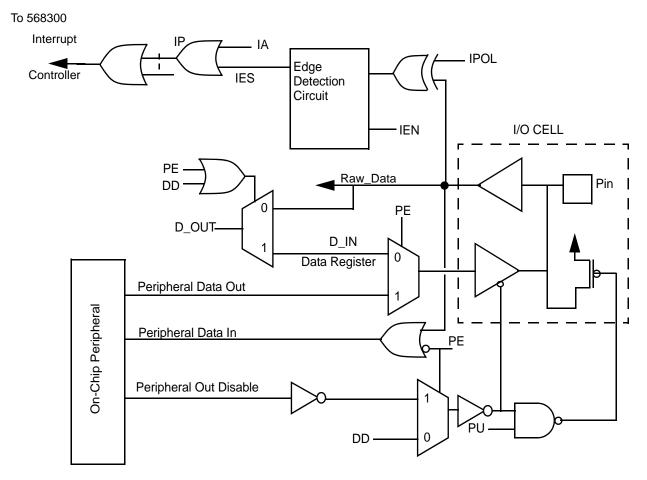

| 8.3                                                                                 | Block Diagram                                                                                                                                                                                                                                                                           | 8-3                                                             |

| 8.4                                                                                 | Operating Modes                                                                                                                                                                                                                                                                         | 8-4                                                             |

| 8.5                                                                                 | Configurations                                                                                                                                                                                                                                                                          | 8-5                                                             |

| 8.6                                                                                 | Register Definitions                                                                                                                                                                                                                                                                    | 8-6                                                             |

| 8.6.1                                                                               | Pull-Up Enable Register (PUR)                                                                                                                                                                                                                                                           | 8-8                                                             |

| 8.6.2                                                                               | Data Register (DR)                                                                                                                                                                                                                                                                      | 8-9                                                             |

| 8.6.3                                                                               | Data Direction Register (DDR)                                                                                                                                                                                                                                                           | 8-9                                                             |

| 8.6.4                                                                               | Peripheral Enable Register (PER)                                                                                                                                                                                                                                                        | 8-9                                                             |

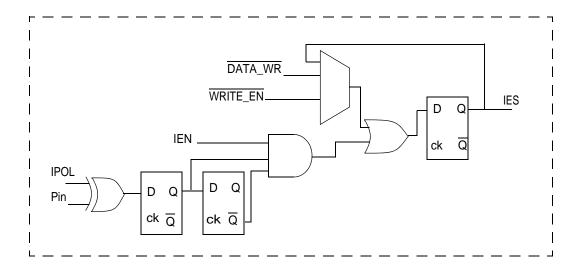

| 8.6.5                                                                               | Interrupt Assert Register (IAR)                                                                                                                                                                                                                                                         |                                                                 |

| 8.6.6                                                                               | Interrupt Enable Register (IENR)8                                                                                                                                                                                                                                                       |                                                                 |

| 8.6.7                                                                               | Interrupt Polarity Register (IPOLR)8                                                                                                                                                                                                                                                    |                                                                 |

| 8.6.8                                                                               | Interrupt Pending Register (IPR)8                                                                                                                                                                                                                                                       |                                                                 |

| 8.6.9                                                                               | Interrupt Edge Sensitive Register (IESR)                                                                                                                                                                                                                                                |                                                                 |

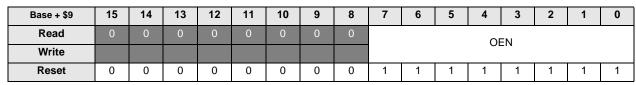

| 8.6.10                                                                              | 3                                                                                                                                                                                                                                                                                       |                                                                 |

| 8.6.11                                                                              | ,                                                                                                                                                                                                                                                                                       |                                                                 |

|                                                                                     | Clocks and Resets                                                                                                                                                                                                                                                                       | i-13                                                            |

| _                                                                                   |                                                                                                                                                                                                                                                                                         |                                                                 |

| 8.7<br>8.8<br><b>Cha</b> i                                                          | Interrupts                                                                                                                                                                                                                                                                              | 3-13                                                            |

| 8.8<br>Cha <sub>l</sub><br>Join                                                     | pter 9 t Test Action Group Port (JTAG)                                                                                                                                                                                                                                                  |                                                                 |

| 8.8  Chap Join  9.1                                                                 | pter 9 t Test Action Group Port (JTAG) Introduction.                                                                                                                                                                                                                                    | 9-3                                                             |

| 8.8<br><b>Cha</b> l<br><b>Join</b><br>9.1<br>9.2                                    | pter 9 t Test Action Group Port (JTAG) Introduction. Features                                                                                                                                                                                                                           | 9-3<br>9-3                                                      |

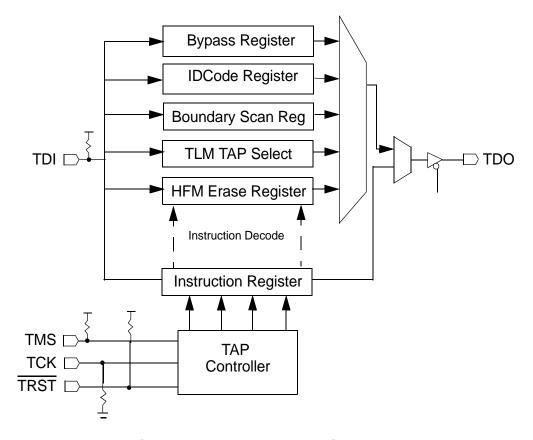

| 8.8<br>Chap<br>Join<br>9.1<br>9.2<br>9.3                                            | pter 9 t Test Action Group Port (JTAG) Introduction. Features Block Diagram                                                                                                                                                                                                             | 9-3<br>9-3<br>9-4                                               |

| 8.8<br>Chap<br>Join<br>9.1<br>9.2<br>9.3<br>9.4                                     | Interrupts  pter 9 t Test Action Group Port (JTAG)  Introduction. Features Block Diagram Functional Description                                                                                                                                                                         | 9-3<br>9-3<br>9-4<br>9-4                                        |

| 8.8<br>Chap<br>Join<br>9.1<br>9.2<br>9.3<br>9.4<br>9.4.1                            | pter 9 t Test Action Group Port (JTAG)  Introduction. Features. Block Diagram Functional Description Master TAP Instructions                                                                                                                                                            | 9-3<br>9-3<br>9-4<br>9-4                                        |

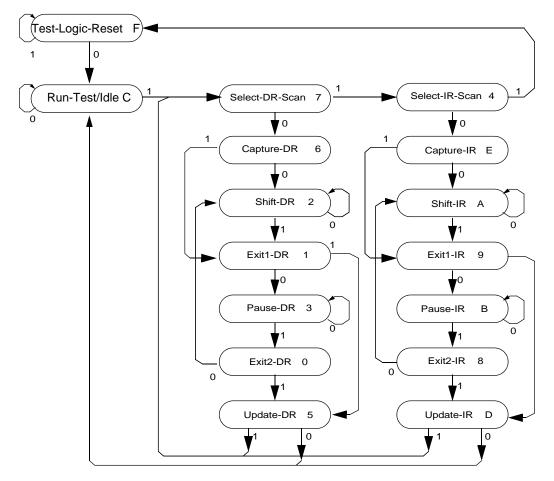

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.4.1 9.5                                   | pter 9 t Test Action Group Port (JTAG)  Introduction. Features. Block Diagram Functional Description Master TAP Instructions TAP Controller                                                                                                                                             | 9-3<br>9-3<br>9-4<br>9-4<br>9-7                                 |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.4.1 9.5 9.5.1                             | Interrupts  pter 9 t Test Action Group Port (JTAG)  Introduction. Features. Block Diagram Functional Description Master TAP Instructions  TAP Controller Operation                                                                                                                      | 9-3<br>9-3<br>9-4<br>9-4<br>9-7<br>9-8                          |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.4.1 9.5 9.5.1 9.6                         | Interrupts  pter 9 t Test Action Group Port (JTAG)  Introduction. Features  Block Diagram Functional Description Master TAP Instructions  TAP Controller Operation Memory Map.                                                                                                          | 9-3<br>9-3<br>9-4<br>9-4<br>9-7<br>9-8                          |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.5 9.5.1 9.5                               | Interrupts                                                                                                                                                                                                                                                                              | 9-3<br>9-3<br>9-4<br>9-4<br>9-7<br>9-8<br>9-11                  |

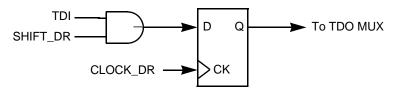

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.5 9.5.1 9.6 9.7 9.8                       | Interrupts 8  pter 9 t Test Action Group Port (JTAG)  Introduction. Features Block Diagram Functional Description Master TAP Instructions TAP Controller Operation Memory Map. Pin Description JTAG Port Architecture.                                                                  | 9-3<br>9-4<br>9-4<br>9-7<br>9-8<br>9-11                         |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.5 9.5 1 9.6 9.7 9.8 9.9                   | Interrupts 8  pter 9 t Test Action Group Port (JTAG)  Introduction. Features. Block Diagram Functional Description Master TAP Instructions TAP Controller Operation Memory Map. Pin Description JTAG Port Architecture. JTAG Boundary Scan Register                                     | 9-3<br>9-4<br>9-4<br>9-4<br>9-7<br>9-8<br>9-11<br>9-12          |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.5 9.5.1 9.6 9.7 9.8 9.9 9.10              | Interrupts 8  Poter 9 t Test Action Group Port (JTAG)  Introduction Features 8  Block Diagram 9  Functional Description 9  Master TAP Instructions 1  TAP Controller 9  Operation 1  Memory Map 1  Pin Description 9  JTAG Port Architecture 9  JTAG Boundary Scan Register 9  Clocks 9 | 9-3<br>9-4<br>9-4<br>9-4<br>9-7<br>9-11<br>9-12<br>9-12         |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.5 9.5 1 9.6 9.7 9.8 9.9 9.10 9.10.1       | Interrupts 8  Poter 9 t Test Action Group Port (JTAG)  Introduction. Features. Block Diagram Functional Description Master TAP Instructions TAP Controller Operation Memory Map. Pin Description JTAG Port Architecture. JTAG Boundary Scan Register Clocks TCK.                        | 9-3<br>9-4<br>9-4<br>9-7<br>9-7<br>9-11<br>9-12<br>9-12         |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.5 9.5.1 9.6 9.7 9.8 9.9 9.10              | Interrupts 8  pter 9 t Test Action Group Port (JTAG)  Introduction. Features. Block Diagram Functional Description Master TAP Instructions TAP Controller Operation Memory Map. Pin Description JTAG Port Architecture. JTAG Boundary Scan Register Clocks. TCK. Interrupts             | 9-3<br>9-4<br>9-4<br>9-4<br>9-7<br>9-8<br>9-11<br>9-12<br>9-12  |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.5 9.5 1 9.6 9.7 9.8 9.9 9.10 9.10.1       | Interrupts                                                                                                                                                                                                                                                                              | 9-3<br>9-4<br>9-4<br>9-7<br>9-7<br>9-11<br>9-12<br>9-12<br>9-13 |

| 8.8<br><b>Chap Join</b> 9.1 9.2 9.3 9.4 9.4.1 9.5 9.5.1 9.6 9.7 9.8 9.9 9.10 9.10.1 | Interrupts                                                                                                                                                                                                                                                                              | 9-3<br>9-4<br>9-4<br>9-7<br>9-7<br>9-11<br>9-12<br>9-12<br>9-13 |

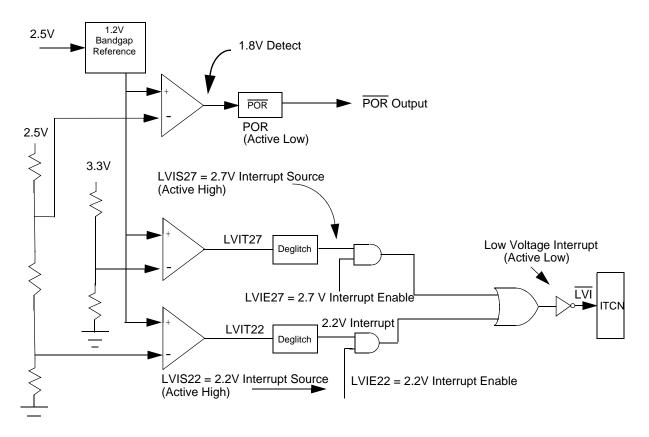

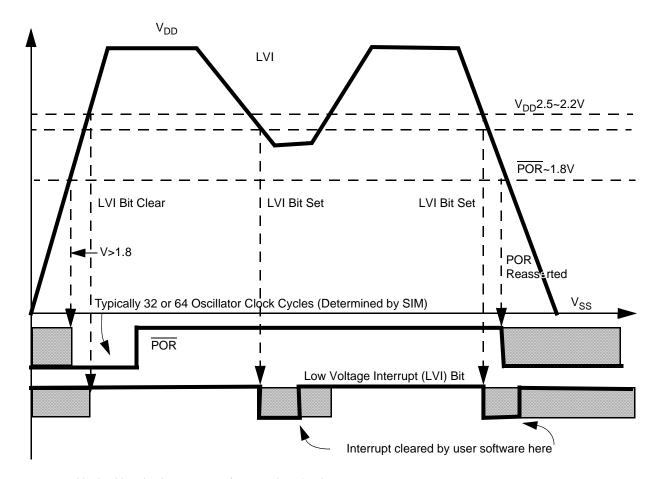

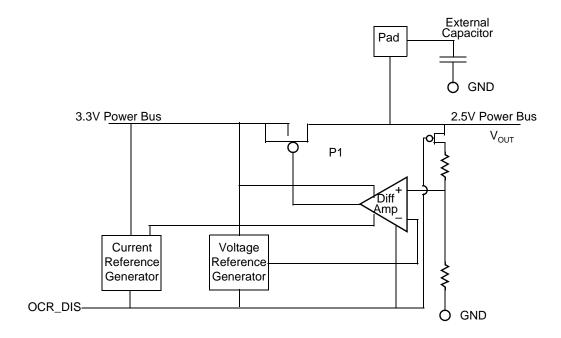

### Chapter 10 Power Supervisor (PS)

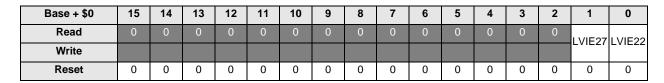

| 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.5.1<br>10.5.2 | Introduction. Features Block Diagram Functional Description Register Definitions Power Supervisor Control Register (LVICTLR) Power Supervisor Status Register (LVISR) | 10-3<br>10-4<br>10-6<br>10-6 |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 10.6                                                     | Suggestions for LVI Interrupt Service Routines                                                                                                                        | 10-8                         |

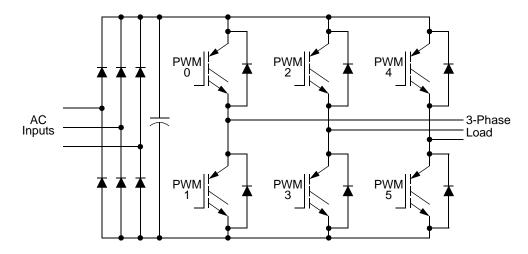

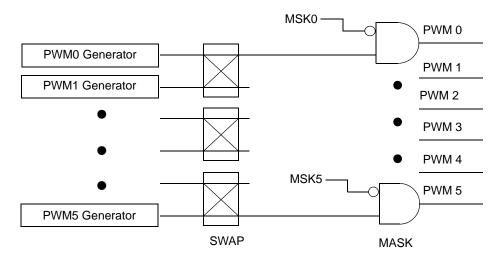

|                                                          | oter 11<br>e Width Modulator (PWM)                                                                                                                                    |                              |

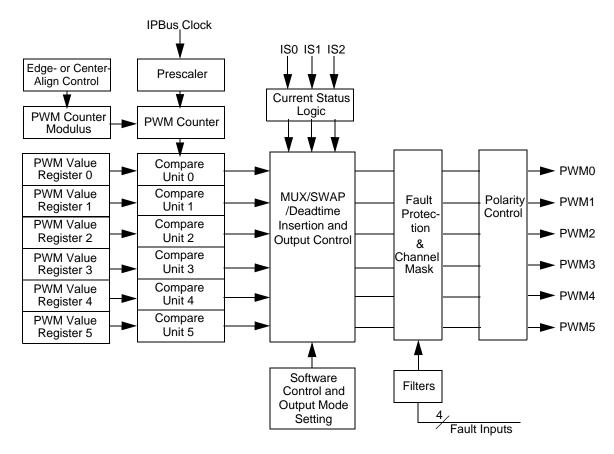

| 11.1                                                     | Introduction                                                                                                                                                          | 11-3                         |

| 11.2                                                     | Features                                                                                                                                                              | 11-3                         |

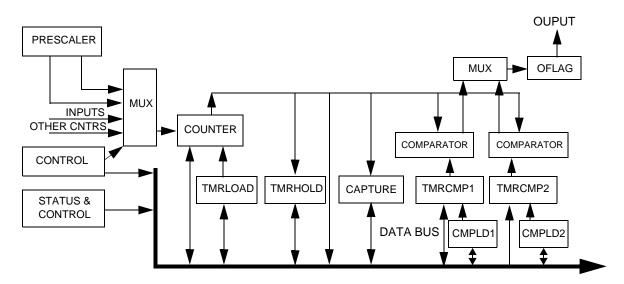

| 11.3                                                     | Block Diagram                                                                                                                                                         | 11-3                         |

| 11.4                                                     | Functional Description                                                                                                                                                |                              |

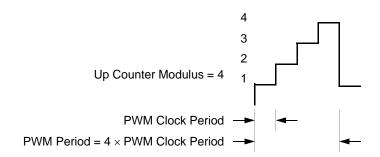

| 11.4.1                                                   | Prescaler                                                                                                                                                             | 11-4                         |

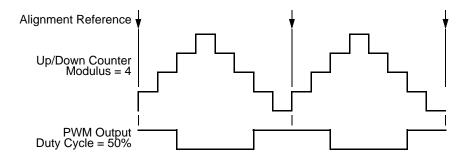

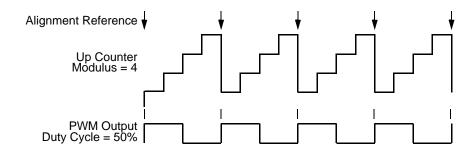

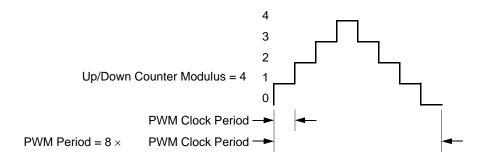

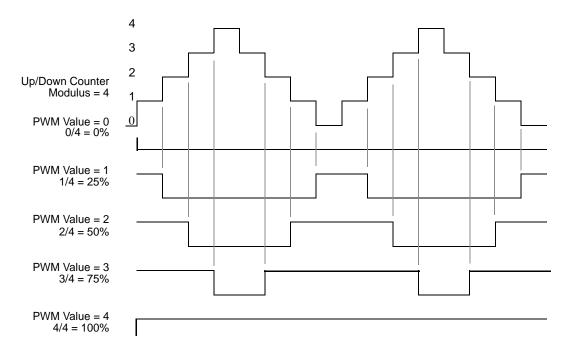

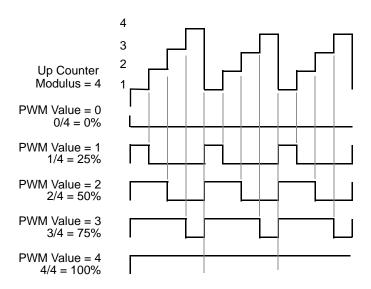

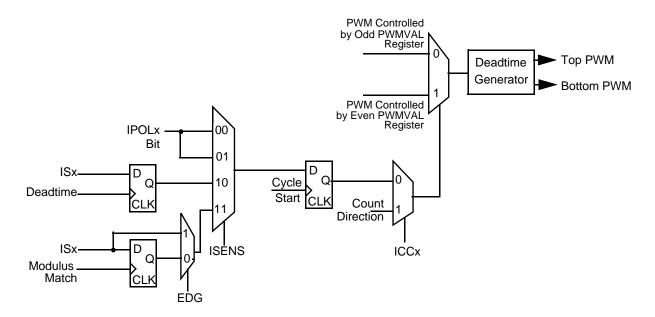

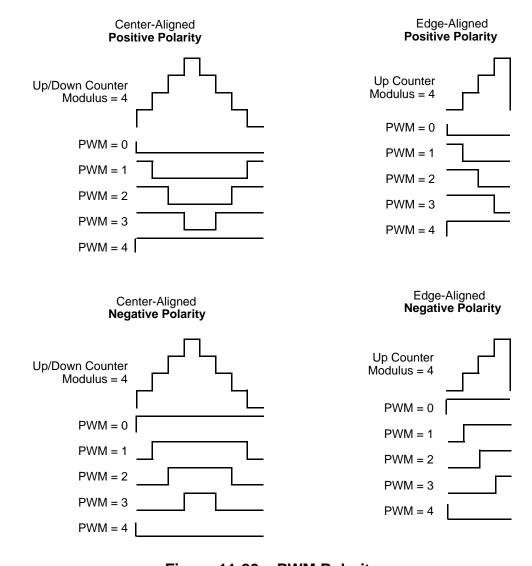

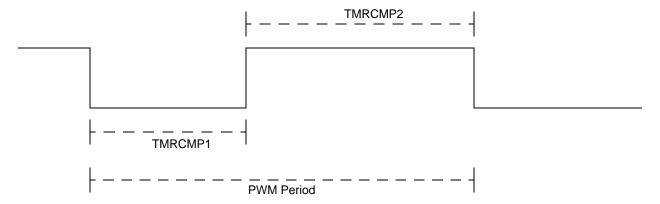

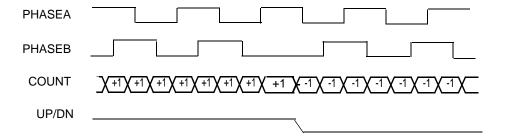

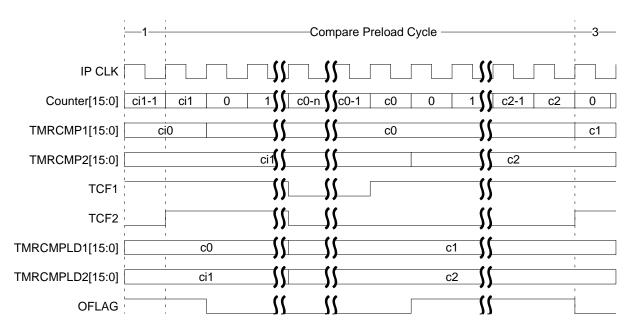

| 11.4.2                                                   | PWM Generator                                                                                                                                                         | 11-4                         |

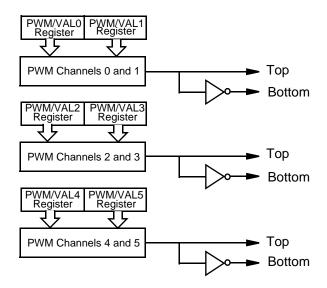

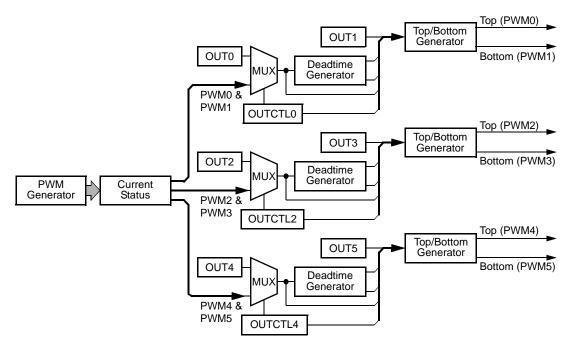

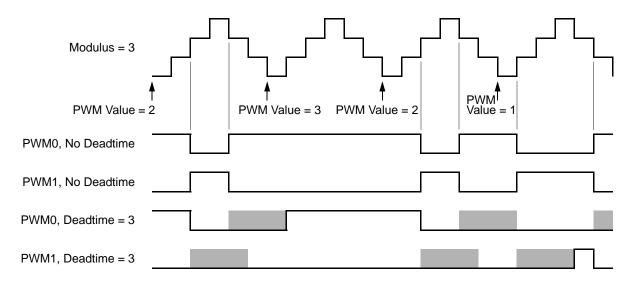

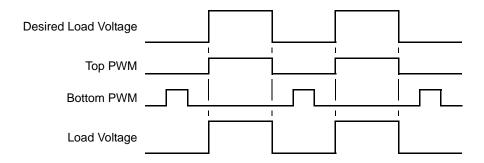

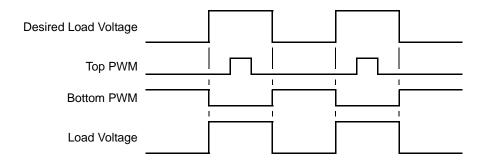

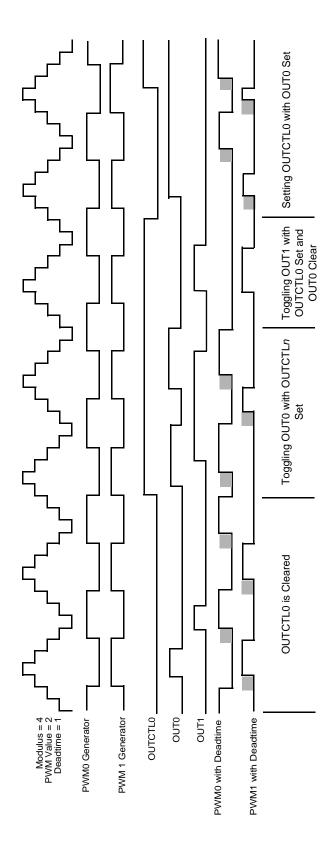

| 11.4.3                                                   | Independent or Complementary Channel Operation                                                                                                                        | 11-8                         |

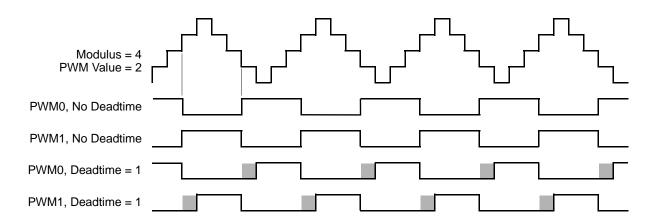

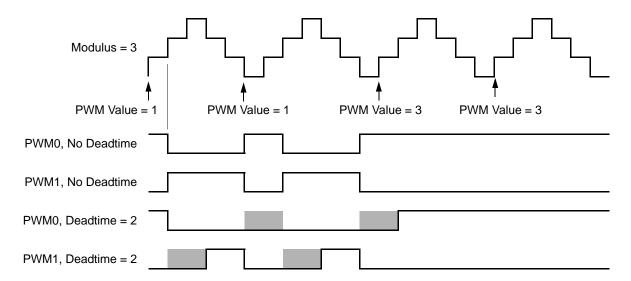

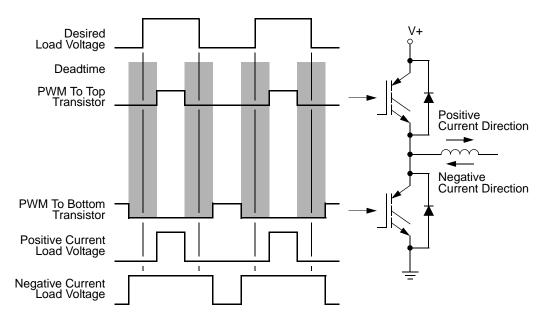

| 11.4.4                                                   | Deadtime Generators                                                                                                                                                   | 11-9                         |

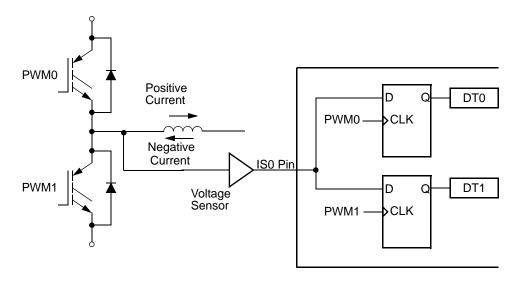

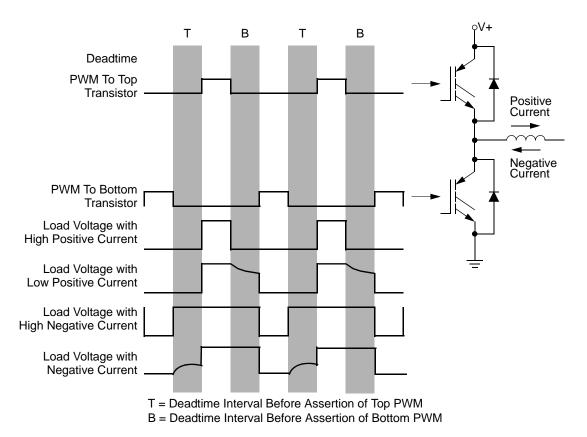

| 11.4.5                                                   | Automatic Deadtime Correction                                                                                                                                         | 1-16                         |

| 11.4.6                                                   | Asymmetric PWM Output                                                                                                                                                 | 1-17                         |

| 11.4.7                                                   | Output Polarity                                                                                                                                                       | 1-18                         |

| 11.5                                                     | Software Output Control1                                                                                                                                              | 1-20                         |

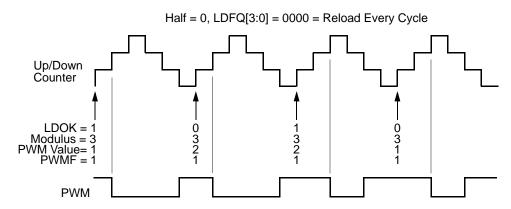

| 11.6                                                     | PWM Generator Loading                                                                                                                                                 | 1-22                         |

| 11.6.1                                                   | Load Enable                                                                                                                                                           | 1-22                         |

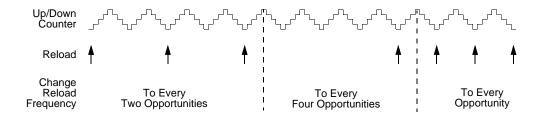

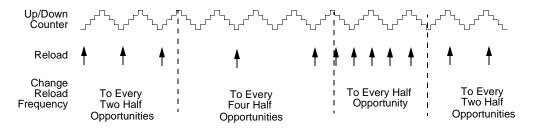

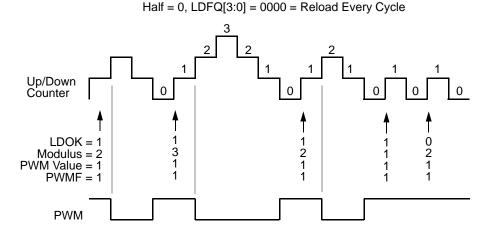

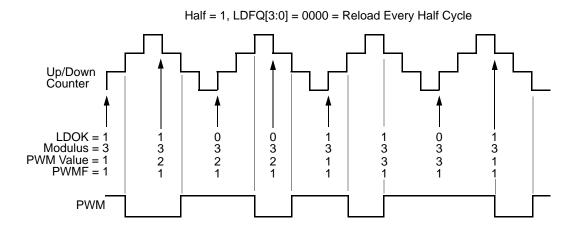

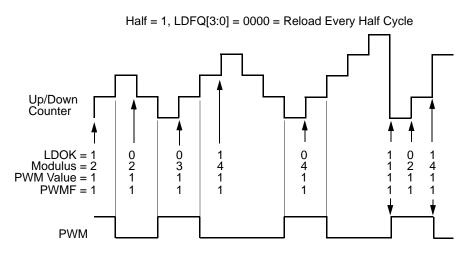

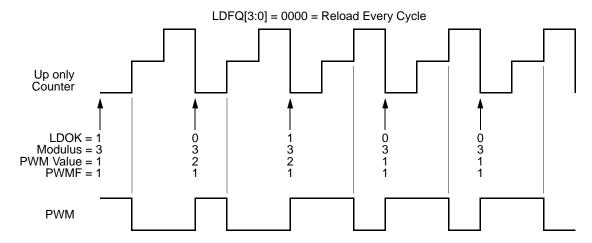

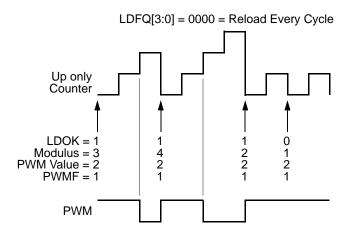

| 11.6.2                                                   | Load Frequency                                                                                                                                                        | 1-22                         |

| 11.6.3                                                   | Reload Flag                                                                                                                                                           | 1-23                         |

| 11.6.4                                                   | Synchronization Output                                                                                                                                                | 1-25                         |

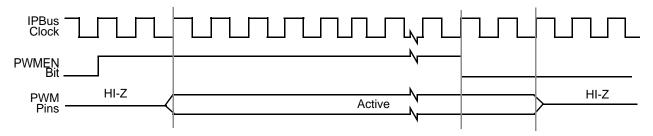

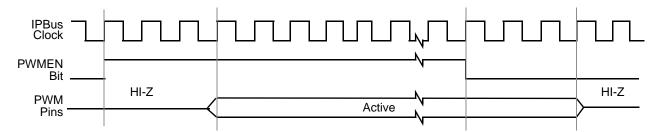

| 11.6.5                                                   | Initialization                                                                                                                                                        | 1-25                         |

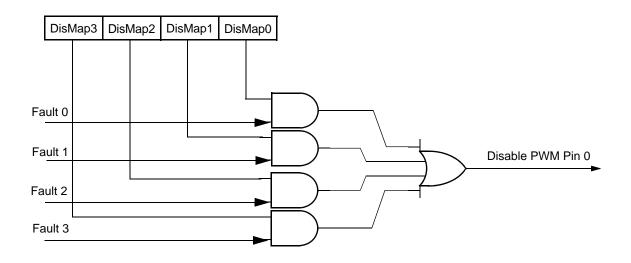

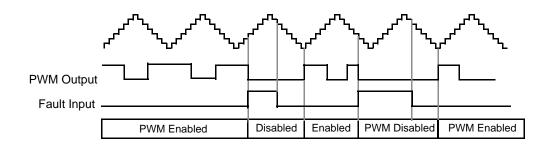

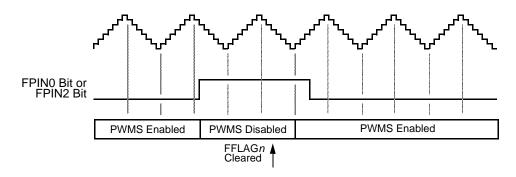

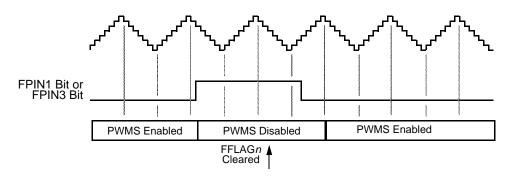

| 11.7                                                     | Fault Protection                                                                                                                                                      | 1-27                         |

| 11.7.1                                                   | Fault Pin Filter                                                                                                                                                      | 1-28                         |

| 11.7.2                                                   | Automatic Fault Clearing                                                                                                                                              | 1-28                         |

| 11.7.3                                                   | Manual Fault Clearing                                                                                                                                                 | 1-28                         |

| 11.8                                                     | Operating Modes                                                                                                                                                       | 1-29                         |

| 11.9                                                     | Pin Descriptions                                                                                                                                                      |                              |

| 11.9.1                                                   | PWM0–PWM5 Pins—(PWM0–5)                                                                                                                                               |                              |

| 11.9.2                                                   |                                                                                                                                                                       |                              |

| 11.9.3                                                   |                                                                                                                                                                       |                              |

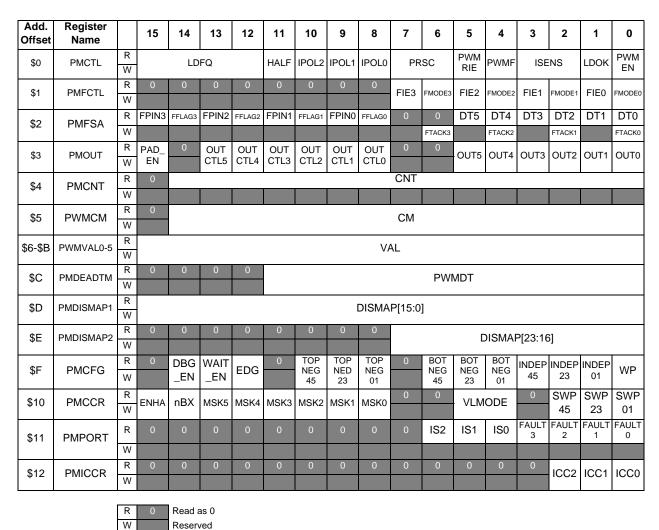

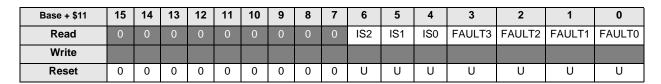

| 11.10.2PWM Fault Control Register (PMFCTL)11-3611.10.3PWM Fault Status and Acknowledge Register (PMFSA)11-3611.10.4PWM Output Control Register (PMOUT)11-3711.10.5PWM Counter Register (PMCNT)11-3911.10.6PWM Counter Modulo Register (PWMCM)11-3911.10.7PWM Value Registers (PWMVAL0-5)11-4011.10.8PWM Deadtime Register (PMDEADTM)11-4011.10.9PWM Disable Mapping Registers (PMDISMAP1-2)11-4111.10.10PWM Configure Register (PMCFG)11-4211.10.11PWM Channel Control Register (PMCCR)11-4411.10.12PWM Port Register (PMPORT)11-4611.10.13PWM Internal Correction Control Register (PMICCR)11-4811.11Clocks11-4811.12Interrupts11-4811.13Resets11-48                                                                                                                                                                                                                                                                                                                                                                                                           | 11.10.2       PWM Fault Control Register (PMFCTL)       11-36         11.10.3       PWM Fault Status and Acknowledge Register (PMFSA)       11-36         11.10.4       PWM Output Control Register (PMOUT)       11-37         11.10.5       PWM Counter Register (PMCNT)       11-39         11.10.6       PWM Counter Modulo Register (PWMCM)       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-48         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.10.3       PWM Fault Status and Acknowledge Register (PMFSA)       11-36         11.10.4       PWM Output Control Register (PMOUT)       11-37         11.10.5       PWM Counter Register (PMCNT)       11-39         11.10.6       PWM Counter Modulo Register (PWMCM)       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-48         11.11       Clocks       11-48         11.12       Interrupts       11-48         11.13       Resets       11-48                                                                                                                                 | 11.10.3       PWM Fault Status and Acknowledge Register (PMFSA)       11-36         11.10.4       PWM Output Control Register (PMOUT)       11-37         11.10.5       PWM Counter Register (PMCNT)       11-39         11.10.6       PWM Counter Modulo Register (PWMCM)       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-48         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                                                                                      |

| 11.10.4       PWM Output Control Register (PMOUT)       11-37         11.10.5       PWM Counter Register (PMCNT)       11-39         11.10.6       PWM Counter Modulo Register (PWMCM)       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48         11.13       Resets       11-48                                                                                                                                                                                                                     | 11.10.4       PWM Output Control Register (PMOUT)       11-37         11.10.5       PWM Counter Register (PMCNT)       11-39         11.10.6       PWM Counter Modulo Register (PWMCM)       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                                                                                                                                                                          |

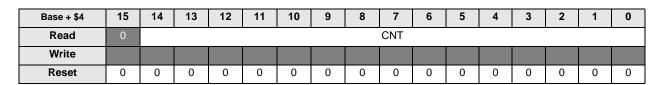

| 11.10.5       PWM Counter Register (PMCNT)       11-39         11.10.6       PWM Counter Modulo Register (PWMCM)       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-48         11.11       Clocks       11-48         11.12       Interrupts       11-48         11.13       Resets       11-48                                                                                                                                                                                                                                                                                           | 11.10.5       PWM Counter Register (PMCNT)       11-39         11.10.6       PWM Counter Modulo Register (PWMCM)       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                                                                                                                                                                                                                                                |

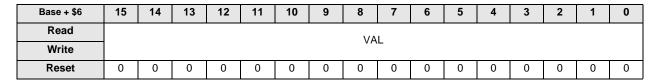

| 11.10.6       PWM Counter Modulo Register (PWMCM).       11-39         11.10.7       PWM Value Registers (PWMVAL0-5).       11-40         11.10.8       PWM Deadtime Register (PMDEADTM).       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2).       11-41         11.10.10       PWM Configure Register (PMCFG).       11-42         11.10.11       PWM Channel Control Register (PMCCR).       11-44         11.10.12       PWM Port Register (PMPORT).       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks.       11-48         11.12       Interrupts       11-48         11.13       Resets       11-48                                                                                                                                                                                                                                                                                                                                                  | 11.10.6       PWM Counter Modulo Register (PWMCM).       11-39         11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM).       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                             |

| 11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-48         11.11       Clocks       11-48         11.12       Interrupts       11-48         11.13       Resets       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                | 11.10.7       PWM Value Registers (PWMVAL0-5)       11-40         11.10.8       PWM Deadtime Register (PMDEADTM)       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                     |

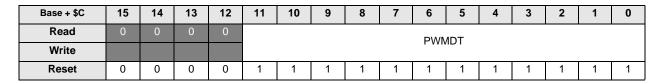

| 11.10.8       PWM Deadtime Register (PMDEADTM).       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2).       11-41         11.10.10       PWM Configure Register (PMCFG).       11-42         11.10.11       PWM Channel Control Register (PMCCR).       11-44         11.10.12       PWM Port Register (PMPORT).       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR).       11-48         11.11       Clocks.       11-48         11.12       Interrupts.       11-48         11.13       Resets.       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11.10.8       PWM Deadtime Register (PMDEADTM).       11-40         11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48         11.13       Resets       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11.10.9       PWM Disable Mapping Registers (PMDISMAP1-2)       11-41         11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

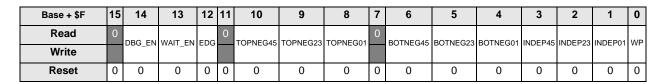

| 11.10.10       PWM Configure Register (PMCFG)       11-42         11.10.11       PWM Channel Control Register (PMCCR)       11-44         11.10.12       PWM Port Register (PMPORT)       11-46         11.10.13       PWM Internal Correction Control Register (PMICCR)       11-46         11.11       Clocks       11-48         11.12       Interrupts       11-48         11.13       Resets       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11.10.10 PWM Configure Register (PMCFG)       11-42         11.10.11 PWM Channel Control Register (PMCCR)       11-44         11.10.12 PWM Port Register (PMPORT)       11-46         11.10.13 PWM Internal Correction Control Register (PMICCR)       11-46         11.11 Clocks       11-48         11.12 Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11.10.11 PWM Channel Control Register (PMCCR)       11-44         11.10.12 PWM Port Register (PMPORT)       11-46         11.10.13 PWM Internal Correction Control Register (PMICCR)       11-46         11.11 Clocks       11-48         11.12 Interrupts       11-48         11.13 Resets       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11.10.11 PWM Channel Control Register (PMCCR)       11-44         11.10.12 PWM Port Register (PMPORT)       11-46         11.10.13 PWM Internal Correction Control Register (PMICCR)       11-46         11.11 Clocks       11-48         11.12 Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.10.12 PWM Port Register (PMPORT).       11-46         11.10.13 PWM Internal Correction Control Register (PMICCR)       11-46         11.11 Clocks.       11-48         11.12 Interrupts       11-48         11.13 Resets       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11.10.12 PWM Port Register (PMPORT).       11-46         11.10.13 PWM Internal Correction Control Register (PMICCR)       11-46         11.11 Clocks.       11-48         11.12 Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11.10.13 PWM Internal Correction Control Register (PMICCR)       11-46         11.11 Clocks       11-48         11.12 Interrupts       11-48         11.13 Resets       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11.10.13 PWM Internal Correction Control Register (PMICCR)       11-46         11.11 Clocks       11-48         11.12 Interrupts       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11.11 Clocks.       11-48         11.12 Interrupts       11-48         11.13 Resets       11-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11.11 Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |