# 240pin Unbuffered DIMM based on 4Gb D-die

78FBGA with Lead-Free & Halogen-Free (RoHS compliant)

# datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

2013 Samsung Electronics Co., Ltd. All rights reserved.

# **Revision History**

| Revision No. | <u>History</u>       | <u>Draft Date</u> | <u>Remark</u> | <u>Editor</u> |

|--------------|----------------------|-------------------|---------------|---------------|

| 1.0          | - First SPEC Release | Aug. 2012         |               | S.H.Kim       |

# Table Of Contents

| 240p | in Unbufl | fered DIN | MM based | on 4Gb D-die |

|------|-----------|-----------|----------|--------------|

| 1. DDR3 Unbuffered DIMM Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2. Key Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4              |

| 3. Address Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4              |

| 4. x64 DIMM Pin Configurations (Front side/Back side)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5              |

| 5. Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6              |

| 6. SPD and Thermal Sensor for ECC UDIMMs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6              |

| 7. Input/Output Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8              |

| 8. Function Block Diagram:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9              |

| 9. Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11             |

| 10. AC & DC Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| 11. AC & DC Input Measurement Levels  11.1 AC & DC Logic Input Levels for Single-ended Signals  11.2 V <sub>REF</sub> Tolerances.  11.3 AC and DC Logic Input Levels for Differential Signals  11.3.1. Differential Signals Definition  11.3.2. Differential Swing Requirement for Clock (CK - CK) and Strobe (DQS - DQS)  11.3.3. Single-ended Requirements for Differential Signals  11.3.4. Differential Input Cross Point Voltage  11.4 Slew Rate Definition for Single Ended Input Signals  11.5 Slew rate definition for Differential Input Signals |                |

| 12. AC & DC Output Measurement Levels  12.1 Single Ended AC and DC Output Levels  12.2 Differential AC and DC Output Levels  12.3 Single-ended Output Slew Rate  12.4 Differential Output Slew Rate                                                                                                                                                                                                                                                                                                                                                       | 19<br>19<br>19 |

| 13. DIMM IDD specification definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21             |

| 14. IDD SPEC Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23             |

| 15. Input/Output Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24             |

| 16. Electrical Characteristics and AC timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25<br>25<br>25 |

| 17. Timing Parameters by Speed Grade 17.1 Jitter Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36             |

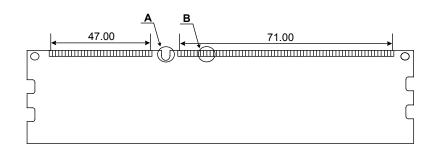

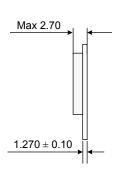

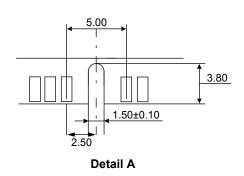

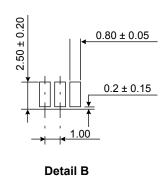

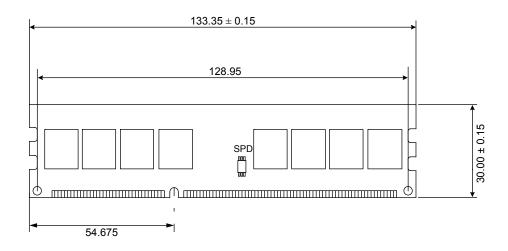

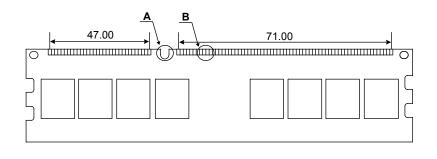

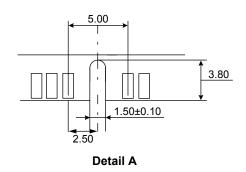

| 18. Physical Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38             |

datasheet

# 1. DDR3 Unbuffered DIMM Ordering Information

| Part Number <sup>2</sup> | Density | Organization | Component Composition <sup>1</sup> | Number of<br>Rank | Height |

|--------------------------|---------|--------------|------------------------------------|-------------------|--------|

| M378B5173DB0-CK0/MA      | 4GB     | 512Mx64      | 512Mx8(K4B4G0846D-BC##)*8          | 1                 | 30mm   |

| M378B1G73DB0-CK0/MA      | 8GB     | 1Gx64        | 512Mx8(K4B4G0846D-BC##)*8          | 2                 | 30mm   |

#### NOTF :

- 1. "##" K0/MA

- 2. K0 1600Mbps 11-11-11 / MA 1866Mbps 13-13-13

- DDR3-1866(13-13-13) is backward compatible to DDR3-1600(11-11-11), DDR3-1333(9-9-9), DDR3-1066(7-7-7)

- DDR3-1600(11-11-11) is backward compatible to DDR3-1333(9-9-9), DDR3-1066(7-7-7)

### 2. Key Features

| Speed       | DDR3-800 | DDR3-1066 | DDR3-1333 | DDR3-1600 | DDR3-1866 | l lait |

|-------------|----------|-----------|-----------|-----------|-----------|--------|

|             | 6-6-6    | 7-7-7     | 9-9-9     | 11-11-11  | 13-13-13  | Unit   |

| tCK(min)    | 2.5      | 1.875     | 1.5       | 1.25      | 1.071     | ns     |

| CAS Latency | 6        | 7         | 9         | 11        | 13        | nCK    |

| tRCD(min)   | 15       | 13.125    | 13.5      | 13.75     | 13.91     | ns     |

| tRP(min)    | 15       | 13.125    | 13.5      | 13.75     | 13.91     | ns     |

| tRAS(min)   | 37.5     | 37.5      | 36        | 35        | 34        | ns     |

| tRC(min)    | 52.5     | 50.625    | 49.5      | 48.75     | 47.91     | ns     |

- JEDEC standard 1.5V ± 0.075V Power Supply

- $V_{DDQ} = 1.5V \pm 0.075V$

- 400MHz  $f_{CK}$  for 800Mb/sec/pin, 533MHz  $f_{CK}$  for 1066Mb/sec/pin, 667MHz  $f_{CK}$  for 1333Mb/sec/pin, 800MHz  $f_{CK}$  for 1600Mb/sec/pin, 933MHz  $f_{CK}$  for 1866Mb/sec/pin

- 8 independent internal bank

- Programmable CAS Latency: 6,7,8,9,10,11,13

- Programmable Additive Latency(Posted CAS): 0, CL 2, or CL 1 clock

- Programmable CAS Write Latency(CWL) = 5 (DDR3-800), 6 (DDR3-1066), 7 (DDR3-1333), 8 (DDR3-1600) and 9 (DDR3-1866)

- Burst Length: 8 (Interleave without any limit, sequential with starting address "000" only), 4 with tCCD = 4 which does not allow seamless read or

write [either On the fly using A12 or MRS]

- Bi-directional Differential Data Strobe

- On Die Termination using ODT pin

- Average Refresh Period 7.8us at lower then T<sub>CASE</sub> 85°C, 3.9us at 85°C < T<sub>CASE</sub> ≤ 95°C

- · Asynchronous Reset

# 3. Address Configuration

| Organization             | Row Address | Row Address Column Address |         | Auto Precharge |  |

|--------------------------|-------------|----------------------------|---------|----------------|--|

| 512Mx8(4Gb) based Module | A0-A15      | A0-A9                      | BA0-BA2 | A10/AP         |  |

# 4. x64 DIMM Pin Configurations (Front side/Back side)

| Pin | Front           | Pin | Back            | Pin | Front                 | Pin | Back                   | Pin | Front           | Pin | Back               |

|-----|-----------------|-----|-----------------|-----|-----------------------|-----|------------------------|-----|-----------------|-----|--------------------|

| 1   | $V_{REFDQ}$     | 121 | V <sub>SS</sub> | 42  | NC                    | 162 | NC                     | 82  | DQ33            | 202 | V <sub>SS</sub>    |

| 2   | V <sub>SS</sub> | 122 | DQ4             | 43  | NC                    | 163 | V <sub>SS</sub>        | 83  | V <sub>SS</sub> | 203 | DM4                |

| 3   | DQ0             | 123 | DQ5             | 44  | V <sub>SS</sub>       | 164 | NC                     | 84  | DQS4            | 204 | NC                 |

| 4   | DQ1             | 124 | V <sub>SS</sub> | 45  | NC                    | 165 | NC                     | 85  | DQS4            | 205 | V <sub>SS</sub>    |

| 5   | V <sub>SS</sub> | 125 | DM0             | 46  | NC                    | 166 | V <sub>SS</sub>        | 86  | V <sub>SS</sub> | 206 | DQ38               |

| 6   | DQS0            | 126 | NC              | 47  | V <sub>SS</sub>       | 167 | NC (TEST) <sup>3</sup> | 87  | DQ34            | 207 | DQ39               |

| 7   | DQS0            | 127 | V <sub>SS</sub> | 48  | NC                    | 168 | Reset                  | 88  | DQ35            | 208 | V <sub>SS</sub>    |

| 8   | V <sub>SS</sub> | 128 | DQ6             |     | KI                    | ΞΥ  | ı                      | 89  | V <sub>SS</sub> | 209 | DQ44               |

| 9   | DQ2             | 129 | DQ7             | 49  | NC                    | 169 | CKE1,NC <sup>1</sup>   | 90  | DQ40            | 210 | DQ45               |

| 10  | DQ3             | 130 | V <sub>SS</sub> | 50  | CKE0                  | 170 | V <sub>DD</sub>        | 91  | DQ41            | 211 | V <sub>SS</sub>    |

| 11  | V <sub>SS</sub> | 131 | DQ12            | 51  | V <sub>DD</sub>       | 171 | A15                    | 92  | V <sub>SS</sub> | 212 | DM5                |

| 12  | DQ8             | 132 | DQ13            | 52  | BA2                   | 172 | A14                    | 93  | DQS5            | 213 | NC                 |

| 13  | DQ9             | 133 | V <sub>SS</sub> | 53  | NC                    | 173 | V <sub>DD</sub>        | 94  | DQS5            | 214 | $V_{SS}$           |

| 14  | V <sub>SS</sub> | 134 | DM1             | 54  | V <sub>DD</sub>       | 174 | A12/BC                 | 95  | V <sub>SS</sub> | 215 | DQ46               |

| 15  | DQS1            | 135 | NC              | 55  | A11                   | 175 | A9                     | 96  | DQ42            | 216 | DQ47               |

| 16  | DQS1            | 136 | V <sub>SS</sub> | 56  | A7                    | 176 | V <sub>DD</sub>        | 97  | DQ43            | 217 | $V_{SS}$           |

| 17  | V <sub>SS</sub> | 137 | DQ14            | 57  | V <sub>DD</sub>       | 177 | A8                     | 98  | V <sub>SS</sub> | 218 | DQ52               |

| 18  | DQ10            | 138 | DQ15            | 58  | A5                    | 178 | A6                     | 99  | DQ48            | 219 | DQ53               |

| 19  | DQ11            | 139 | V <sub>SS</sub> | 59  | A4                    | 179 | V <sub>DD</sub>        | 100 | DQ49            | 220 | V <sub>SS</sub>    |

| 20  | V <sub>SS</sub> | 140 | DQ20            | 60  | V <sub>DD</sub>       | 180 | A3                     | 101 | V <sub>SS</sub> | 221 | DM6                |

| 21  | DQ16            | 141 | DQ21            | 61  | A2                    | 181 | A1                     | 102 | DQS6            | 222 | NC                 |

| 22  | DQ17            | 142 | V <sub>SS</sub> | 62  | V <sub>DD</sub>       | 182 | V <sub>DD</sub>        | 103 | DQS6            | 223 | V <sub>SS</sub>    |

| 23  | V <sub>SS</sub> | 143 | DM2             | 63  | CK1,NC                | 183 | V <sub>DD</sub>        | 104 | V <sub>SS</sub> | 224 | DQ54               |

| 24  | DQS2            | 144 | NC              | 64  | CK1,NC                | 184 | CK0                    | 105 | DQ50            | 225 | DQ55               |

| 25  | DQS2            | 145 | V <sub>SS</sub> | 65  | V <sub>DD</sub>       | 185 | CK0                    | 106 | DQ51            | 226 | V <sub>SS</sub>    |

| 26  | V <sub>SS</sub> | 146 | DQ22            | 66  | V <sub>DD</sub>       | 186 | V <sub>DD</sub>        | 107 | V <sub>SS</sub> | 227 | DQ60               |

| 27  | DQ18            | 147 | DQ23            | 67  | V <sub>REF</sub> CA   | 187 | NC                     | 108 | DQ56            | 228 | DQ61               |

| 28  | DQ19            | 148 | V <sub>SS</sub> | 68  | NC                    | 188 | A0                     | 109 | DQ57            | 229 | $V_{SS}$           |

| 29  | V <sub>SS</sub> | 149 | DQ28            | 69  | V <sub>DD</sub>       | 189 | V <sub>DD</sub>        | 110 | V <sub>SS</sub> | 230 | DM7                |

| 30  | DQ24            | 150 | DQ29            | 70  | A10/AP                | 190 | BA1                    | 111 | DQS7            | 231 | NC                 |

| 31  | DQ25            | 151 | V <sub>SS</sub> | 71  | BA0                   | 191 | V <sub>DD</sub>        | 112 | DQS7            | 232 | V <sub>SS</sub>    |

| 32  | V <sub>SS</sub> | 152 | DM3             | 72  | V <sub>DD</sub>       | 192 | RAS                    | 113 | V <sub>SS</sub> | 233 | DQ62               |

| 33  | DQS3            | 153 | NC              | 73  | WE                    | 193 | <u>\$</u> 0            | 114 | DQ58            | 234 | DQ63               |

| 34  | DQS3            | 154 | V <sub>SS</sub> | 74  | CAS                   | 194 | V <sub>DD</sub>        | 115 | DQ59            | 235 | V <sub>SS</sub>    |

| 35  | V <sub>SS</sub> | 155 | DQ30            | 75  | V <sub>DD</sub>       | 195 | ODT0                   | 116 | V <sub>SS</sub> | 236 | V <sub>DDSPD</sub> |

| 36  | DQ26            | 156 | DQ31            | 76  | ₹1, NC <sup>1</sup>   | 196 | A13                    | 117 | SA0             | 237 | SA1                |

| 37  | DQ27            | 157 | V <sub>SS</sub> | 77  | ODT1, NC <sup>1</sup> | 197 | V <sub>DD</sub>        | 118 | SCL             | 238 | SDA                |

| 38  | V <sub>SS</sub> | 158 | NC              | 78  | $V_{DD}$              | 198 | NC                     | 119 | SA2             | 239 | $V_{SS}$           |

| 39  | NC              | 159 | NC              | 79  | NC                    | 199 | V <sub>SS</sub>        | 120 | V <sub>TT</sub> | 240 | V <sub>TT</sub>    |

| 40  | NC              | 160 | V <sub>SS</sub> | 80  | V <sub>SS</sub>       | 200 | DQ36                   |     |                 |     |                    |

| 41  | V <sub>SS</sub> | 161 | NC              | 81  | DQ32                  | 201 | DQ37                   |     |                 |     |                    |

#### NOTE:

NC = No Connect; NU = Not Used; RFU = Reserved Future Use

- 1. S1, ODT1, CKE1: Used for dual-rank UDIMMs; NC on single-rank UDIMMs

- $2. \ CK1, NC \ and \ \overline{CK1}, NC: Used \ for \ dual-rank \ UDIMMs; \ not \ used \ on \ single-rank \ UDIMMs, \ but \ terminated$

- 3. TEST (pin 167) used by memory bus analysis tools (unused on memory DIMMs)

SAMSUNG ELECTRONICS CO., Ltd. reserves the right to change products and specifications without notice.

# 5. Pin Description

| Pin Name                 | Description                                                          | Pin Name           | Description                                                |

|--------------------------|----------------------------------------------------------------------|--------------------|------------------------------------------------------------|

| A0-A15                   | SDRAM address bus                                                    | SCL                | I <sup>2</sup> C serial bus clock for EEPROM               |

| BA0-BA2                  | SDRAM bank select                                                    | SDA                | I <sup>2</sup> C serial bus data line for EEPROM           |

| RAS                      | SDRAM row address strobe                                             | SA0-SA2            | I <sup>2</sup> C serial address select for EEPROM          |

| CAS                      | SDRAM column address strobe                                          | V <sub>DD</sub> *  | SDRAM core power supply                                    |

| WE                       | SDRAM write enable                                                   | V <sub>DDQ</sub> * | SDRAM I/O Driver power supply                              |

| <u>\$</u> 0, <u>\$</u> 1 | DIMM Rank Select Lines                                               | $V_{REFDQ}$        | SDRAM I/O reference supply                                 |

| CKE0,CKE1                | SDRAM clock enable lines                                             | V <sub>REFCA</sub> | SDRAM command/address reference supply                     |

| ODT0, ODT1               | On-die termination control lines                                     | V <sub>SS</sub>    | Power supply return (ground)                               |

| DQ0 - DQ63               | DIMM memory data bus                                                 | V <sub>DDSPD</sub> | Serial EEPROM positive power supply                        |

| CB0 - CB7                | DIMM ECC check bits                                                  | NC                 | Spare Pins(no connect)                                     |

| DQS0 - DQS8              | SDRAM data strobes (positive line of differential pair)              | TEST               | Used by memory bus analysis tools (unused on memory DIMMs) |

| DQS0-DQS8                | SDRAM differential data strobes (negative line of differential pair) | RESET              | Set DRAMs Known State                                      |

| DM0-DM8                  | SDRAM data masks/high data strobes (x8-based x72 DIMMs)              | EVENT              | Reserved for optional temperature-sensing hardware         |

| CK0, CK1                 | SDRAM clocks (positive line of differential pair)                    | V <sub>TT</sub>    | SDRAM I/O termination supply                               |

| CK0, CK1                 | SDRAM clocks (negative line of differential pair)                    | RFU                | Reserved for future use                                    |

#### NOTE

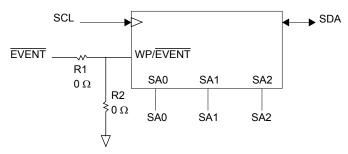

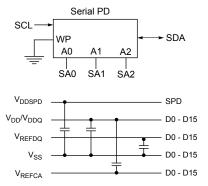

### 6. SPD and Thermal Sensor for ECC UDIMMs

On DIMM thermal sensor will provide DRAM temperature readout through a integrated thermal sensor.

#### NOTE:

- 1. Raw Cards D (1Rx8 ECC) and E (2Rx8 ECC) support a thermal sensor.

- When the SPD and the thermal sensor are placed on the module, R1 is placed but R2 is not. When only the SPD is placed on the module, R2 is placed but R1 is not.

#### [ Table 1 ] Temperature Sensor Characteristics

| Grade      | Range          | Tempe | Units   | NOTE    |         |      |

|------------|----------------|-------|---------|---------|---------|------|

| Grade      |                | Min.  | Тур.    | Max.    | Units   | NOTE |

| В          | 75 < Ta < 95   | -     | +/- 0.5 | +/- 1.0 |         | -    |

|            | 40 < Ta < 125  | -     | +/- 1.0 | +/- 2.0 | °C      | -    |

|            | -20 < Ta < 125 | -     | +/- 2.0 | +/- 3.0 |         | -    |

| Resolution |                | 0.25  |         |         | °C /LSB | -    |

<sup>\*</sup>The  $\mathrm{V}_{\mathrm{DD}}$  and  $\mathrm{V}_{\mathrm{DDQ}}$  pins are tied common to a single power-plane on these designs.

<sup>\*\*</sup> DQS8,  $\overline{DQS}$ 8, DM8 arefor ECC UDIMM only

# 7. Input/Output Functional Description

| Symbol                                        | Type   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK0-CK1<br>CK0-CK1                            | SSTL   | CK and $\overline{\text{CK}}$ are differential clock inputs. All the DDR3 SDRAM addr/cntl inputs are sampled on the crossing of positive edge of CK and negative edge of $\overline{\text{CK}}$ . Output (read) data is reference to the crossing of CK and $\overline{\text{CK}}$ (Both directions of crossing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CKE0-CKE1                                     | SSTL   | Activates the SDRAM CK signal when high and deactivates the CK signal when low. By deactivating the clocks, CKE low initiates the Power Down mode, or the Self-Refresh mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| \$0-\$1                                       | SSTL   | Enables the associated SDRAM command decoder when low and disables the command decoder when high. When the command decoder is disabled, new command are ignored but previous operations continue. This signal provides for external rank selection on systems with multiple ranks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RAS, CAS, WE                                  | SSTL   | RAS, CAS, and WE (ALONG WITH S) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ODT0-ODT1                                     | SSTL   | When high, termination resistance is enabled for all DQ, DQS, $\overline{DQS}$ and DM pins, assuming the function is enabled in the Extended Mode Register Set (EMRS).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $V_{REFDQ}$                                   | Supply | Reference voltage for SSTL 15 I/O inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>REFCA</sub>                            | Supply | Reference voltage for SSTL 15 command/address inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DDQ</sub>                              | Supply | Power supply for the DDR3 SDRAM output buffers to provide improved noise immunity. For all current DDR3 unbuffered DIMM designs, V <sub>DDQ</sub> shares the same power plane as V <sub>DD</sub> pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BA0-BA2                                       | SSTL   | Selects which SDRAM bank of eight is activated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A0-A15                                        | SSTL   | During a Bank Activate command cycle, Address input defines the row address (RA0-RA13)  During a Read or Write command cycle, Address input defines the column address, In addition to the column address, AP is used to invoke autoprecharge operation at the end of the burst read or write cycle. If AP is high, autoprecharge is selected and BA0, BA1, BA2 defines the bank to be precharged. If AP is low, autoprecharge is disabled. During a precharge command cycle, AP is used in conjunction with BA0, BA1, BA2 to control which bank(s) to precharge. If AP is high, all banks will be precharged regardless of the state of BA0, BA1 or BA2. If AP is low, BA0, BA1 and BA2 are used to define which bank to precharge. A12(BC) is sampled during READ and WRITE commands to determine if burst chop (on-the-fly) will be performed (HIGH, no burst chop; Low, burst chopped). |

| DQ0-DQ63<br>CB0-CB7                           | SSTL   | Data and Check Bit Input/Output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DM0-DM8 <sup>1</sup>                          | SSTL   | DM is an input mask signal for write data. Input data is masked when DM is sampled High coincident with that input data during a write access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>DD</sub> ,V <sub>SS</sub>              | Supply | Power and ground for DDR3 SDRAM input buffers, and core logic. V <sub>DD</sub> and V <sub>DDQ</sub> pins are tied to V <sub>DD</sub> /V <sub>DDQ</sub> planes on these modules.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQS0-DQS8 <sup>1</sup> DQS0-DQS8 <sup>1</sup> | SSTL   | Data strobe for input and output data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SA0-SA2                                       | -      | These signals and tied at the system planar to either V <sub>SS</sub> or V <sub>DDSPD</sub> to configure the serial SPD EERPOM address range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SDA                                           | -      | This bidirectional pin is used to transfer data into or out of the SPD EEPROM. An external resistor may be connected from the SDA bus line to V <sub>DDSPD</sub> to act as a pull-up on the system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCL                                           | -      | This signal is used to clock data into and out of the SPD EEPROM. An external resistor may be connected from the SCL bus time to V <sub>DDSPD</sub> to act as a pull-up on the system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>DDSPD</sub>                            | Supply | Power supply for SPD EEPROM. This supply is separate from the $V_{DD}/V_{DDQ}$ power plane. EEPROM supply is operable from 3.0V to 3.6V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET                                         | -      | The RESET pin is connected to the RESET pin on each DRAM. When low, all DRAMs are set to a know state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EVENT                                         | Output | This signal indicates that a thermal event has been detected in the thermal sensing device. The system should guarantee the electrical level requirement is met for the EVENT pin on TS/SPD part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### NOTE

1. DM8, DQS8 and  $\overline{\rm DQS}8$  are for ECC UDIMM only

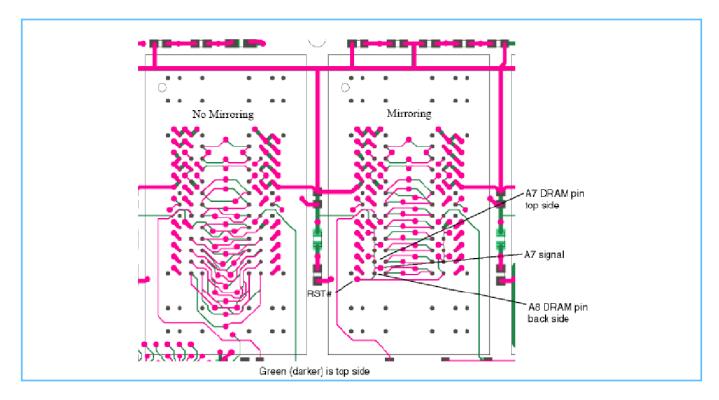

### 7.1 Address Mirroring Feature

There is a via grid located under the DRAMs for wiring the CA signals (address, bank address, command, and control lines) to the DRAM pins. The length of the traces from the vias to the DRAMs places limitations on the bandwidth of the module. The shorter these traces, the higher the bandwidth. To extend the bandwidth of the CA bus for DDR3 modules, a scheme was defined to reduce the length of these traces.

The pins on the DRAM are defined in a manner that allows for these short trace lengths. The CA bus pins in Columns 2 and 8, ignoring the mechanical support pins, do not have any special functions (secondary functions). This allows the most flexibility with these pins. These are address pins A3, A4, A5, A6, A7, A8 and bank address pins BA0 and BA1. Refer to Table . Rank 0 DRAM pins are wired straight, with no mismatch between the connector pin assignment and the DRAM pin assignment. Some of the Rank 1 DRAM pins are cross wired as defined in the table. Pins not listed in the table are wired straight.

#### 7.1.1 DRAM Pin Wiring Mirroring

| Connector Pin | DRAM Pin |        |  |  |  |

|---------------|----------|--------|--|--|--|

| Connector Fin | Rank 0   | Rank 1 |  |  |  |

| A3            | A3       | A4     |  |  |  |

| A4            | A4       | A3     |  |  |  |

| A5            | A5       | A6     |  |  |  |

| A6            | A6       | A5     |  |  |  |

| A7            | A7       | A8     |  |  |  |

| A8            | A8       | A7     |  |  |  |

| BA0           | BA0      | BA1    |  |  |  |

| BA1           | BA1      | BA0    |  |  |  |

Figure 1illustrates the wiring in both the mirrored and non-mirrored case. The lengths of the traces to the DRAM pins, is obviously shorter. The via grid is smaller as well.

Figure 1. Wiring Differences for Mirrored and Non-Mirrored Addresses

Since the cross-wired pins have no secondary functions, there is no problem in normal operation. Any data written is read the same way. There are limitations however. When writing to the internal registers with a "load mode" operation, the specific address is required. See the DDR3 UDIMM SPD specification for these details. The controller must read the SPD and have the capability of de-mirroring the address when accessing the second rank. SAMSUNG DDR3 dual rank UDIMM R/C B(2Rx8) and R/C E(2Rx8) Modules are using Mirrored Addresses mode.

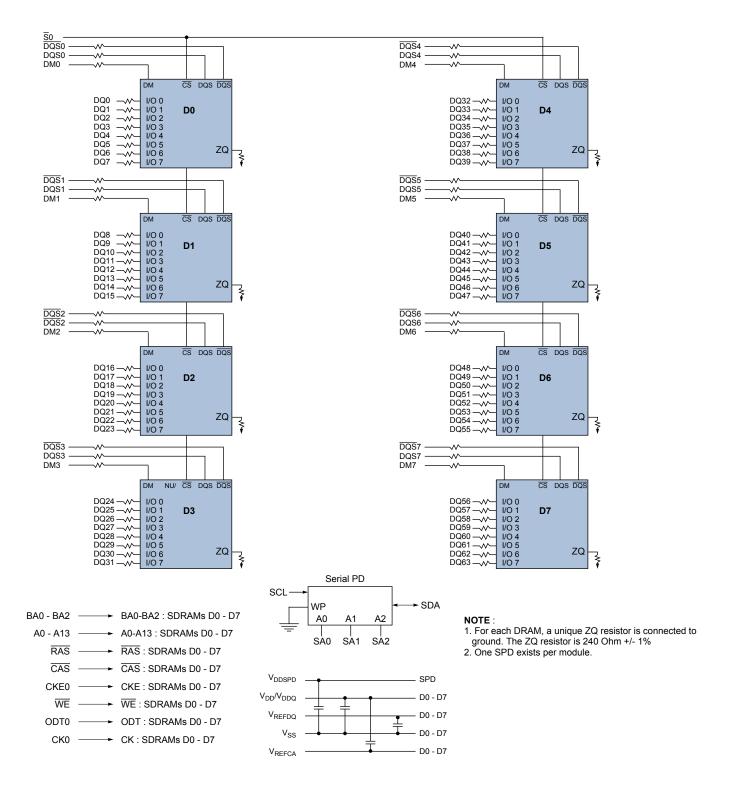

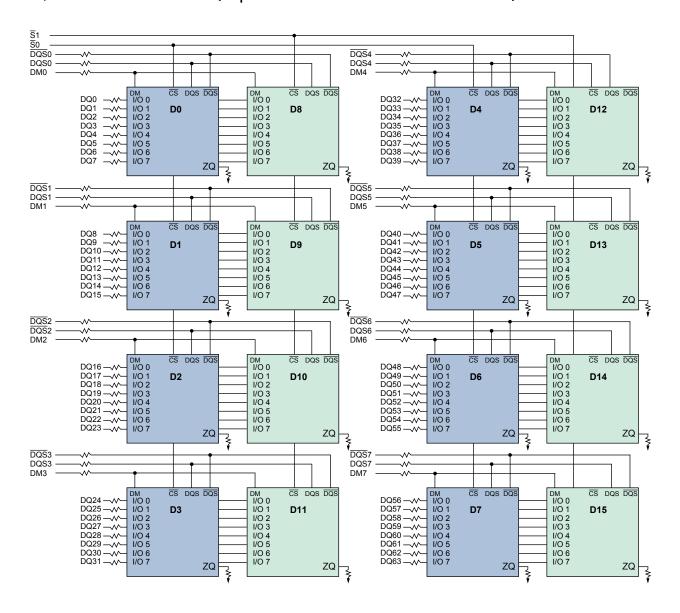

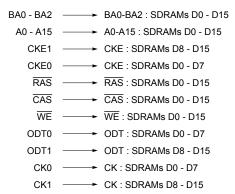

# 8. Function Block Diagram:

### 8.1 4GB, 512Mx64 Non ECC Module (Populated as 1 rank of x8 DDR3 SDRAMs)

### 8.2 8GB, 1Gx64 Non ECC Module (Populated as 2 ranks of x8 DDR3 SDRAMs)

#### NOTE:

- For each DRAM, a unique ZQ resistor is connected to ground. The ZQ resistor is 240 Ohm +/- 1%

- 2. One SPD exists per module.

# 9. Absolute Maximum Ratings

### 9.1 Absolute Maximum DC Ratings

| Symbol                            | Parameter                                      | Rating          | Units | NOTE |

|-----------------------------------|------------------------------------------------|-----------------|-------|------|

| V <sub>DD</sub>                   | Voltage on $V_{DD}$ pin relative to $V_{SS}$   | -0.4 V ~ 1.80 V | V     | 1,3  |

| $V_{\mathrm{DDQ}}$                | Voltage on $V_{DDQ}$ pin relative to $V_{SS}$  | -0.4 V ~ 1.80 V | V     | 1,3  |

| V <sub>IN,</sub> V <sub>OUT</sub> | Voltage on any pin relative to V <sub>SS</sub> | -0.4 V ~ 1.80 V | V     | 1    |

| T <sub>STG</sub>                  | Storage Temperature                            | -55 to +100     | °C    | 1, 2 |

#### NOTE:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 3. V<sub>DD</sub> and V<sub>DDQ</sub> must be within 300mV of each other at all times; and V<sub>REF</sub> must be not greater than 0.6 x V<sub>DDQ</sub>, When V<sub>DD</sub> and V<sub>DDQ</sub> are less than 500mV; V<sub>REF</sub> may be equal to or less than 300mV.

### 9.2 DRAM Component Operating Temperature Range

| Symbol            | Parameter                   | rating  | Unit | NOTE    |

|-------------------|-----------------------------|---------|------|---------|

| T <sub>OPER</sub> | Operating Temperature Range | 0 to 95 | °C   | 1, 2, 3 |

#### NOTE:

- 1. Operating Temperature T<sub>OPER</sub> is the case surface temperature on the center/top side of the DRAM. For measurement conditions, please refer to the JEDEC document JESD51-2.

- The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0-85°C under all operating conditions

- Some applications require operation of the Extended Temperature Range between 85°C and 95°C case temperature. Full specifications are guaranteed in this range, but the

following additional conditions apply:

- a) Refresh commands must be doubled in frequency, therefore reducing the refresh interval tREFI to 3.9us.

- b) If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to either use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 A6 = 0b and MR2 A7 = 1b), in this case IDD6 current can be increased around 10~20% than normal Temperature range.

# 10. AC & DC Operating Conditions

## 10.1 Recommended DC Operating Conditions (SSTL-15)

| Symbol    | Parameter                 |       | Units | NOTE  |        |      |

|-----------|---------------------------|-------|-------|-------|--------|------|

| Symbol    | Symbol Parameter          |       | Тур.  | Max.  | Uiilis | NOTE |

| $V_{DD}$  | Supply Voltage            | 1.425 | 1.5   | 1.575 | V      | 1,2  |

| $V_{DDQ}$ | Supply Voltage for Output | 1.425 | 1.5   | 1.575 | V      | 1,2  |

#### NOTE

- 1. Under all conditions  $V_{\mbox{\scriptsize DDQ}}$  must be less than or equal to  $V_{\mbox{\scriptsize DD}}.$

- 2.  $V_{DDQ}$  tracks with  $V_{DD}$ . AC parameters are measured with  $V_{DD}$  and  $V_{DDQ}$  tied together.

# 11. AC & DC Input Measurement Levels

### 11.1 AC & DC Logic Input Levels for Single-ended Signals

[ Table 2 ] Single-ended AC & DC input levels for Command and Address

| Symbol                     | Parameter                             | DDR3-800/10            | 066/1333/1600          | DDR3                   | 3-1866                 | Unit   | NOTE  |

|----------------------------|---------------------------------------|------------------------|------------------------|------------------------|------------------------|--------|-------|

| Symbol                     | Parameter                             | Min.                   | Max.                   | Min.                   | Max.                   | - Onit | NOTE  |

| V <sub>IH.CA</sub> (DC100) | DC input logic high                   | V <sub>REF</sub> + 100 | V <sub>DD</sub>        | V <sub>REF</sub> + 100 | V <sub>DD</sub>        | mV     | 1,5   |

| V <sub>IL.CA</sub> (DC100) | DC input logic low                    | V <sub>SS</sub>        | V <sub>REF</sub> - 100 | V <sub>SS</sub>        | V <sub>REF</sub> - 100 | mV     | 1,6   |

| V <sub>IH.CA</sub> (AC175) | AC input logic high                   | V <sub>REF</sub> + 175 | Note 2                 | -                      | -                      | mV     | 1,2,7 |

| V <sub>IL.CA</sub> (AC175) | AC input logic low                    | Note 2                 | V <sub>REF</sub> - 175 | -                      | -                      | mV     | 1,2,8 |

| V <sub>IH.CA</sub> (AC150) | AC input logic high                   | V <sub>REF</sub> +150  | Note 2                 | -                      | -                      | mV     | 1,2,7 |

| V <sub>IL.CA</sub> (AC150) | AC input logic low                    | Note 2                 | V <sub>REF</sub> -150  | -                      | -                      | mV     | 1,2,8 |

| V <sub>IH.CA</sub> (AC135) | AC input logic high                   | -                      | -                      | V <sub>REF</sub> + 135 | Note 2                 | mV     | 1,2,7 |

| V <sub>IL.CA</sub> (AC135) | AC input logic low                    | -                      | -                      | Note 2                 | V <sub>REF</sub> - 135 | mV     | 1,2,8 |

| V <sub>IH.CA</sub> (AC125) | AC input logic high                   | -                      | -                      | V <sub>REF</sub> +125  | Note 2                 | mV     | 1,2,7 |

| V <sub>IL.CA</sub> (AC125) | AC input logic low                    | -                      | -                      | Note 2                 | V <sub>REF</sub> -125  | mV     | 1,2,8 |

| V <sub>REFCA</sub> (DC)    | Reference Voltage for ADD, CMD inputs | 0.49*V <sub>DD</sub>   | 0.51*V <sub>DD</sub>   | 0.49*V <sub>DD</sub>   | 0.51*V <sub>DD</sub>   | V      | 3,4,9 |

#### NOTE

- 1. For input only pins except  $\overline{\text{RESET}}$ ,  $V_{\text{REF}} = V_{\text{REFCA}}(DC)$

- 2. See 'Overshoot/Undershoot Specification' on Component Datasheet.

- 3. The AC peak noise on  $V_{REF}$  may not allow  $V_{REF}$  to deviate from  $V_{REF}(DC)$  by more than  $\pm$  1%  $V_{DD}$  (for reference : approx.  $\pm$  15mV)

- 4. For reference : approx.  $V_{DD}/2 \pm 15 mV$

- 5.  $V_{IH}(dc)$  is used as a simplified symbol for  $V_{IH.CA}(DC100)$

- 6. V<sub>IL</sub>(dc) is used as a simplified symbol for V<sub>IL.CA</sub>(DC100)

- 7. V<sub>IH</sub>(ac) is used as a simplified symbol for V<sub>IH.CA</sub>(AC155), V<sub>IH.CA</sub>(AC150), V<sub>IH.CA</sub>(AC135) and V<sub>IH.CA</sub>(AC125); V<sub>IH.CA</sub>(AC175) value is used when V<sub>REF</sub> + 175mV is referenced , V<sub>IH.CA</sub>(AC150) value is used when VREF + 150mV is referenced, V<sub>IH.CA</sub>(AC135) value is used when VREF + 135mV is referenced and V<sub>IH.CA</sub>(AC125) value is used when VREF + 125mV is referenced.

- 8. V<sub>IL</sub>(ac) is used as a simplified symbol for V<sub>IL.CA</sub>(AC175) and V<sub>IL.CA</sub>(AC150), V<sub>IL.CA</sub>(AC135) and V<sub>IL.CA</sub>(AC125); V<sub>IL.CA</sub>(AC175) value is used when V<sub>REF</sub> 175mV is referenced, V<sub>IL.CA</sub>(AC150) value is used when V<sub>REF</sub> 135mV is referenced and V<sub>IL.CA</sub>(AC125) value is used when V<sub>REF</sub> 125mV is referenced.

- 9. VrefCA(DC) is measured relative to VDD at the same point in time on the same device

#### [ Table 3 ] Single-ended AC & DC input levels for DQ and DM

| Symbol                     | Doromotor                              | DDR3-8                 | 00/1066                | DDR3-13                | 33/1600                | DDR3                   | -1866                  | Unit | NOTE     |

|----------------------------|----------------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------|----------|

| Symbol                     | Parameter                              | Min.                   | Max.                   | Min.                   | Max.                   | Min.                   | Max.                   | Unit | NOTE     |

| V <sub>IH.DQ</sub> (DC100) | DC input logic high                    | V <sub>REF</sub> + 100 | $V_{DD}$               | V <sub>REF</sub> + 100 | $V_{DD}$               | V <sub>REF</sub> + 100 | $V_{DD}$               | mV   | 1,5      |

| V <sub>IL.DQ</sub> (DC100) | DC input logic low                     | V <sub>SS</sub>        | V <sub>REF</sub> - 100 | V <sub>SS</sub>        | V <sub>REF</sub> - 100 | V <sub>SS</sub>        | V <sub>REF</sub> - 100 | mV   | 1,6      |

| V <sub>IH.DQ</sub> (AC175) | AC input logic high                    | V <sub>REF</sub> + 175 | NOTE 2                 | -                      | -                      | -                      | -                      | mV   | 1,2,7    |

| V <sub>IL.DQ</sub> (AC175) | AC input logic low                     | NOTE 2                 | V <sub>REF</sub> - 175 | -                      | -                      | -                      | -                      | mV   | 1,2,8    |

| V <sub>IH.DQ</sub> (AC150) | AC input logic high                    | V <sub>REF</sub> + 150 | NOTE 2                 | V <sub>REF</sub> + 150 | NOTE 2                 | -                      | -                      | mV   | 1,2,7    |

| V <sub>IL.DQ</sub> (AC150) | AC input logic low                     | NOTE 2                 | V <sub>REF</sub> - 150 | NOTE 2                 | V <sub>REF</sub> - 150 | -                      | -                      | mV   | 1,2,8    |

| V <sub>IH.DQ</sub> (AC135) | AC input logic high                    | V <sub>REF</sub> + 135 | NOTE 2                 | V <sub>REF</sub> + 135 | NOTE 2                 | V <sub>REF</sub> + 135 | NOTE 2                 | mV   | 1,2,7,10 |

| V <sub>IL.DQ</sub> (AC135) | AC input logic low                     | NOTE 2                 | V <sub>REF</sub> - 135 | NOTE 2                 | V <sub>REF</sub> - 135 | NOTE 2                 | V <sub>REF</sub> - 135 | mV   | 1,2,8,10 |

| V <sub>REFDQ</sub> (DC)    | Reference Voltage for DQ,<br>DM inputs | 0.49*V <sub>DD</sub>   | 0.51*V <sub>DD</sub>   | 0.49*V <sub>DD</sub>   | 0.51*V <sub>DD</sub>   | 0.49*V <sub>DD</sub>   | 0.51*V <sub>DD</sub>   | V    | 3,4,9    |

#### NOTE:

- 1. For input only pins except  $\overline{RESET}$ ,  $V_{REF} = V_{REFDO}(DC)$

- 2. See 'Overshoot/Undershoot Specification' on Component Datasheet.

- 3. The AC peak noise on V<sub>REF</sub> may not allow V<sub>REF</sub> to deviate from V<sub>REF</sub>(DC) by more than ± 1% V<sub>DD</sub> (for reference : approx. ± 15mV)

- 4. For reference : approx.  $V_{DD}/2 \pm 15 \text{mV}$

- 5.  $V_{IH}(dc)$  is used as a simplified symbol for  $V_{IH,DQ}(DC100)$

- 5. V<sub>IH,DQ</sub>(Is used as a simplified symbol for V<sub>IH,DQ</sub>(DC100)

6. V<sub>IL</sub>(dc) is used as a simplified symbol for V<sub>IL,DQ</sub>(DC100)

7. V<sub>IH</sub>(ac) is used as a simplified symbol for V<sub>IH,DQ</sub>(AC175), V<sub>IH,DQ</sub>(AC150) and V<sub>IH,DQ</sub>(AC135); V<sub>IH,DQ</sub>(AC175) value is used when V<sub>REF</sub> + 175mV is referenced, V<sub>IH,DQ</sub>(AC150) value is used when V<sub>REF</sub> + 150mV is referenced.

8. V<sub>IL</sub>(ac) is used as a simplified symbol for V<sub>IL,DQ</sub>(AC175), V<sub>IL,DQ</sub>(AC150); V<sub>IL,DQ</sub>(AC175) value is used when V<sub>REF</sub> 175mV is referenced, V<sub>IL,DQ</sub>(AC150) value is used when

- V<sub>REF</sub> 150mV is referenced.

- 9. VrefCA(DC) is measured relative to VDD at the same point in time on the same device

- 10. Optional in DDR3 SDRAM for DDR3-800/1066/1333/1600: Users should refer to the DRAM supplier data sheetand/or the DIMM SPDto determine if DDR3 SDRAM devices support this option.

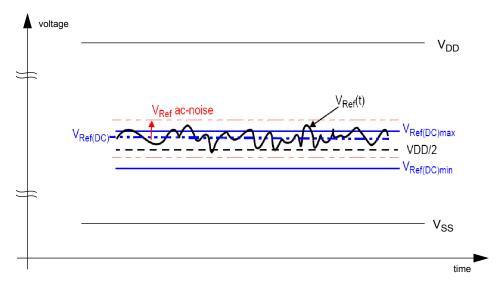

### 11.2 V<sub>RFF</sub> Tolerances.

The dc-tolerance limits and ac-noise limits for the reference voltages  $V_{REFCA}$  and  $V_{REFDQ}$  are illustrate in Figure 2. It shows a valid reference voltage  $V_{REF}(t)$  as a function of time. ( $V_{REF}$  stands for  $V_{REFCA}$  and  $V_{REFDQ}$  likewise).

$V_{REF}(DC)$  is the linear average of  $V_{REF}(t)$  over a very long period of time (e.g. 1 sec). This average has to meet the min/max requirements of  $V_{REF}$ . Furthermore  $V_{REF}(t)$  may temporarily deviate from  $V_{REF}(DC)$  by no more than  $\pm$  1%  $V_{DD}$ .

Figure 2. Illustration of VREF(DC) tolerance and VREF ac-noise limits

The voltage levels for setup and hold time measurements  $V_{IH}(AC)$ ,  $V_{IH}(DC)$ ,  $V_{IL}(AC)$  and  $V_{IL}(DC)$  are dependent on  $V_{REF}$ .

" $V_{REF}$ " shall be understood as  $V_{REF}(DC)$ , as defined in Figure 2.

This clarifies, that dc-variations of  $V_{REF}$  affect the absolute voltage a signal has to reach to achieve a valid high or low level and therefore the time to which setup and hold is measured. System timing and voltage budgets need to account for  $V_{REF}(DC)$  deviations from the optimum position within the data-eye of the input signals.

This also clarifies that the DRAM setup/hold specification and derating values need to include time and voltage associated with  $V_{REF}$  ac-noise. Timing and voltage effects due to ac-noise on  $V_{REF}$  up to the specified limit (+/-1% of  $V_{DD}$ ) are included in DRAM timings and their associated deratings.

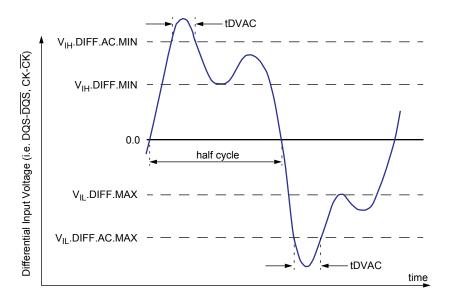

### 11.3 AC and DC Logic Input Levels for Differential Signals

#### 11.3.1 Differential Signals Definition

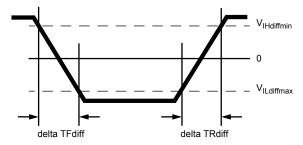

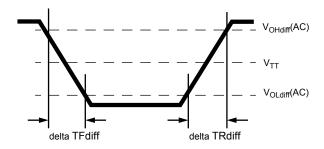

Figure 3. Definition of differential ac-swing and "time above ac level" tDVAC

#### 11.3.2 Differential Swing Requirement for Clock (CK - CK) and Strobe (DQS - DQS)

| Symbol                   | Parameter                  | DDR3-800/1066/1333/1600/1866                   |                                                | unit | NOTE |

|--------------------------|----------------------------|------------------------------------------------|------------------------------------------------|------|------|

| Symbol                   | raiailletei                | min                                            | max                                            | unit | NOTE |

| $V_{IHdiff}$             | differential input high    | +0.2                                           | NOTE 3                                         | V    | 1    |

| V <sub>ILdiff</sub>      | differential input low     | NOTE 3                                         | -0.2                                           | V    | 1    |

| V <sub>IHdiff</sub> (AC) | differential input high ac | 2 x (V <sub>IH</sub> (AC) - V <sub>REF</sub> ) | NOTE 3                                         | V    | 2    |

| V <sub>ILdiff</sub> (AC) | differential input low ac  | NOTE 3                                         | 2 x (V <sub>IL</sub> (AC) - V <sub>REF</sub> ) | V    | 2    |

#### NOTE

- 1. Used to define a differential signal slew-rate.

2. for CK CK use V<sub>IH</sub>/V<sub>IL</sub>(AC) of ADD/CMD and V<sub>REFCA</sub>; for DQS DQS use V<sub>IH</sub>/V<sub>IL</sub>(AC) of DQs and V<sub>REFDQ</sub>; if a reduced ac-high or ac-low level is used for a signal group, then the reduced level applies also here.

- 3. These values are not defined, however they single-ended signals CK,  $\overline{CK}$ , DQS,  $\overline{DQS}$ , DQSL need to be within the respective limits ( $V_{IH}(DC)$  max,  $V_{IL}(DC)$ min) for single-ended signals CK,  $\overline{CK}$ , DQS,  $\overline{DQS}$ , DQSL need to be within the respective limits ( $V_{IH}(DC)$  max,  $V_{IL}(DC)$ min) for single-ended signals CK,  $\overline{CK}$ , DQS,  $\overline{DQS}$ , DQSL need to be within the respective limits ( $V_{IH}(DC)$  max,  $V_{IL}(DC)$ min) for single-ended signals CK,  $\overline{CK}$ , DQS,  $\overline{DQS}$ , DQSL need to be within the respective limits ( $V_{IH}(DC)$  max,  $V_{IL}(DC)$ min) for single-ended signals  $\overline{CK}$ ,  $\overline$ ended signals as well as the limitations for overshoot and undershoot. Refer to "overshoot and Undersheet Specification"

[ Table 4 ] Allowed time before ringback (tDVAC) for CK -  $\overline{\text{CK}}$  and DQS -  $\overline{\text{DQS}}$

|                  |      |                      | DDR3-800/10                                       | 66/1333/1600 | )                   |                                               |                                                       | DDR3 | 3-1866                                                           |     |

|------------------|------|----------------------|---------------------------------------------------|--------------|---------------------|-----------------------------------------------|-------------------------------------------------------|------|------------------------------------------------------------------|-----|

| Slew Rate [V/ns] |      | C [ps]<br>AC)= 350mV | tDVAC [ps]<br>@ V <sub>IH/Ldiff</sub> (AC)= 300mV |              | @ VIH/L<br>(DQS - D | C [ ps ]<br>diff(ac) =<br>QS#) only<br>ional) | tDVAC [ps]<br>@ V <sub>IH/Ldiff</sub> (AC)<br>= 300mV |      | tDVAC [ps]<br>@ V <sub>IH/Ldiff</sub> (AC)<br>= (CK - CKS#) only |     |

|                  | min  | max                  | min                                               | max          | min                 | max                                           | min                                                   | max  | min                                                              | max |

| > 4.0            | 75   | -                    | 175                                               | -            | 214                 | -                                             | 134                                                   | -    | 139                                                              | -   |

| 4.0              | 57   | -                    | 170                                               | -            | 214                 | -                                             | 134                                                   | -    | 139                                                              | -   |

| 3.0              | 50   | -                    | 167                                               | -            | 191                 | -                                             | 112                                                   | -    | 118                                                              | -   |

| 2.0              | 38   | -                    | 119                                               | -            | 146                 | -                                             | 67                                                    | -    | 77                                                               | -   |

| 1.8              | 34   | -                    | 102                                               | -            | 131                 | -                                             | 52                                                    | -    | 63                                                               | -   |

| 1.6              | 29   | -                    | 81                                                | -            | 113                 | -                                             | 33                                                    | -    | 45                                                               | -   |

| 1.4              | 22   | -                    | 54                                                | -            | 88                  | -                                             | 9                                                     | -    | 23                                                               | -   |

| 1.2              | note | -                    | 19                                                | -            | 56                  | -                                             | note                                                  | -    | note                                                             | -   |

| 1.0              | note | -                    | note                                              | -            | 11                  | -                                             | note                                                  | -    | note                                                             | -   |

| < 1.0            | note | -                    | note                                              | -            | note                | -                                             | note                                                  | -    | note                                                             | -   |

NOTE: Rising input differential signal shall become equal to or greater than VIHdiff(ac) level and Falling input differential signal shall become equal to or less than VILdiff(ac) level.

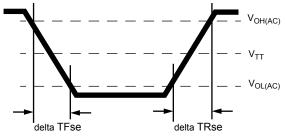

#### 11.3.3 Single-ended Requirements for Differential Signals

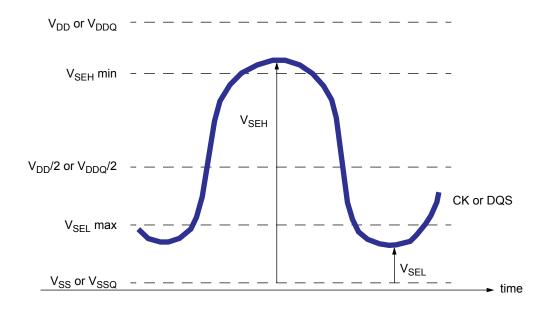

Each individual component of a differential signal (CK, DQS,  $\overline{CK}$ ,  $\overline{DQS}$ ) has also to comply with certain requirements for single-ended signals. CK and  $\overline{CK}$  have to approximately reach  $V_{SEH}$ min /  $V_{SEL}$ max (approximately equal to the ac-levels ( $V_{IH}(AC)$  /  $V_{IL}(AC)$ ) for ADD/CMD signals) in every half-cycle.

DQS,  $\overline{DQS}$  have to reach  $V_{SEH}$ min /  $V_{SEL}$ max (approximately the ac-levels ( $V_{IH}(AC)/V_{IL}(AC)$ ) for DQ signals) in every half-cycle proceeding and following a valid transition.

Note that the applicable ac-levels for ADD/CMD and DQ's might be different per speed-bin etc. E.g. if  $V_{IH}150(AC)/V_{IL}150(AC)$  is used for ADD/CMD signals, then these ac-levels apply also for the single-ended signals CK and  $\overline{CK}$ .

Figure 4. Single-ended requirement for differential signals

Note that while ADD/CMD and DQ signal requirements are with respect to  $V_{REF}$ , the single-ended components of differential signals have a requirement with respect to  $V_{DD}/2$ ; this is nominally the same. The transition of single-ended signals through the ac-levels is used to measure setup time. For single-ended components of differential signals the requirement to reach  $V_{SEL}$ max,  $V_{SEH}$ min has no bearing on timing, but adds a restriction on the common mode characteristics of these signals.

[ Table 5 ] Single ended levels for CK, DQS, CK, DQS

| Symbol           | Parameter                           | DDR3-800/1066              | Unit                       | NOTE  |      |

|------------------|-------------------------------------|----------------------------|----------------------------|-------|------|

| Symbol           | r ai ailletei                       | Min                        | Max                        | Oilit | NOTE |

| V <sub>SEH</sub> | Single-ended high-level for strobes | (V <sub>DD</sub> /2)+0.175 | NOTE 3                     | V     | 1, 2 |

| V SEH            | Single-ended high-level for CK, CK  | (V <sub>DD</sub> /2)+0.175 | NOTE 3                     | V     | 1, 2 |

| V <sub>SEL</sub> | Single-ended low-level for strobes  | NOTE 3                     | (V <sub>DD</sub> /2)-0.175 | V     | 1, 2 |

| V SEL            | Single-ended low-level for CK, CK   | NOTE 3                     | (V <sub>DD</sub> /2)-0.175 | V     | 1, 2 |

#### NOTE

- 1. For CK,  $\overline{CK}$  use  $V_{IH}/V_{IL}(AC)$  of ADD/CMD; for strobes (DQS,  $\overline{DQS}$ ) use  $V_{IH}/V_{IL}(AC)$  of DQs.

- 2. V<sub>IH</sub>(AC)/V<sub>IL</sub>(AC) for DQs is based on V<sub>REFDQ</sub>; V<sub>IH</sub>(AC)/V<sub>IL</sub>(AC) for ADD/CMD is based on V<sub>REFCA</sub>; if a reduced ac-high or ac-low level is used for a signal group, then the reduced level applies also here

- 3. These values are not defined, however the single-ended signals CK,  $\overline{CK}$ , DQS,  $\overline{DQS}$  need to be within the respective limits (V<sub>IH</sub>(DC) max, V<sub>IL</sub>(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot Specification"

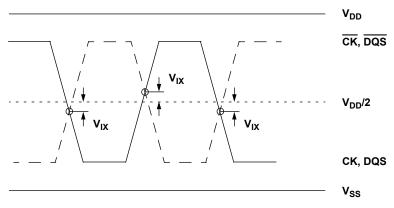

#### 11.3.4 Differential Input Cross Point Voltage

To guarantee tight setup and hold times as well as output skew parameters with respect to clock and strobe, each cross point voltage of differential input signals (CK,  $\overline{CK}$  and DQS,  $\overline{DQS}$ ) must meet the requirements in below table. The differential input cross point voltage  $V_{IX}$  is measured from the actual cross point of true and complement signal to the mid level between of  $V_{DD}$  and  $V_{SS}$ .

Figure 5. VIX Definition

#### [ Table 6 ] Cross point voltage for differential input signals (CK, DQS)

| Symbol          | Parameter                                                                                        | DDR3-800/1066/ | DDR3-800/1066/1333/1600/1866 |      |      |

|-----------------|--------------------------------------------------------------------------------------------------|----------------|------------------------------|------|------|

| Symbol          |                                                                                                  | Min            | Max                          | Unit | NOTE |

| V <sub>IX</sub> | V <sub>IX</sub> Differential Input Cross Point Voltage relative to V <sub>DD</sub> /2 for CK, CK | -150           | 150                          | mV   | 2    |

| VIX             | VIX Differential input closs Foliat voltage relative to VDD/2 for CK,CK                          |                | 175                          | mV   | 1    |

| V <sub>IX</sub> | Differential Input Cross Point Voltage relative to V <sub>DD</sub> /2 for DQS, DQS               | -150           | 150                          | mV   | 2    |

#### NOTE

2. The relation between  $\rm V_{IX}$  Min/Max and  $\rm V_{SEL}/\rm V_{SEH}$  should satisfy following.

$$\begin{split} &(V_{DD}/2) + V_{IX}(Min) - V_{SEL} \geq 25mV \\ &V_{SEH} - ((V_{DD}/2) + V_{IX}(Max)) \geq 25mV \end{split}$$

### 11.4 Slew Rate Definition for Single Ended Input Signals

See "Address / Command Setup, Hold and Derating" for single-ended slew rate definitions for address and command signals. See "Data Setup, Hold and Slew Rate Derating" for single-ended slew rate definitions for data signals.

### 11.5 Slew rate definition for Differential Input Signals

Input slew rate for differential signals (CK,  $\overline{\text{CK}}$  and DQS,  $\overline{\text{DQS}}$ ) are defined and measured as shown in below.

#### [ Table 7 ] Differential input slew rate definition

| Description                                                       | Meas                   | ured                   | Defined by                                                       |

|-------------------------------------------------------------------|------------------------|------------------------|------------------------------------------------------------------|

| Description                                                       | From                   | То                     | Defined by                                                       |