#### **Features**

- Input Voltage Range: 36 V to 57 V

- 10 W Output

- IEEE Std. 802.3af Compliant (for PoE-PD Interface)

- 85 % Efficiency

- Low Profile (9 mm)

- Output Voltage Trim/Adjust

- Under-Voltage Lockout

- Input Transient Suppressor

- Internal EMI Filter

- Meets FCC Class B Radiated & Class A Conducted

- Output Inhibit Control

- Short Circuit Protection

- Over Temperature Shutdown

- 1500 VDC Isolation

- Safety Approvals (Pending): UL 60950, cUL 60950, EN60950

## **Description**

The PTB48540 series of power modules is specifically designed to provide an isolated, low-voltage power source to a remote Powered Device (PD) in Power-Over-Ethernet (PoE) applications. These modules are rated 10 W and incorporate all the necessary interface requirements to comply with IEEE Std. 802.3af, for managing the input power to the PD from the PoE Power Sourcing Equipment (PSE). This includes PD detection and PD classification current signatures required for the PSE. The modules are compatible with PD classifications, class 0 through class 3.

In addition to a fully integrated DC/DC converter, each PTB48540 power module incorporates internal input diode bridges

to support both Data Line and Spare Line pair standard Ethernet power connections, an integral transient suppressor for input over-voltage protection, and an EMI filter to ensure noise compatibility with Ethernet data signals.

Other features include an input undervoltage lockout (UVLO), over-current and short-circuit protection, an output voltage adjust/trim, and over-temperature protection. An "Output Inhibit" control allows the output voltage to be turned off to support an idle condition or power saving mode. The output voltage options are for 3.3-V, 5-V, or 12-V output. The target applications are small low-power remote IP appliances, such as security card readers and cameras, test dongles, and IP phone consoles.

### **Pin Assignments**

| Pin | Function         |

|-----|------------------|

| 1   | -Vout            |

| 2   | Vout Adj         |

| 3   | +Vout            |

| 4   | Input Ref        |

| 5   | Detect A         |

| 6   | Detect B         |

| 7   | Spare Line B     |

| 8   | Spare Line A     |

| 9   | Data Line B      |

| 10  | Data Line A      |

| 11  | Class B          |

| 12  | Class A          |

| 13  | Output Inhibit * |

Shaded functions indicate signals electrically common with the input.

\* Denotes negative logic:

Open = Normal operation

Low (Input Ref) = Output Off

## **Product Top View**

10-W Power-Over-Ethernet Isolated Power Module Assembly

SLTS224B - APRIL 2004 - REVISED JULY 2004

## **Ordering Information**

| Output V | oltage (PTB48540□xx) | Packag | ge Options (PTB48540) | x□□)         |

|----------|----------------------|--------|-----------------------|--------------|

| Code     | Voltage              | Code   | Description           | Pkg Ref. (1) |

| A        | 5 V                  | AH     | Horiz. T/H            | (EUP)        |

| В        | 3.3 V                | AS     | SMD, Standard (2)     | (EUQ)        |

| С        | 12 V                 |        |                       |              |

Notes: (1) Reference the applicable package reference drawing for the dimensions and PC board layout

(2) "Standard" option specifies 63/37, Sn/Pb pin solder material.

## **Pin Descriptions**

**-Vour:** This is the negative output from the module, with respect to +Vout. Both the +Vout and -Vout terminals are isolated from the Ethernet input, and used to power the PD appliance. When this pin is connected to the PD appliance common, a positive supply voltage is produced at +Vout.

**Vout Adj:** By connecting a single resistor to this pin, the regulated output voltage may be adjusted/trimmed by up to  $\pm 10$  % from the original set-point value. If no adjustment is desired, this pin should be left open circuit.

**+Vour:** This is the positive output from the module with respect to –Vout, and is used to power the PD appliance. By connecting this pin to the PD appliance common, a negative supply voltage will be produced at –Vout.

**Input Ref:** This pin provides access to the –Vin of the internal DC/DC converter, and is the 0-VDC reference for the *'Output Inhibit'* control.

**Detect A:** This is a control input that is normally left open circuit. The module incorporates an internal 24.9-k $\Omega$  resistor, between the ' $Detect\ A$ ' and ' $Detect\ B$ ' pins. This provides the PD with a correct "valid device" detection resistance for the PSE. By placing an external resistor between the ' $Detect\ A$ ' and ' $Detect\ B$ ' pins (in parallel with the internal 24.9-k $\Omega$  resistor) the module can be made to identify itself as a "non-valid device."

**Detect B:** This pin is used in conjunction with the 'Detect A' input only when it is desired for the PD to communicate a "non-valid" device signature to the PSE (see 'Detect A' description). 'Detect B' is also the rectified DC output from the module's internal diode bridges, and represents the positive DC input to the module's DC/DC converter. Connecting an external capacitor between this pin and the

'Input Ref' pin (0 V), adds more filter capacitance across the input of the DC/DC converter.

**Data Line A/B:** These are the main inputs from which the module obtains DC input power from the Ethernet connector. The connection of these inputs to the Ethernet connections must be via an IEEE 802.3af compliant signal transformer, that is designed for use in a PoE application. This is necessary to preserve the integrity of the Ethernet data traffic. Consult the example application for further information.

**Spare Line A/B:** These are alternative inputs from which the module may obtain DC input power. In a PoE application, 'Spare Line A' may be directly connected to pins 4 & 5, and 'Spare Line B' to pins 7 & 8 of an Ethernet RJ-45 connector. These connections are not used for data transmission.

**Class A/B:** The control inputs 'Class A' and 'Class B' allow the PD Class to be programmed from the module. The module incorporates an internal 4.42-k $\Omega$  resistor between the 'Class A' and 'Class B' inputs. This corresponds to a default "Class 0" PD classification signature being sent to the PSE. By adding an external resistor across these pins, the module can be programmed to other PD classifications. For further information, consult the PD class reference table in the application notes.

**Output Inhibit:** This is an open-collector (or open-drain) negative logic input. Applying a low-level voltage to this input, with respect to the 'Input Ref' pin, turns off the DC output voltage from the module. If the pin is left open-circuit, the module will operate as normal, producing an output voltage whenever it is connected to a valid PoE input source.

## 10-W Power-Over-Ethernet Isolated **Power Module Assembly**

SLTS224B - APRIL 2004 - REVISED JULY 2004

## **Specifications** (Unless otherwise stated, $T_a$ =25°C, $V_{in}$ =48V (1), and $I_o$ = $I_o$ max)

|                                                                    |                                                    |                                                                                  | P                     | PTB48540 SERIES |                  |               |

|--------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|-----------------|------------------|---------------|

| Characteristic                                                     | Symbol                                             | Conditions                                                                       | Min                   | Тур             | Max              | Units         |

| Output Current                                                     | $I_{o}$                                            | Over V <sub>in</sub> range PTB48540A (5 V<br>PTB48540B (3.3 V<br>PTB48540C (12 V | 7) 0.1 <sup>(2)</sup> |                 | 2<br>3<br>0.85   | A             |

| Input Voltage Range                                                | $V_{in}$                                           | Over I <sub>o</sub> Range                                                        | 36                    | _               | 57 (1)           | VDC           |

| Set Point Voltage Tolerance                                        | V <sub>o</sub> tol                                 | -                                                                                | _                     | ±1              | ±2               | $%V_{o}$      |

| Temperature Variation                                              | Reg <sub>temp</sub>                                | $-40 \le T_a \le +85 \text{ °C}, I_o = I_o \text{min}$                           | _                     | ±0.2            | _                | $%V_{o}$      |

| Line Regulation                                                    | Reg <sub>line</sub>                                | Over V <sub>in</sub> range                                                       | _                     | ±1              | _                | mV            |

| Load Regulation                                                    | Regload                                            | Over I <sub>o</sub> range                                                        | _                     | ±5              | _                | mV            |

| Total Output Voltage Variation                                     | $\Delta V_{o}$ tot                                 | Includes set-point, line, load,<br>$-40 \le \Gamma_a \le +85 ^{\circ}\text{C}$   | _                     | ±1.5            | ±3               | $%V_{o}$      |

| Efficiency                                                         | η                                                  | PTB48540C (12 N<br>PTB48540A (5 N<br>PTB48540B (3.3 N                            | Λ) —                  | 85<br>82<br>79  | _                | %             |

| $V_{o}$ Ripple (pk-pk)                                             | $V_r$                                              | 20 MHz bandwidth                                                                 | _                     | 50              | _                | $mV_{pp}$     |

| Transient Response                                                 | t <sub>tr</sub>                                    | $\underline{1}$ A/µs load step, 50 % to 100 % $\underline{I}_{o}$ max            |                       | 100             | _                | μs            |

|                                                                    | $\Delta  m V_{tr}$                                 | $V_{o}$ over/undershoot $V_{o} \le 5$ $V_{o} = 12$                               | V —<br>V —            | ±150<br>±200    | _                | mV            |

| Output Voltage Adjust                                              | $V_{adj}$                                          |                                                                                  | _                     | ±10             | _                | $%V_{o}$      |

| Current Limit Threshold                                            | $I_{ m lim}$                                       | $V_{in} = 42 \text{ V}, \Delta V_o = -1 \%$                                      | _                     | 150             | _                | $%I_{o}$ max  |

| Switching Frequency                                                | $f_{s}$                                            | Over V <sub>in</sub> range                                                       | 200                   | 300             | 400              | kHz           |

| Under-Voltage Lockout                                              | UVLO                                               | $V_{ m in}$ rising $V_{ m in}$ falling                                           | 30                    | 40<br>32        | <u>42</u>        | V             |

| Output Inhibit (Pin 13)<br>Input High Voltage<br>Input Low Voltage | $egin{array}{c} V_{ m IH} \ V_{ m IL} \end{array}$ | Referenced to Input Ref (pin 4)                                                  | 4.5<br>-0.2           | _               | Open (3)<br>+0.8 | V             |

| Input Low Current                                                  | $I_{IL}$                                           |                                                                                  |                       | -2              | _                | mA            |

| Standby Input Current                                              | I <sub>in</sub> standby                            | pins 13 & 4 connected                                                            |                       | 1               |                  | mA            |

| External Output Capacitance                                        | $C_{out}$                                          | $V_o \le 5$ $V_o = 12$                                                           | V 0 (4)               | _               | 1000<br>330      | μF            |

| Internal Input Capacitance                                         | C <sub>in</sub>                                    | $V_{in}$ < UVLO threshold $V_{in}$ > UVLO threshold                              | 0.05<br>5             | 0.1<br>7        | 0.12<br>—        | μF            |

| Detection Resistance                                               | R <sub>detect</sub>                                | $2.7 \text{ V} \le V_{\text{in}} \le 10.1 \text{ V}$                             | 23.75                 | 24.9 (5)        | 26.25            | kΩ            |

| Classification Current                                             | I <sub>class</sub>                                 | $14.5 \text{ V} \le V_{\text{in}} \le 20.5 \text{ V}$                            | 2                     | 2.5 (6)         | 3                | mA            |

| Operating Temperature Range                                        | $T_a$                                              | Over V <sub>in</sub> range                                                       | -40                   | _               | +85 (7)          | °C            |

| Over Temperature Protection                                        | OTP                                                | Measured at pin 7 Threshol<br>Hysteris                                           |                       | 20              | _                | °C            |

| Isolation Voltage<br>Capacitance<br>Resistance                     |                                                    | Input-output                                                                     | $\frac{1500}{10}$     | 1,100<br>—      | =                | V<br>pF<br>MΩ |

| Solder Reflow Temperature                                          | $T_{reflow}$                                       | Surface temperature of module body or pins                                       | _                     | _               | 235 (8)          | °C            |

| Storage Temperature                                                | $T_s$                                              | _                                                                                | -40                   | _               | +125             | °C            |

| Reliability                                                        | MTBF                                               | Per Bellcore TR-332<br>50 % stress, T <sub>a</sub> =40 °C, ground benign         | 4                     | _               | _                | 106 Hrs       |

| Mechanical Shock                                                   | _                                                  | Per Mil-Std-883D, method 2002.3,<br>1 mS, half-sine, mounted to a fixture        | _                     | 500             | _                | G's           |

| Mechanical Vibration                                               | _                                                  | Mil-Std-883D, Method 2007.2 Pkg EU                                               |                       | 20<br>7.5       | _                | G's           |

|                                                                    |                                                    | 20-2000 Hz, soldered to PC Pkg EU                                                | ~ —                   | 1.5             |                  |               |

| Weight                                                             | _                                                  | — Prg EU                                                                         | _                     | 12              |                  | grams         |

Notes: (1) The input voltage Vin is applied and measured between 'Data Line A' (pin 10) and 'Data Line B' (pin 9), or between 'Spare Line A' (pin 8) and 'Spare Line B' (pin 7). These inputs accept either polarity.

(2) The DC/DC converter will operate at no load with reduced specifications.

- (3) The Output Inhibit (pin 13) is referenced to 'Input Ref' (pin 4) and has an internal pull-up. If it is left open circuit the converter will operate when input power is applied. The open-circuit voltage is typically 5 V. Refer to the application notes for interface considerations.

- (4) An output capacitor is not required for proper operation.

(5) This is the default for a "Valid Device" PD detection signature.

(6) This is the default for a "Class 0" PD classification signature.

- (7) See Safe Operating Area curves or contact the factory for the appropriate derating.

- (8) During the reflow of the SMD package version do not elevate the peak temperature of the module, pins, or internal components above the stated maximum.

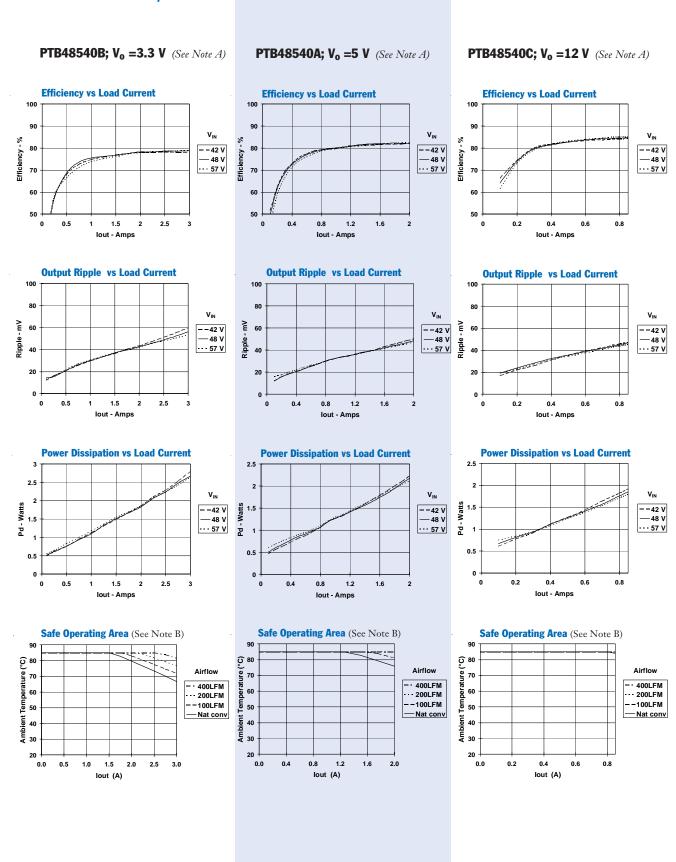

# Typical Characteristics

10-W Power-Over-Ethernet Isolated Power Module Assembly

SLTS224B - APRIL 2004 - REVISED JULY 2004

Note A: Characteristic data has been developed from actual products tested at 25°C. This data is considered typical data for the converter.

Note B: SOA curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to modules soldered directly to a 4 in. × 4 in. double-sided PCB with 1 oz. copper.

# **Operating Features of the PTB48540 Series Power-Over-Ethernet Modules**

#### **Overview**

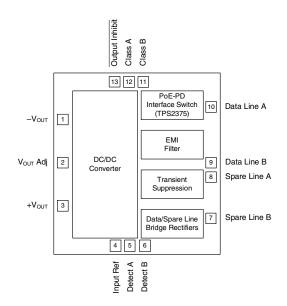

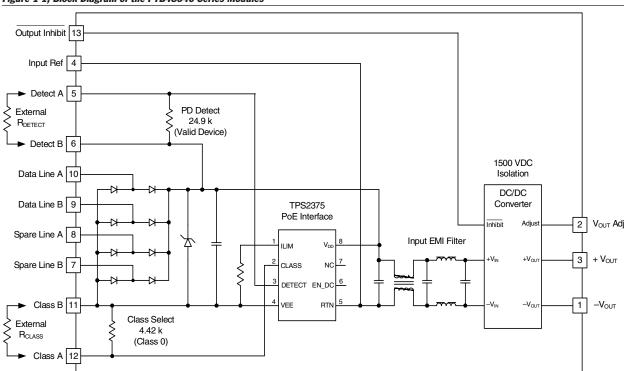

Figure 1-1 shows the block diagram of the PTB48540 series of Power-over-Ethernet (PoE) modules. Input power to the module can be supplied through either the Data Line A/B or Spare Line A/B associated Ethernet connections. A diode bridge associated with each of these input pairs allows the input source to be supplied in either polarity. A transient suppressor, located across the common output of the diode bridges, protects the module against power surges.

The input power to the internal DC/DC converter is controlled by the TPS2375 IC. This IC is a power interface switch, specifically designed for use with PoE powered devices. The IC provides the device detection, classification, and current limiting control that is necessary for a powered device (PD) to comply with the IEEE 802.af Standard. The DC/DC converter input circuit includes an EMI filter, which maintains the module in compliance with CISPR 22 (EN5022); class 'B' for radiated, and class 'A' for conducted emissions.

#### **PD Detection**

Prior to power up, the PoE power sourcing equipment (PSE) must detect a 24.9-kΩ "discovery" load resistance from the PD. This default value of resistance is necessary for the PD to be recognized as a "valid device" by the PSE. A 24.9-k $\Omega$  resistor is provided internally to the PTB48540 modules. It is located across the 'Detect A' (pin 5) and 'Detect B' (pin 6) terminals. By placing an external resistor across these pins (in parallel with the internal 24.9-k $\Omega$  resistor), the module can be made to communicate a "non-valid device" signature to the PSE. A non-valid device is recognized by a resistance of less than 12 kΩ. Connecting a 16.9-kΩ external resistor between the 'Detect A' and 'Detect B' pins creates an equivalent resistance of 10 k $\Omega$ . This is sufficient to communicate a non-valid device signature. The external resistor should not be less than 16.9 k $\Omega$  as this increases power dissipation in the power interface IC.

## **PD Classification Signature**

The PSE uses a classification current to determine the maximum supply current that the PD is allowed to draw. The classification current is sensed by the PSE when the supply voltage to the PD is between 15 V and 20 V. The classification current is set on the PTB48540 by a programming resistance. Table 1-1 gives the resistance values

Figure 1 1; Block Diagram of the PTB48540 Series Modules

Table 1-1; PD Class Programming Resistance

| PD    |             | PD Dema | nd (watts) | Class Program | External |  |

|-------|-------------|---------|------------|---------------|----------|--|

| Class | Usage       | Min     | Max        | Resistance    | Resistor |  |

| 0     | Default     | 0.44    | 12.95      | 4.42 kΩ       | None     |  |

| 1     | Optional    | 0.44    | 3.84       | 950 Ω         | 1.21 kΩ  |  |

| 2     | Optional    | 3.84    | 6.49       | 543 Ω         | 619 Ω    |  |

| 3     | Optional    | 6.49    | 12.95      | 360 Ω         | 392 Ω    |  |

| 4     | Not Allowed | — Futur | e Use —    | 252 Ω         | 267 Ω    |  |

for the different types of PD class defined in the IEEE 802.3af Standard. The power modules support the PD classification protocol with a default 'Class 0' signature. 'Class 0' corresponds to a 4.42-k $\Omega$  programming resistance, which is set by an internal resistor located between the 'Class A' (pin 12) and 'Class B' (pin 11) terminals. By placing an external resistor across the Class A/B pins (in parallel with the internal 4.42-k $\Omega$  resistor) the power module can be made to communicate one of the alternate classifications to the PSE. Consult Table 1-1 for the external resistance values.

#### **Under-Voltage Lockout**

The UVLO prevents the internal DC/DC converter from seeing an input voltage until the voltage applied to either the 'Data Line A/B' or 'Spare Line A/B' pair of Ethernet connections approaches 42 V. The UVLO threshold correlates to a voltage between the 'Detect B' (pin 6) and 'Class B' (pin 11) terminals of approximately 39.3 V. Only after the voltage applied from the Ethernet is above the UVLO threshold is the module's internal bus voltage allowed to rise. The internal bus powers the DC/DC converter and can be measured between the 'Detect B' (pin 6) and 'Input Ref' (pin 4) terminals.

## **Input Capacitance**

In accordance with the IEEE 802.3af Standard, the PTB48540 power modules provide an input capacitance of 0.1 µF to the PSE when communicating the required detection and classification signatures. Once fully powered (V<sub>in</sub> ≥42 V), the PSE will see the combined input capacitance of the EMI filter and DC/DC converter; approximately 7 µF. This capacitance is sufficient to operate the module's internal DC/DC converter, and satisfies the 5 µF minimum capacitance required by the IEEE 802.3af Standard. For improved hold-up capability, this input capacitance can be increased with an external capacitor. Connect the anode of the external capacitor to 'Detect B' (pin 6), and the cathode to the 'Input Ref' (pin 4). During power up the power interface IC limits the inrush current for charging the input capacitance. Additional capacitance increases the power dissipation in the IC. For this reason the maximum recommended value of external capacitance is 220 µF (100-V electrolytic).

#### Startup

Startup of the module in a PoE application consists of a complex process of handshaking states between the module and PSE. During the PD detection state the PSE uses a low voltage (<10 V) to detect the module's "valid device" resistance signature. This is followed by the classification detection state where the PSE applies a voltage of 15 V to 20 V to detect the module's PD class. The PSE continues to raise the input voltage, but the input voltage to the internal DC/DC converter is held at zero until the voltage from the PSE approaches 42 V. At an input voltage of 42 V or higher, the module's power interface IC allows the internal bus voltage to rise using a limited amount of inrush current. Approximately 50 ms after the DC/DC converter input filter capacitors are fully charged, the module is able to produce a regulated output voltage.

#### **Converter Over-Current Protection**

The internal DC/DC converter has inherent protection against an output load fault. Whenever its load current exceeds the over-current protection threshold (see specification table) the converter momentarily turns its output off. After a short period (<100 ms), the regulator will attempt to power up again by executing a soft-start power up. The converter will continue in a successive cycle of shutdown, followed by soft-start power up until the load fault is removed.

When the DC/DC converter is powered from just the Ethernet source, a load current above its rated output (but below its over-current threshold) will likely activate the over-current protection offered by the power interface IC. This is especially at input voltages lower than 48 V.

## **Ethernet Over-Current Protection**

Protection is also provided for the Ethernet power source equipment (PSE). In event of a fault across the module's internal bus, the onboard power interface IC limits the maximum current that may be drawn from the PSE to no less than 405 mA. This prevents the DC/DC converter from drawing excessive input current and also safeguards against external faults that may occur across the 'Detect B' (pin 6) and 'Input Ref' (pin 4) terminals. Note: These terminals can be used to add capacitance to the module's internal bus.

Load faults applied to the DC/DC converter's output will most often trigger the power interface IC's protection mechanism prior to activating the converter's own current limit threshold. In these instances the power interface IC will completely shut down the module's internal bus. This is a latched condition. It is reset by the PoE source when it attempts another power-up cycle after it senses loss of the PD's Maintain Power Signature (10 mA).

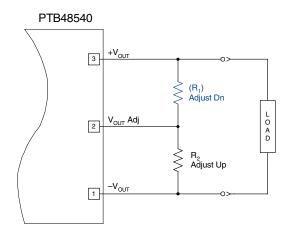

## Adjusting the Output Voltage of the PTB48540 Series of Power Over Ethernet Modules

The set-point output voltage of the PTB48540 series of PoE modules may be adjusted (trimmed) by up to  $\pm 10$  %. This is accomplished with the addition of a single external resistor. For the input voltage range specified in the data sheet, Table 2-1 gives the allowable adjustment range for each model as  $V_{\rm O}$  (min) and  $V_{\rm O}$  (max).

**Adjust Up:** An increase in the output voltage is obtained by adding a resistor,  $R_2$  between pin 2 ( $V_{out}$  Adj), and pin 1 ( $-V_{out}$ ).

**Adjust Down:** Add a resistor  $(R_1)$ , between pin 2  $(V_{out} Adj)$  and pin 3  $(+V_{out})$ .

Refer to Figure 2-1 and Table 2-2 for both the placement and value of the required resistor,  $(R_1)$  or  $R_2$ .

The values of  $(R_1)$  [adjust down], and  $R_2$  [adjust up], can also be calculated using the following formulas.

$$\begin{array}{cccc} (R_1) & = & \frac{56.2 \; (V_a - 1.225)}{V_o - V_a} & - \, R_s & k\Omega \\ \end{array}$$

$$R_2 = \frac{68.845}{V_a - V_o} - R_s \qquad k\Omega$$

Where,  $V_o$  = Original output voltage  $V_a$  = Adjusted output voltage

$R_s$  = Internal resistance (Table 2-1)

## Notes:

- 1. Use only a single 1 % resistor in either the  $(R_1)$  or  $R_2$  location. Place the resistor as close to the module as possible.

- 2. Never connect capacitors to  $V_{\rm o}$  adjust. Any capacitance added to the  $V_{\rm o}$  adjust control pin will affect the stability of the module.

- 3. The output power is limited to 10 W. If the output voltage is increased, the maximum load current must be derated according to the following equation.

$$I_o(max) = \frac{10}{V_a}$$

In any instance, the load current must not exceed the converter's rated current (See Table 2-1).

Table 2-1

| DC/DC CONVERTER ADJUSTMENT PARAMETERS     |        |       |        |  |  |  |  |  |

|-------------------------------------------|--------|-------|--------|--|--|--|--|--|

| Series Pt # PTB48540B PTB48540A PTB48540C |        |       |        |  |  |  |  |  |

| Rated Current <sup>3</sup>                | 3 A    | 2 A   | 0.85 A |  |  |  |  |  |

| V <sub>o</sub> (nom)                      | 3.3 V  | 5 V   | 12 V   |  |  |  |  |  |

| Vo(min)                                   | 2.95 V | 4.5 V | 10.8 V |  |  |  |  |  |

| Vo(max)                                   | 3.65 V | 5.5 V | 13.2 V |  |  |  |  |  |

| R <sub>s</sub> (kΩ)                       | 187    | 110   | 49.9   |  |  |  |  |  |

#### Figure 2-1; Adjust Resistor Placement

Table 2-2

| Series Pt #            | PTB48540B              | PTB48540A             | PTB485400  |

|------------------------|------------------------|-----------------------|------------|

| V <sub>o</sub> (nom)   | 3.3 V                  | 5 V                   | 12 V       |

| V <sub>a</sub> (req'd) | 3.5 7                  |                       | 12 1       |

| 2.95                   | (90.0)kΩ               |                       |            |

| 3.0                    | (146.0)kΩ              |                       |            |

| 3.05                   | (223.0)kΩ              |                       |            |

| 3.1                    | (340.0)kΩ              |                       |            |

| 3.15                   | (534.0)kΩ              |                       |            |

| 3.2                    | (923.0)kΩ              |                       |            |

| 3.25                   | (2090.0)kΩ             |                       |            |

| 3.3                    |                        |                       |            |

| 3.35                   | 1190.0kΩ               |                       |            |

| 3.4                    | 501.0kΩ                |                       |            |

| 3.45                   | 272.0kΩ                |                       |            |

| 3.5                    | 157.0kΩ                |                       |            |

| 3.55                   | 88.4kΩ                 |                       |            |

| 3.6                    | 42.5kΩ                 |                       |            |

| 3.65                   | $9.7 \mathrm{k}\Omega$ |                       |            |

| •                      |                        |                       |            |

| 4.5                    |                        | $(258.0)$ k $\Omega$  |            |

| 4.6                    |                        | $(364.0)$ k $\Omega$  |            |

| 4.7                    |                        | $(541.0)$ k $\Omega$  |            |

| 4.8                    |                        | $(895.0)$ k $\Omega$  |            |

| 4.9                    |                        | $(1960.0)$ k $\Omega$ |            |

| 5.0                    |                        |                       |            |

| 5.1                    |                        | 578.0kΩ               |            |

| 5.2                    |                        | 234.0kΩ               |            |

| 5.3                    |                        | 119.0kΩ               |            |

| 5.4                    |                        | 62.1kΩ                |            |

| 5.5                    |                        | 27.7kΩ                |            |

| •                      |                        |                       |            |

| 10.8                   |                        |                       | (399.0)kΩ  |

| 11.0                   |                        |                       | (499.0)kΩ  |

| 11.5                   |                        |                       | (1110.0)kΩ |

| 12.0                   |                        |                       |            |

| 12.5                   |                        |                       | 87.8kΩ     |

| 13.0                   |                        |                       | 18.9kΩ     |

| 13.2                   |                        |                       | 7.5kΩ      |

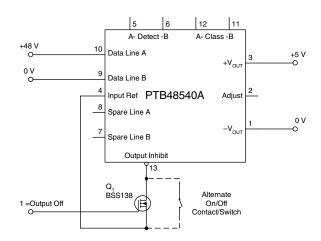

## Using the Output Inhibit Control with the PTB48540 Power-over-Ethernet Modules

The PTB48540 Power-over-Ethernet (PoE) modules incorporate all the necessary interface requirements to provide 10 W of regulated DC voltage from a recognized Power-over-Ethernet source.

One of the operating features of these modules allows the output voltage to be turned off, thereby placing the module in an idle state. This may be useful for applications that have an alternative voltage source available, such as a wall adapter.

The "Output Inihibit" control is provided by pin 13. The module functions normally with this pin open-circuit, providing a regulated output voltage whenever a valid source voltage is supplied from the Ethernet connection. When a low voltage is applied to pin 13, with respect to the "Input Ref" terminal (pin 4), the output is turned off. Even though the Ethernet source is still present.

Figure 3-1 is an application schematic, which shows how the "Output Inhibit" control may be used. Either a discrete transistor  $(Q_1)$ , or a contact switch may be used. The "Output Inhibit" control pin has its own internal pull-up (See notes 2 & 3). Table 3-1 gives the threshold requirements.

When placed in the "Off" state, the standby current drawn from the input source is typically reduced to 1 mA<sup>3</sup>.

Table 3-1; Pin 13 Output Inhibit Control Parameters 1

| Parameter                       | Min   | Тур   | Max   |  |

|---------------------------------|-------|-------|-------|--|

| Enable (VIH)                    | 4.5 V | _     | _     |  |

| Disable (VIL)                   | _     | _     | 0.8 V |  |

| V <sub>O/c</sub> [Open-Circuit] |       | 5 V   |       |  |

| Iin [pins 13 & 4 connnected     | ed] — | −1 mA | _     |  |

#### **Notes:**

- 1. The *Output Inhibit* control uses *Input Ref* (pin 4) as its 0-V reference. All voltages specified are with respect to the *Input Ref* pin.

- Use an open-collector device (preferably a discrete transistor or switch) for the *Output Inhibit* input. A pull-up resistor is not necessary. To turn the output off, the control pin should be pulled low to less than 0.8 VDC.

- 3. The module's idle current is typically less than 1 mA. This is below the minimum power signature (MPS) current, required for the PoE source to continue providing the PD with a source voltage. This will inevitably result in the removal of the module's input source. However, the PSE will endevour to periodically re-apply input power after detecting that the PD is still a valid device. This cycle may be prevented by also modifying the module's 'Detect' signature resistance so that it reflects an invalid device to the PSE.

Figure 3-1

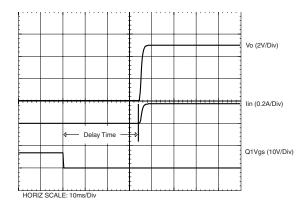

**Turn-On Time:** In the circuit of Figure 3-1, turning  $Q_1$  on applies a low-voltage to pin 13 and disables the module output. Correspondingly, turning  $Q_1$  off allows pin 13 to be pulled high by an internal pull-up resistor. The module produces a regulated output voltage within 60 ms. Figure 3-2 shows shows the output response of a PTB48540A (5 V) following the turn-off of  $Q_1$ . The turn off of  $Q_1$  corresponds to the drop in  $Q_1$  Vgs. Although the rise-time of the output voltage is short (<5 ms), the indicated delay time will vary depending upon the input voltage and the module's internal timing. The waveform was measured with a 48 Vdc input voltage, and a 1.4 A resistive load.

Figure 3-2

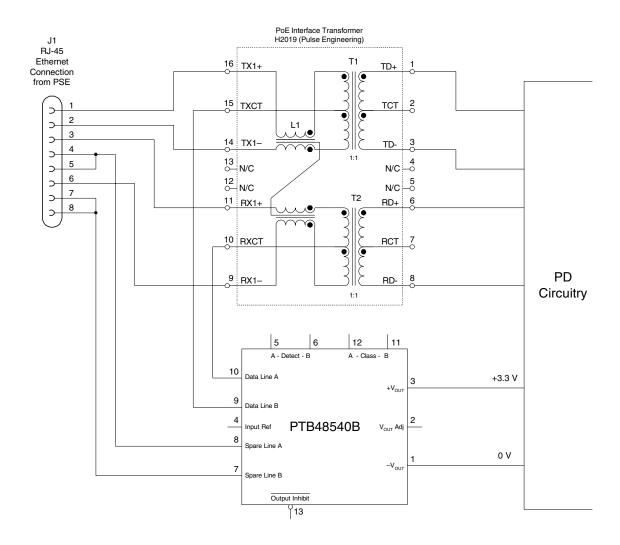

# Using the PTB48540 Series Module in a Power-Over-Ethernet (PoE) Application

The schematic of Figure 4-1 shows an example of how a PTB48540 module may be connected to a PoE compliant system. The connector J1 is the input from the PoE source.

In a Power-over-Ethernet (PoE) application, the power and high-frequency data signals share the same conductors in the Ethernet cable. The data and power signals must be separated using an IEEE 802.3af compliant PoE magnetic module.

The magnetic module incorporates the customary isolation transformers, T1 and T2. The transformers each include a center tap, across which the dc current from the Ethernet power source equipment (PSE) is conveniently extracted. The transmit and receive hf Ethernet data

appear as differential signals to each transformer. These signals are isolated by the transformers, allowing the Ethernet communication content to flow freely between the connector and the powered device (PD) circuitry.

The common-mode inductor, L1, is a popular addition to off-the-shelf PoE magnetic modules. The inductor provides additional rejection to common mode noise currents, which may otherwise be present on either the data or power signals.

The PTB48540 module complies with the PoE protocols, provides the required isolation, and converts the raw power from the PSE to a precision regulated 3.3-VDC power source for the remote PD circuitry.

Figure 4-1; Power-Over-Ethernet Application Schematic

20-Jul-2012

## **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type            | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup>               | Samples<br>(Requires Login) |

|------------------|-----------------------|-------------------------|--------------------|------|-------------|-------------------------|----------------------|--------------------------------------------|-----------------------------|

| PTB48540AAH      | NRND                  | Through-<br>Hole Module | EUP                | 13   | 12          | Pb-Free (RoHS)          | SN                   | N / A for Pkg Type                         |                             |

| PTB48540AAS      | NRND                  | Surface<br>Mount Module | EUQ                | 13   | 12          | TBD                     | SNPB                 | Level-1-235C-UNLIM/<br>Level-3-260C-168HRS |                             |

| PTB48540AAZ      | NRND                  | Surface<br>Mount Module | EUQ                | 13   | 12          | Pb-Free (RoHS)          | SNAGCU               | Level-3-260C-168 HR                        |                             |

| PTB48540BAH      | NRND                  | Through-<br>Hole Module | EUP                | 13   | 12          | Pb-Free (RoHS)          | SN                   | N / A for Pkg Type                         |                             |

| PTB48540BAZ      | NRND                  | Surface<br>Mount Module | EUQ                | 13   | 12          | Pb-Free (RoHS)          | SNAGCU               | Level-3-260C-168 HR                        |                             |

| PTB48540CAD      | NRND                  | Through-<br>Hole Module | EUP                | 13   | 12          | Pb-Free (RoHS)          | SN                   | N / A for Pkg Type                         |                             |

| PTB48540CAH      | NRND                  | Through-<br>Hole Module | EUP                | 13   | 12          | Pb-Free (RoHS)          | SN                   | N / A for Pkg Type                         |                             |

| PTB48540CAS      | NRND                  | Surface<br>Mount Module | EUQ                | 13   | 12          | TBD                     | SNPB                 | Level-1-235C-UNLIM/<br>Level-3-260C-168HRS |                             |

| PTB48540CAZ      | NRND                  | Surface<br>Mount Module | EUQ                | 13   | 12          | Pb-Free (RoHS)          | SNAGCU               | Level-3-260C-168 HR                        |                             |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

## **PACKAGE OPTION ADDENDUM**

20-Jul-2012

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| roducts |              | Applications |

|---------|--------------|--------------|

|         | ti aaaa/adia | A            |

Pr

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio www.ti.com/communications **Amplifiers** amplifier.ti.com Communications and Telecom **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** Consumer Electronics www.ti.com/consumer-apps www.dlp.com DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Mobile Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity